AMD Ryzen: взгляд изнутри

Характеристики процессоров AMD Ryzen и игровых станций на их основе позволяют осторожно предположить окончание непростого периода у «альтернативного» чипмейкера и претензии на лидерство. Не претендуя на истину в последней инстанции проанализируем некоторые детали — функциональные расширения базового набора x86-инструкций в семействе процессоров AMD Family 17h.

Список технологий и инструкций, поддержка которых реализована в AMD CPU семейства 17h. Фрагмент документа Software Optimization Guide for AMD Family 17h Processors.

Сложнейшие устройства, какими являются современные CPU, можно рассматривать с различных точек зрения, приходя к диаметрально противоположным выводам и результатам сравнения. Тем не менее, большинство технологий, рассмотренных ниже, ранее были реализованы в процессорах Intel, за исключением эксклюзивной для AMD инструкции CLZERO [1].

SMAP, Supervisor Mode Access Prevention

- Intel и AMD

Опция SMAP оказывает влияние на механизм трансляции страниц и подсистему виртуальной памяти. Позволяет блокировать доступ привилегированного кода операционной системы (Kernel Mode) к страницам уровня пользователя (User Mode).

Такое ограничение, несколько противоречащее классической иерархии защиты памяти (при которой статус супервизора допускает любые виды доступа) в некоторых случаях помогает противостоять действиям злонамеренного кода, несанкционированно использующего режим супервизора, а также упростить выявление некоторых ошибок, приводящих к искажению содержимого памяти.

RDSEED, Read Random Number (Re-Seed)

- Intel и AMD

Инструкция RDSEED, также как и ранее существующая инструкция RDRAND, генерирует случайное число. Отличие в том, что RDSEED для каждого сгенерированного числа использует аналоговый источник энтропии (Enhanced non-deterministic random bit generator, NRBG). RDRAND использует цифровой генератор (Deterministic random bit generator, DRBG), периодически перезагружаемый из аналогового источника энтропии. Такая перезагрузка называется re-seed. Недостаток инструкции RDRAND в том, что в паузах между такими перезагрузками может быть сгенерировано несколько случайных чисел, и в этом случае генерация каждого следующего числа в данной группе чисел является результатом работы цифрового автомата (DRBG), а не аналогового источника энтропии (NRBG), что теоретически снижает криптостойкость.

Данная официальная трактовка различий RDRAND и RDSEED приводится в документации Intel. Возможно, существуют некоторые Implementation-Specific различия у Intel и AMD. Упрощенно говоря, можно дать такую рекомендацию: если в приоритете производительность генератора случайных чисел, следует использовать инструкцию RDRAND, если криптографическая стойкость — RDSEED.

XSAVEC, Extended Save with Compaction

- Intel и AMD

Инструкция XSAVEC является одной из оптимизированных форм инструкции сохранения контекста XSAVE, применяемой для обеспечения работы многозадачных ОС. Инструкция XSAVEC в отличие от XSAVE не выполняет сохранение компонентов контекста процессора, состояние которых не изменялось с момента инициализации (init optimization).

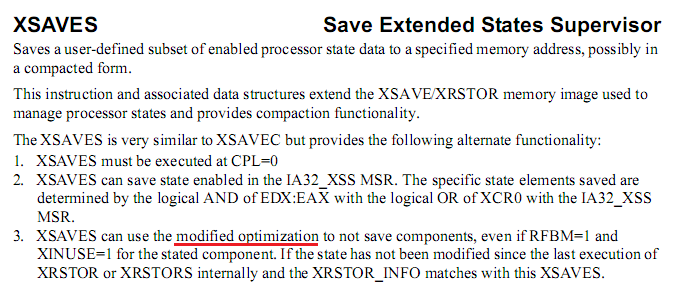

XSAVES, Extended Save for Supervisor

- Intel и AMD

Инструкция XSAVES является одной из оптимизированных форм инструкции сохранения контекста XSAVE, применяемой для обеспечения работы многозадачных ОС. Инструкция XSAVES в отличие от XSAVE не выполняет сохранение компонентов контекста процессора, состояние которых не изменялось с момента предшествующего восстановления их состояния (modified optimization). Данная форма оптимизации характерна для привилегированных процедур операционной системы.

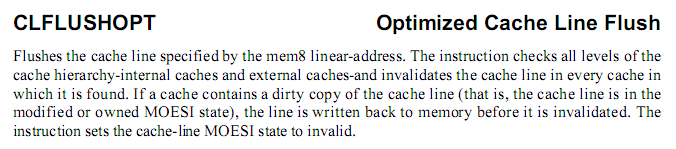

CLFLUSHOPT, Cache Line Flush Optimized

- Intel и AMD

Инструкция CLFLUSHOPT объявляет недостоверной строку кэш-памяти. Если перед выполнением инструкции, строка содержала данные, ожидающие отложенной записи в ОЗУ, такая запись выполняется перед очисткой строки. CLFLUSHOPT является оптимизированной версией ранее существующей инструкции CLFLUSH. К сожалению, четкая формализация списка различий между CLFLUSH и CLFLUSHOPT отсутствует в документации Intel и AMD.

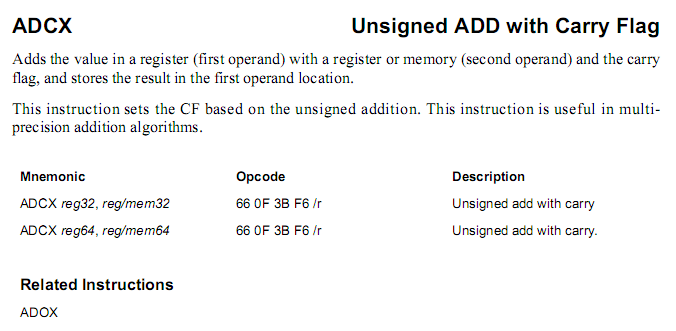

ADCX, Add with Carry Flag for Multi-Precision

- Intel и AMD

Инструкции ADCX и ADOX выполняют беззнаковое сложение двух операндов и предназначены для обработки чисел, разрядность которых превышает разрядность одной операции сложения за несколько таких операций. Признак арифметического переноса учитывается при сложении и устанавливается в соответствии с его результатами.

Имеют место следующие отличия от классической инструкции ADC, также выполняющей сложение с использованием флага переноса:

- Инструкция ADCX не модифицирует флаг переполнения OF.

- Инструкция ADOX в качестве признака арифметического переноса использует флаг переполнения (OF) и не модифицирует флаг переноса CF.

Описанный нетипичный формат использования флагов позволяет оптимизировать параллельное выполнение двух операций многоразрядного сложения, чередуя инструкции, относящиеся к двум ветвям. При использовании классической инструкции ADC, такое чередование инструкций взаимно-независимых ветвей в одном потоке было бы невозможно, в силу применения общего флага переноса (CF).

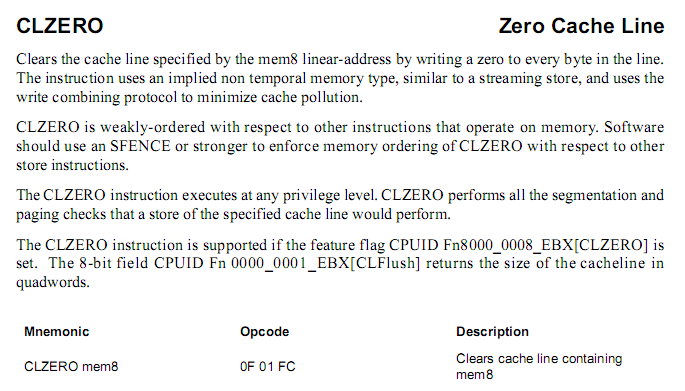

CLZERO, Cache Line Zero

- Только AMD

Инструкция CLZERO выполняет обнуление содержимого заданной строки кэш-памяти. Может использоваться для быстрого обнуления кэшируемых областей памяти а также исключения дополнительных пересылок между кэш-памятью и DRAM, имеющих место в случаях, когда содержимое кэш-строки модифицируется частично. Таким образом, оптимизируется взаимодействие Cache и DRAM.

Чтобы оценить эффект эксклюзивной для AMD инструкции CLZERO, потребуется основательно вспомнить теорию: информация, которую обрабатывает процессор, может быть классифицирована как temporal и non-temporal.

- К типу temporal можно отнести данные, которые процессор интенсивно и многократно использует в текущий момент времени, при этом их суммарный размер меньше размера кэш. Размещение таких данных в кэш повышает производительность, снимая необходимость доступа к ОЗУ.

- К типу non-temporal относятся данные, размещать которые в кэш бесполезно, а зачастую вредно. Если размер обрабатываемого блока превышает размер кэш, либо следующий доступ к данным планируется через продолжительное время, такие данные с высокой вероятностью будут вытеснены из кэш до следующего обращения к ним, а значит снова потребуется чтение ОЗУ. В таком примере, кэширование непроизводительно занимает такты CPU и объем кэш-памяти.

По умолчанию, большинство процессорных инструкций обращения к памяти работают в режиме temporal, для non-temporal доступа применяются специальные инструкции, например movntps [2] и/или movntpd [3].

С учетом сказанного, процессор по-разному выполняет операцию записи:

- Запись в режиме temporal store подразумевает предварительное заполнение строки кэш-памяти, для этого считывается и кэшируется 64-байтная область ОЗУ, которую затрагивает целевая операция записи. Собственно, обновление данных, предписанное инструкцией записи, выполняется уже в кэш-памяти.

- Запись в режиме non-temporal store (streaming store) подразумевает только запись в ОЗУ, без предварительного «спекулятивного» чтения, хотя и допускает объединение серии нескольких циклов записи малой разрядности в общий цикл суммарной разрядности (write combining).

Инструкция CLZERO, атомарно выполняющая полное обнуление кэш-строки, устраняет необходимость дополнительной загрузки информации из ОЗУ при формировании достоверного содержимого строки. Этим она отличается от типовых операций записи меньшей разрядности, модифицирующих кэш-строку частично. Кроме того, явно заданная размерность данных 64 байта или 512 бит упрощает write-combining оптимизацию.

Примечание.

Для удобства изложения, размер строки кэш-памяти принят равным 64 байта. Это типовое значение для современных процессоров Intel и AMD. В общем случае, программист должен детектировать значение этого параметра с помощью инструкции CPUID, избегая использования предопределенных констант.

Вместо послесловия

Анализируя рассмотренный список функциональных расширений, можно заключить, что в фокусе внимания разработчиков оказались защита пользовательских данных, сокращение затрат процессорных тактов на переключение контекста в многозадачной среде, оптимизация взаимодействия кэш-памяти и ОЗУ, а также базовые арифметические операции с целыми числами высокой разрядности.

Информация собиралась из разных источников, процесс уточнения и верификации не завершен на данный момент, поэтому замечания и дополнения приветствуются, особенно относительно инструкций CLFLUSHOPT и CLZERO и не нормируемых официальной документацией Implementation-Specific особенностей различных процессоров.

Автор: IC Book Labs

Источник [4]

Сайт-источник PVSM.RU: https://www.pvsm.ru

Путь до страницы источника: https://www.pvsm.ru/amd/265543

Ссылки в тексте:

[1] инструкции CLZERO: http://composter.com.ua/content/asus-rog-strix-gl702zc-v-poiskah-neochevidnogo-2017-10-01

[2] movntps: http://x86.renejeschke.de/html/file_module_x86_id_197.html

[3] movntpd: http://composter.com.ua/content/benchmarki-v-virtualnoy-realnosti-2014-11-24

[4] Источник: https://geektimes.ru/post/294325/

Нажмите здесь для печати.