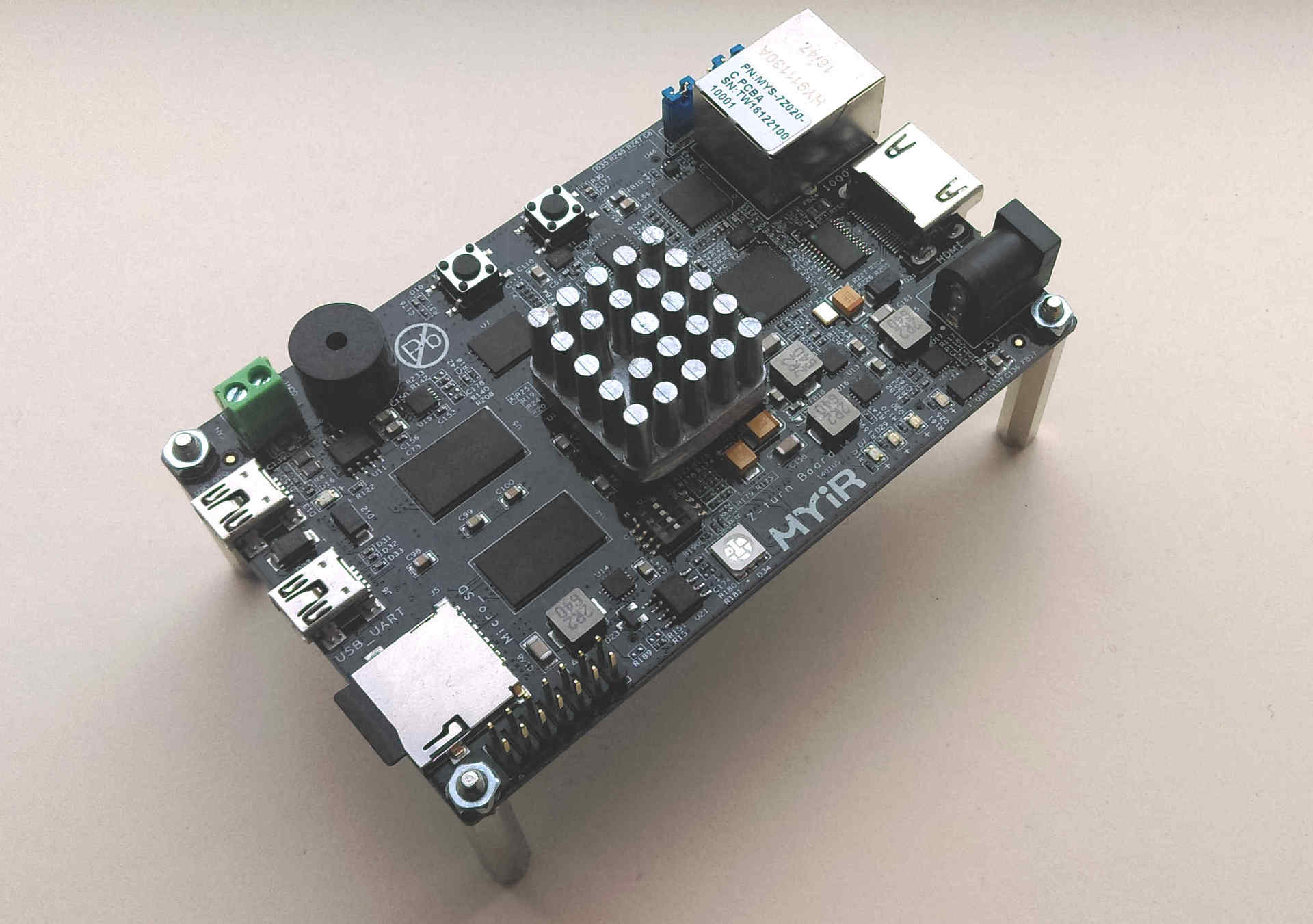

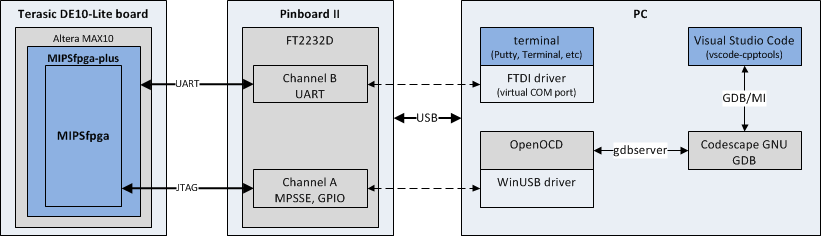

Здравствуйте! Мы одни из победителей хакатона MIPfpga, в этой статье расскажем, как подключать модули в систему на кристалле на основе MIPSfpga на примере клавиатуры Pmod KYPD. Также ознакомим с написанием программы для управления подключенных модулей.

→ Описание клавиатуры найдете здесь

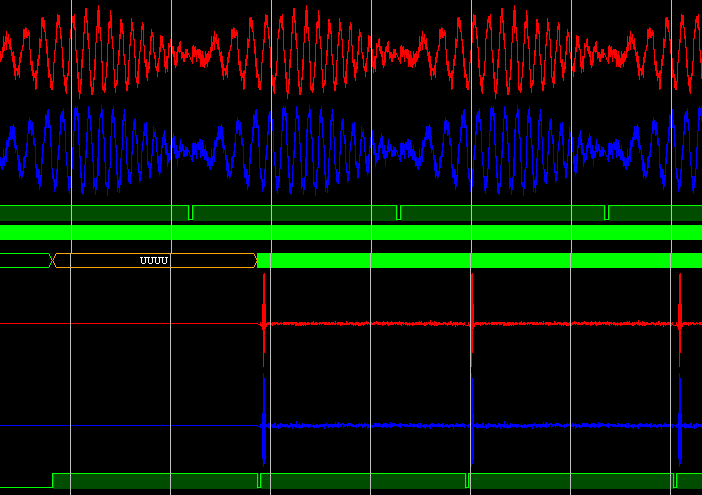

Pmod KYPD — 16-кнопочная клавиатура с цифрами в шестнадцатеричном формате (0-F). Опрос происходит способом поочередной подачи логического 0 на каждый столбец и считывания состояния строк. Если в момент опроса столбца одна из кнопок в нем нажата, соответствующая строка выдаст логическую 1.

Читать полностью »