Часть I

Часть II

Часть III

Часть IV

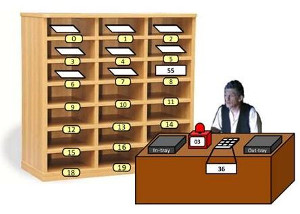

Эта статья посвящена созданию интерпретатора некого эзотерического языка LMCode, в основе которого лежит архитектура Little Man Computer. О Little Man Computer можно прочитать в предыдущих статьях.

- Пусть команде INP соответствует ,

- команде OUT соответствует .

- команде ADD соответствует +

- команде SUB соответствует —

- команде STA соответствует ~

- команде LDA соответствует ^

Напишем программу, которая загружает число из устройства ввода в аккумулятор, сохраняет число в памяти, прибавляет число из памяти к аккумулятору (удваивает число), и выводит удвоенное число в устройство вывода.

На ассемблере LMC эта программа будет выглядеть так (начальной ячейкой пусть будет 20)

INP

STA 20

ADD 20

OUT