Что есть жизнь? Это вечное стремление познавать не познанное. Я же познаю программирование ПЛИС (программируемая логическая интегральная схема). Просто поморгать светодиодом для меня не очень интересно и пришлось придумать задачу серьезнее. Так и родилась идея видеокарты (VGA) для микроконтроллера. Серьезным дядькам эта штука вряд ли пригодиться, а вот новичкам... Очень даже может быть. От того и было решено «заточить» видеокарту под Arduino NANO.

Основой проекта стала ПЛИС EPM240T100C5NЧитать полностью »

Рубрика «ПЛИС» - 2

VGA видеокарта для Arduino NANO

2021-10-07 в 16:00, admin, рубрики: arduino, arduino nano, fpga, VGA, видеокарта, Видеокарты, ПЛИС, Разработка под ArduinoПроектировщики RISC-V из Yadro покажут школьникам как проектировать процессоры

2021-09-07 в 5:50, admin, рубрики: asic, fpga, risc-v, syntacore, Verilog, обработка звука, обучение, параллельное программирование, ПЛИС, программирование микроконтроллеров, Процессоры, сколково, Электроника для начинающих

Через неделю будет выставка ChipEXPO, на которой для будет Читать полностью »

Практическое применение сервера с FPGA

2021-07-10 в 9:00, admin, рубрики: fpga, gpgpu, graphblas, opencl, Алгоритмы, Блог компании Selectel, математика, ПЛИС

В данной статье будет рассказано о попытке ускорить операции над разреженными булевыми матрицами, реализованные на OpenCL, с помощью замены целевой платформы GPGPU на FPGA.

Эта задача возникла при работе над библиотекой примитивов линейной алгебры, необходимых для решения некоторых задач анализа графов. Данные, структурированные в виде графов, играют огромную роль в современной жизни и встречаются в таких областях, как социальные сети, транспортные и коммуникационные сети, являются основой для набирающих популярность графовых баз данных.

Объем таких данных неуклонно растет и потому для получения хорошей производительности в задачах анализа графов все острее встает вопрос о разработке параллельных алгоритмов, что оказывается нетривиальной задачей из-за нерегулярности данных.

Читать полностью »

Новостной дайджест событий из мира FPGA-ПЛИС — №005 (2020_09)

2020-10-07 в 5:17, admin, рубрики: Achronix, fpga, intel, Lattice, xilinx, ПЛИСЗдравствуйте, друзья.

Возвращаемся к публикации последних событий из мира FPGA/ПЛИС. Ниже приведены несколько ссылок на новости, анонсы, вебинары, воркшопы, туториалы, видео и тд. Подобные новостные дайджесты есть, например, на хабе про php, почему бы и не сделать что-то подобное и для ПЛИС?

Подробности в конце статьи :)Читать полностью »

Генерация клока в ПЛИС на примитивах

2020-07-05 в 10:17, admin, рубрики: fpga, Verilog, генерация тактового сигнала, ненормальное программирование, ПЛИСЧитая даташиты на ПЛИС, можно находить таблички об их рабочих частотах…

Хотя нет, история начинается еще с 2015 года, когда я познакомился с ПЛИС. В своих первых простеньких работах я формировал нужный мне клок из счетчика и запитывал от него всю логику(естественно при условии что клок мне нужен медленнее чем подавался на ПЛИС, например UART и SPI). Естественно за такое меня гоняли, но у меня была простая отмазка «но ведь работает же!», и действительно все работало. С тех пор у меня в голове закралась мысль «а откуда вообще можно взять тактирующий сигнал?».

Вариантов источников взять клок не много. Либо взять из некого ClockWizard основанный на PLL или MMCM, либо сформировать из счетчика, либо сразу с ножки так сказать single ended. А что, если взять тактовый сигнал сформированный примитивом ПЛИС?

Читать полностью »

PCI Express в ПЛИС V-й серии Intel: основы интерфейса и особенности аппаратных ядер

2020-04-11 в 10:10, admin, рубрики: fpga, pcie, ПЛИС, программирование микроконтроллеровВведение

Знакомый многим интерфейс PCI Express или PCIe был доступен разработчикам систем на ПЛИС уже тогда, когда он только начинал распространяться в цифровой технике. В это время существовало решение, в котором программное ядро подключалось ко внешней микросхеме физического уровня [5]. Это позволяло создавать одноканальную линию PCIe со скоростью 2,5 гигатранзакций в секунду. В дальнейшем, благодаря развитию технологий, физический уровень интерфейса перекочевал в аппаратные блоки PCIe внутри самих ПЛИС; количество возможных каналов увеличилось до 8, а в ряде новых микросхем — и до 16; вслед за современными стандартами выросли возможные скорости передачи данных.

В то же время, в русскоязычных источниках по-прежнему затруднительно найти вспомогательные материалы по работе с аппаратными ядрами современных ПЛИС, не так и много информации доступно по самому интерфейсу PCIe. Руководство к аппаратным ядрам PCI Express подразумевает, что разработчик уже ознакомился со стандартом и понимает основы передачи данных между устройством и персональным компьютером (ПК). Однако обилие информации в самом стандарте PCIe не дает сразу же разобраться в том, какие шаги необходимо предпринять, чтобы успешно передать данные от устройства в память ПК или обратно. Чтобы получить более полную картину, немалую часть сведений приходится собирать по крупицам из разных источников. Для разработчиков систем на ПЛИС фирмы Intel сложность также заключается в том, что большинство доступных материалов и статей описывают работу с аппаратными ядрами ПЛИС фирмы Xilinx.

В данной статье автор постарается рассказать о том, что необходимо знать разработчику систем на ПЛИС для работы с интерфейсом PCI Express; рассмотрит особенности работы с аппаратными ядрами PCI Express ПЛИС V-й серии фирмы Intel в варианте Avalon-ST.

Читать полностью »

Собственный софт-процессор на ПЛИС с компилятором языка высокого уровня или Песнь о МышЕ

2020-03-09 в 12:54, admin, рубрики: forth, fpga, python, Компиляторы, ПЛИС, софт-процессорСобственный софт-процессор на ПЛИС с компилятором языка высокого уровня или Песнь о МышЕ — опыт адаптации компилятора языка высокого уровня к стековому процессорному ядру.

Распространенной проблемой для софт-процессоров является отсутствие средств разработки для них, особенно, если их система команд не является подмножеством команд одного их популярных процессорных ядер. Разработчики в этом случае вынуждены будут решать эту проблему. Прямым её решением является создание компилятора языка ассемблера. Однако в современных реалиях не всегда удобно работать на Ассемблере, так как в процессе развития проекта может изменяться система команд в связи, например, с изменившимися требованиями. Поэтому задача легкой реализации компилятора языка высокого уровня (ЯВУ) для софт-процессора является актуальной.

Компилятор языка Python — Uzh представляется легким и удобным инструментарием для разработки программного обеспечения для софт-процессоров. Инструментарий определения примитивов и макросов как функций целевого языка позволяет критичные места реализовывать на ассемблере процессора. В данной работе рассмотрены основные моменты адаптации компилятора для процессоров стековой архитектуры.

Читать полностью »

Аннотация

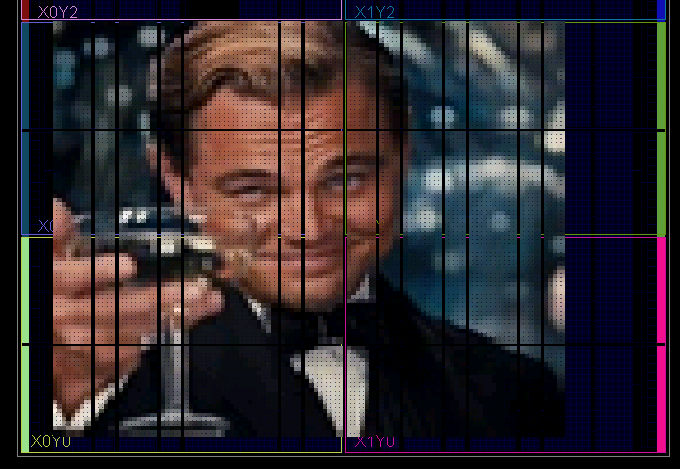

Безумию все возрасты покорны

При проектировании каких-либо модулей на ПЛИС невольно иногда приходит в голову мысль о не совсем стандартном использовании самой среды проектирования и инструментов, которые она предоставляет для проектирования. В этой небольшой заметке мы рассмотрим, как с помощью инструмента управления средой, реализованного на Tcl, мы можем буквально рисовать на ПЛИС фотографии, картины, портреты и мемасики.

Такой необычный «маршрут проектирования» был реализован еще полтора года тому назад, но вот только сейчас пришла мысль оформить его в виде заметки, в которой имеется небольшая практика применения Tcl скриптов для управления средой проектирования, в данном случае Vivado. Однако при небольших доработках все легко может быть адаптировано под другие среды разработки, например Quartus II.

Первые опыты использования потокового протокола на примере связи ЦП и процессора в ПЛИС комплекса REDD

2019-08-07 в 12:00, admin, рубрики: fpga, Redd, Компьютерное железо, ПЛИС, потоковый протокол, программирование микроконтроллеров, системное программирование, шина

В предыдущих статьях мы уже познакомились с шиной Avalon-MM, где MM означает Memory Mapped, то есть проецируемая на память. Эта шина вполне себе универсальная. К ней может быть подключено несколько ведущих (Master) и несколько ведомых (Slave) устройств. Мы уже подключали сразу два ведущих устройства (Instruction Master и Data Master), потому что у процессора NIOS II гарвардская архитектура, так что шины команд и данных у него разные, но многие авторы для упрощения разработки ПО снаружи подключают их к одной и той же общей шине.

Если какой-то блок на шине имеет функциональность прямого доступа к памяти (DMA), то он также будет содержать ведущее устройство для шины.

Собственно, на этом факте (много ведущих, много ведомых) и основано главное неудобство данной шины. Когда мы проектировали своё ведомое устройство, нам приходилось декодировать адрес. Когда же мне доводилось делать своего ведущего, возни с арбитражем было существенно больше. А ведь красной нитью через весь цикл статей идёт утверждение, что разработка под Redd — вспомогательная часть проекта, она не должна требовать слишком много трудозатрат. И если можно освободиться от рутины, мы должны от неё освободиться.

Читать полностью »

Разработка программ для центрального процессора Redd на примере доступа к ПЛИС

2019-07-04 в 8:46, admin, рубрики: fpga, Компьютерное железо, микроконтроллеры, ПЛИС, программирование микроконтроллеров, системное программированиеВ прошлой статье я сказал, что нам пора переходить к потоковым протоколам. Но начав подготовку рассказа о них, я понял, что сам плаваю в одной очень важной теме. Как уже отмечалось, у меня с Линуксом достаточно своеобразные отношения. В общем, я понял, что сам не могу создать с нуля приложение на С++, которое удовлетворяло бы всем принципам программирования для Redd. Можно было бы попросить кого-то сделать это, а затем просто воспользоваться готовым шаблоном, но цикл статей призван научить всех вести разработку под Redd с нуля. Поэтому я попросил своего начальника (большого специалиста по Линуксу), и он разъяснил мне, что за чем нажимать. Затем я чуть переосмыслил его слова и теперь считаю нужным зафиксировать все знания письменно. Это избавит таких, как я, от мучительных раздумий: «Так… Что он сделал – понятно, но как мне это повторить?». В общем, кто работает под Линуксом, можете пробежать следующие два раздела по диагонали. Вряд ли вы найдёте там что-то новое (дальше – найдёте). А остальным я предлагаю на выбор две методики разработки, которые соответствуют декларируемым принципам работы под Redd: низкие трудозатраты на разработку и удалённая отладка.