Сейчас выходит русский перевод японской манги 2013 года про цифровые схемы, созданной Амано Хидэхару и Мэгуро Кодзи. Несмотря на несерьезную форму изложения, суть этой книжки очень здравая. Например, она начинает от древних микросхем малой степени интеграции и быстро привязывает их к современному языку описания аппаратуры Verilog и программируемым логическим интегральным схемам (ПЛИС). Также манга четко определяет зачем нужны комбинационные и последовательностные схемы, и дает представление о методах оптимизации.

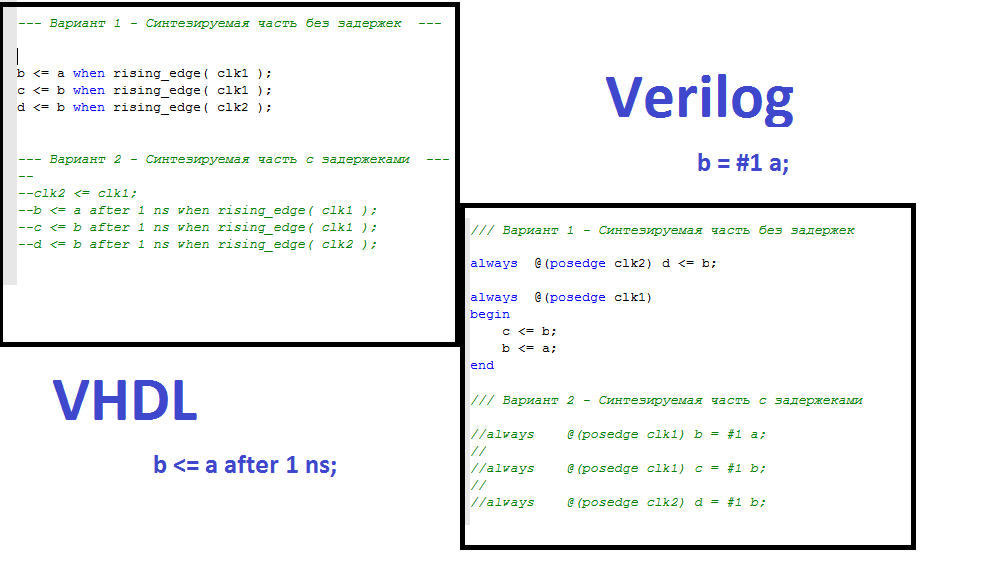

Манга избегает ошибок многих своих предшественников. Одну из таких ошибок совершил Чарльз Петцольд в книге «Код», которая вводила последовательностную логику не на D-триггерах, управляемых фронтом тактового сигнала (edge-triggered D-flip-flop), а на D-триггерах с работой по уровню (защелках, level-sensitive D-latch), хотя потом переключалась на правильные триггеры. Вероятно, ошибка была связана с тем, что Чарльз Петзольд, который прославился как автор учебников по программированию GUI в Microsoft Windows, не был практикующим разработчиком электроники, и для него защелки были «проще», чем триггеры с фронтом. Проблема в том, что защелки плохо совместимы со статическим анализом задержек при логическом синтезе, главной технологии проектирования цифровых схем последних 30 лет. Системы на кристалле внутри гаджетов типа айфона в качестве элементов состояния в 99% случаях используют D-триггеры переключаемые по фронту, а защелки используют только в очень специальных случаях. Давать новичкам строить схемы на защелках — это значит вводить их в заблуждение.

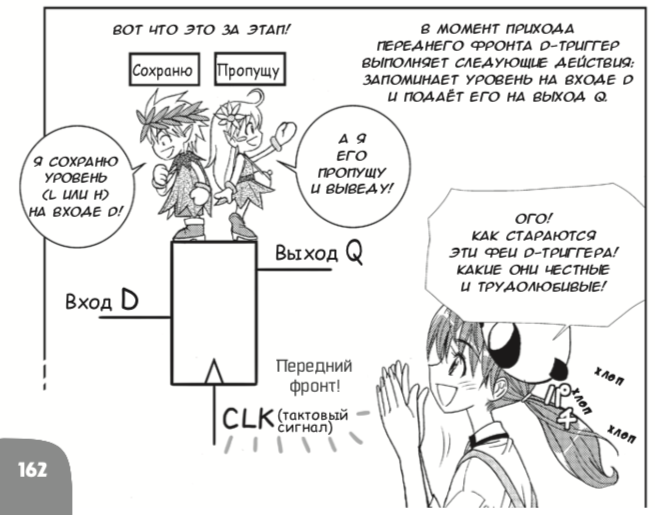

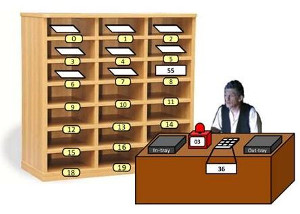

В этом смысле манга лучше чем Петзольд. Вот как элегантно манга объясняет работу двухступенчатого master slave D-триггера, управляемого фронтом тактового сигнала. Это делается с помощью феи «Хи-хи-хи» и феи «Ха-ха-ха»: