Система настройки и ввода ограничений (Constraint manager) в PADS Professional/Xpedition предоставляет пользователям полный контроль над всеми параметрами, которые влияют на целостность высокоскоростных сигналов. Сегодня мы разберем как можно включить в расчет общей длины проводника влияние длины и задержки (Pin Package Length and Delays) выводов микросхемы, а также влияние фактора переходных отверстий (ПО).

Все самое интересное под катом.

В данной статье я попытаюсь ответить на следующий вопросы:

- Фактор длины ПО

- Можно ли одновременно вводить ограничения по длине и задержке для выводов в Constraint Manager?

- Каково влияние задержек и длин для выводов на вкладке «Part» в CES?

- Как работает инструмент «Tuning meter» при использовании параметров длины выводов и фактора длины ПО?

- Влияние задержки в ПО на расчет общей задержки сигнала

Настройка задержки выводов в Constraint Manager

В PADS Professional/Xpedition версии VX2.2 и выше появилась возможность одновременного импорта файла с задержками и длинами выводов прямо в систему ввода ограничений.

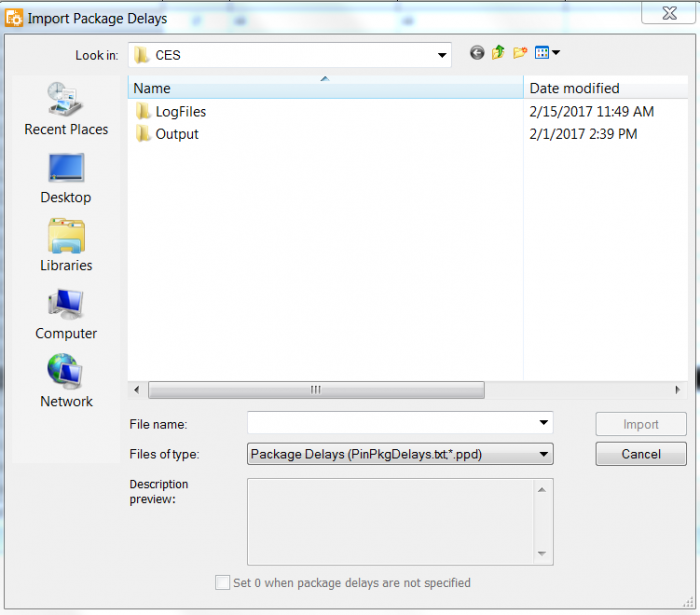

Для того, чтобы выполнить импорт откройте CES, перейдите в меню File > Import > Package Delays и выберите ваш файл с задержками:

Автоматический расчет значений задержек

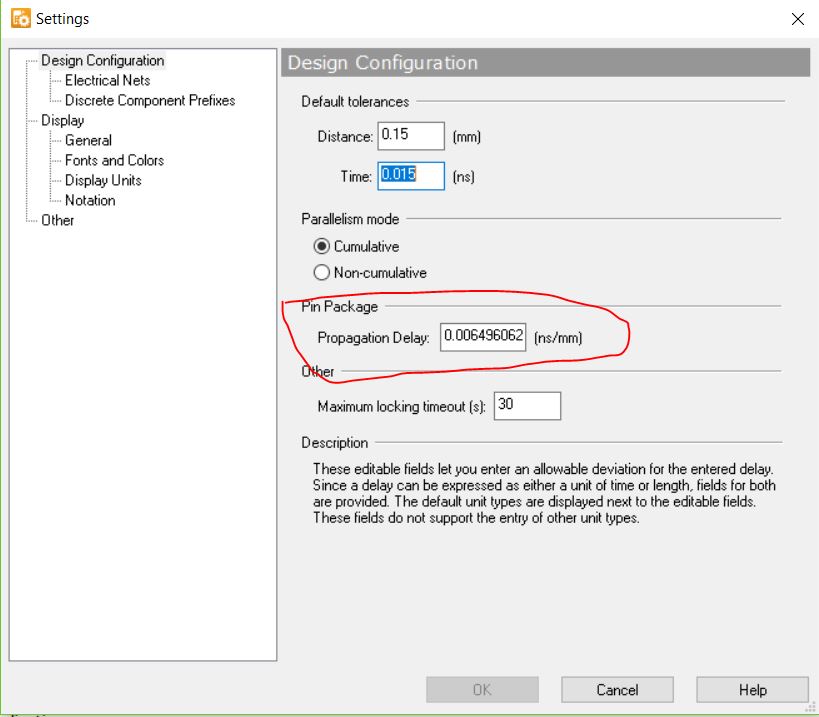

Если у вас имеется информация только о длине выводов микросхемы, то вы можете использовать CES для автоматического расчета значения задержки выводов, на основе задержки распространения сигнала, определенной в настройках CES (Setup > Settings):

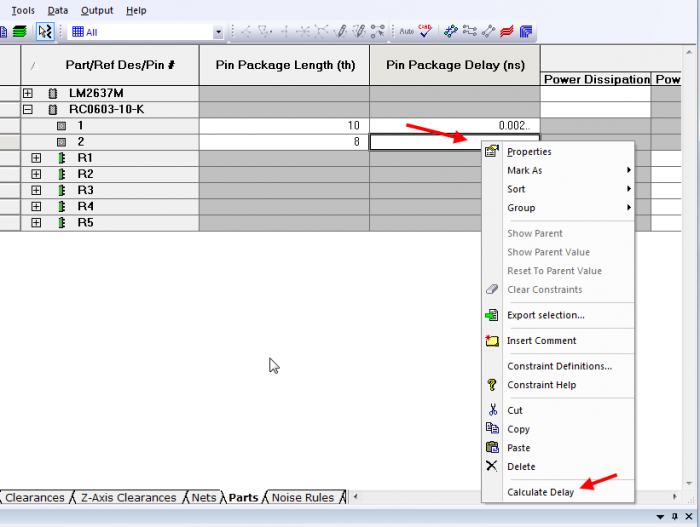

После того, как вы задали значения длины выводов, щелкните правой кнопкой мыши в ячейке соответствующей задержке контакта и выберите Calculate Delay и система автоматически рассчитает значение:

Ниже будут приведены примеры для различных случаев использования Via Lengths, Via Delay и Pin Package Lengths.

Пример №1

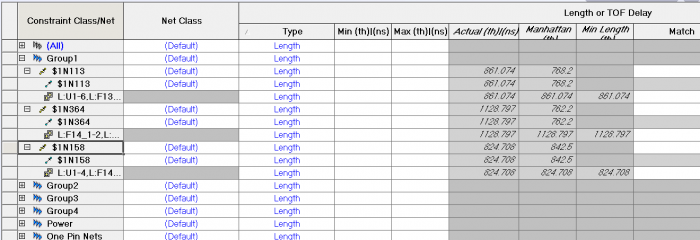

В данном примере не используются параметры Via или Pin Package Length:

Добавление длины 100th к каждому выводу компонента U1 дает следующие значения:

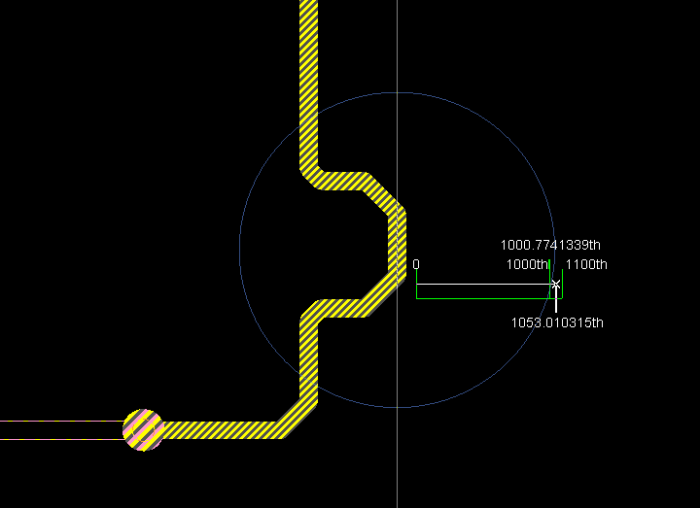

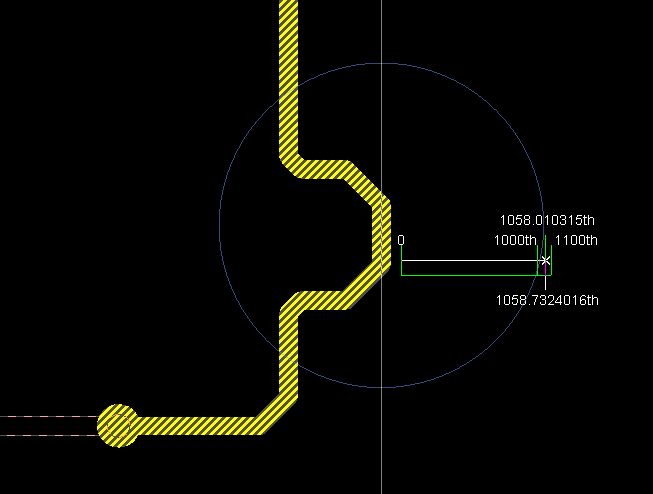

Tuning Meter теперь отображает значения длины проводника, с учетом добавленных 100th к каждому выводу компонента:

Пример №2

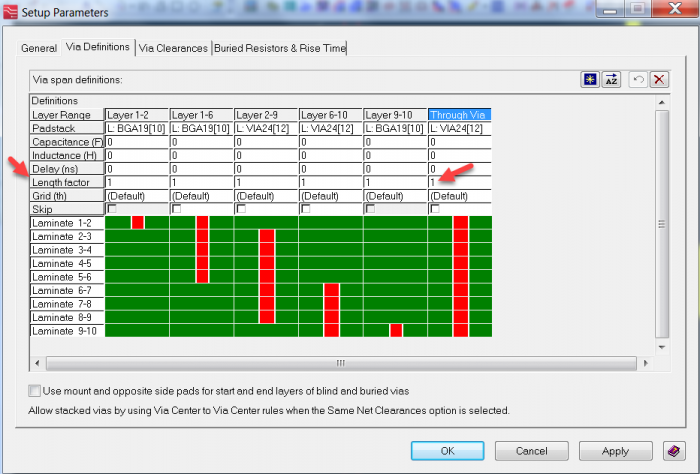

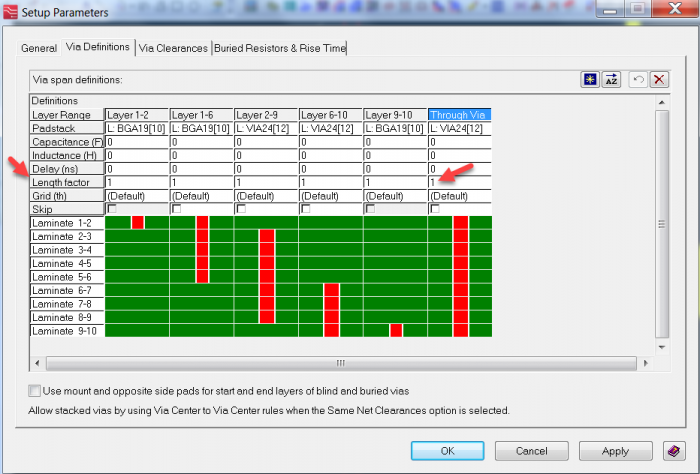

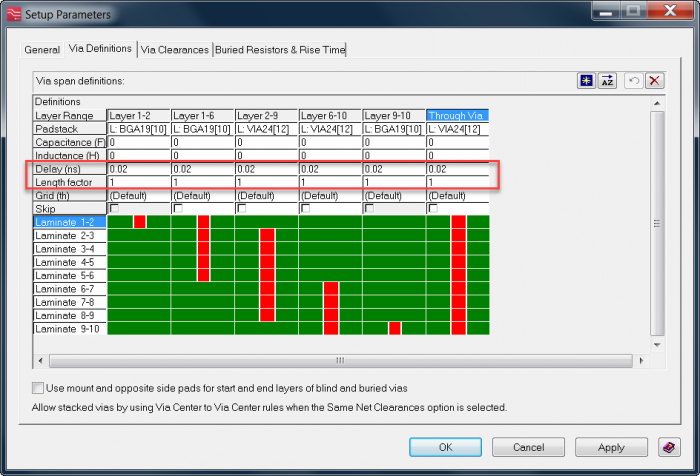

Теперь переходим в меню Setup >Setup Parameters и на вкладке Via Defenitions задаем значение Via Length Factor равное 1.

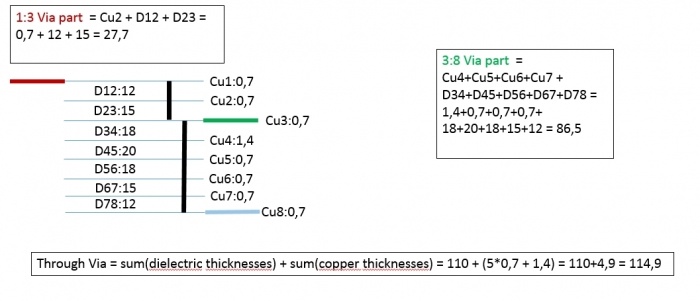

Примечание: значение длины ПО рассчитывается на основе вашего стэка платы. Также Обратите внимание, что для расчета длины ПО толщина меди начального и конечного слоев НЕ учитывается. На рисунке ниже показано как происходит расчет длины ПО сигнала, переходящего со слоя 1 на слой 3 и со слоя 3 на слой 8:

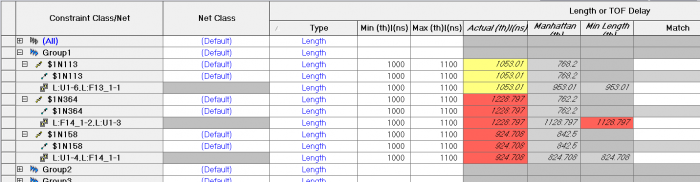

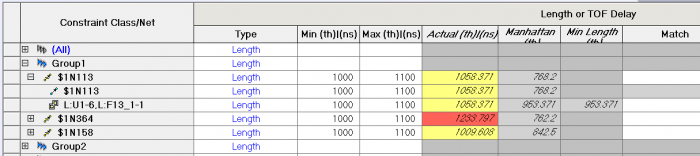

Фактическая длина проводника в менеджере ограничений изменится, как только мы зададим коэффициент длины ПО:

Теперь длина проводника, отображаемая в Tuning Meter, включает в себя коэффициент длины ПО и длину выводов:

Пример №3

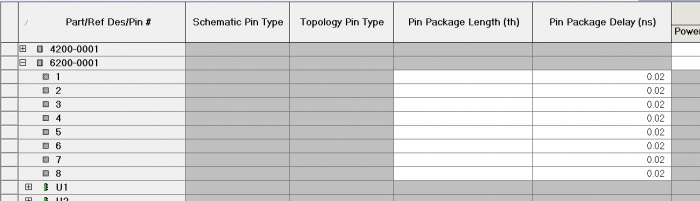

На этом этапе мы добавим задержку Pin Package Delay 0,02 нс:

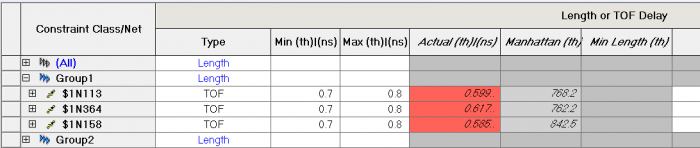

Давайте для наглядности посмотрим значения задержки, рассчитанное для проводника в режиме TOF, при условии, что Pin Package Delay установлен в значение 0:

Теперь зададим для Pin Package Delay значение в 0.02 нс:

Задержка в менеджере ограничений для данного сигнала изменилась на 0.02 и мы в этом можем убедиться:

Пример №4

Теперь давайте рассмотрим случай, когда одновременно установлены Pin Package Delay и Pin Package Length а также Via Delay и Via Length Factor и как это повлияет на расчет общей длины/задержки проводника.

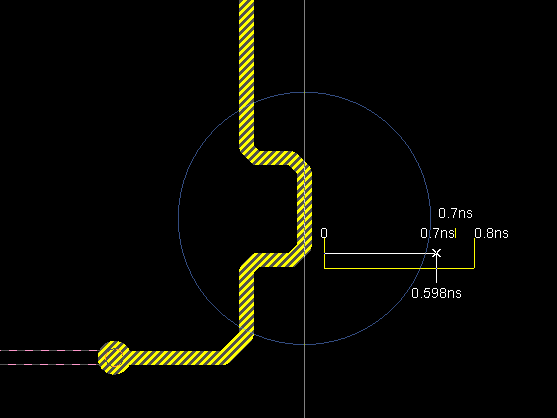

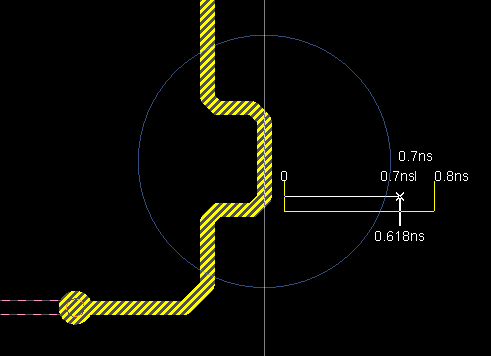

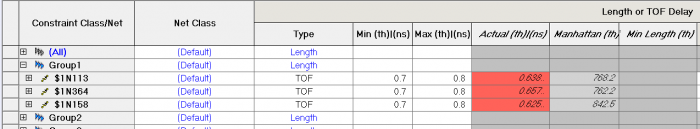

На рисунке ниже показана задержка распространения сигнала в проводнике при нулевых значениях Pin Package Delay и Via Delay в инструменте Tuning Meter:

Следующим шагом устанавливаем Pin Package Delay в 0.02 нс и смотрим изменения:

Теперь, если мы зададим еще значение в поле Pin Package Length или Via Lenght Factor, то значение задержки никак не изменится, так как мы работаем в режиме TOF.

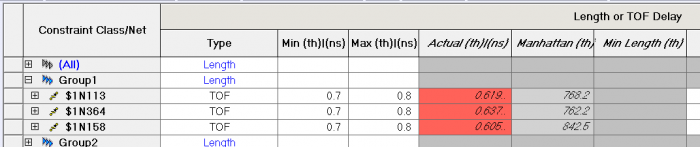

Но если мы установим Pin Package Delay и Via Delay в значение 0.02 нс, то мы получим следующий результат:

В редакторе ограничений задержка распространения сигнала по проводнику, с установленными параметрами Pin Package Delay и Via Delay со значением 0.02 нс будет выглядеть следующим образом:

Via Delay и Via Length Factor можно настроить через меню Setup > Setup Parameters на вкладке Via Defenitions:

Заключение

Система ввода ограничений PADS Professional/Xpedition позволяет задавать одновременно и длину выводов и значения задержки, НО если у вас в CES задан вариант расчета по времени распространения сигнала (TOF), то система будет использовать значения из ячейки Pin Package Delay, а если вариант расчета по длине (Length) — система будет брать значения из ячейки Pin Package Lengths.

Тоже самое касается и влияние ПО. Если тип задержки, определенный в менеджере ограничений задан как Length, то будет использоваться коэффициент длины (Via Length Factor) ПО, в случае TOF будет использоваться значение Via Delay.

Надеюсь, что вышло не слишком громоздко и запутанно.

Все непонятные моменты готов обсуждать в комментариях.

Филипов Богдан PBO, Product-manager по решениям PADS

Автор: pbo