Процессоры Intel Xeon оснастили FPGA Altera

Intel начинает поставки двухчиповой платформы для разработки, состоящей из процессора Xeon E5-2600 v4 (Broadwell) и FPGA Altera Arria 10 [1] — такую информацию озвучила вице-президент Intel Diane Bryant в своей речи на конференции IDF 2016 в Китае [2]. Предполагается, что с помощью подобного гибрида удастся получить 70% прирост производительности при том же энергопотреблении и частоте. Плоды сотрудничества Intel и Altera, которое продолжается далеко не первый год, мы уже видели в лице прототипа платформы 5G [3] — там скрещивались FPGA и Intel Core. И вот теперь — новый дуэт. В планах на будущее — полная интеграция обоих компонентов на одном кристалле. Первыми потребителями гибрида станут крупнейшие облачные сервисы и дата-центры. По прогнозам Intel, к 2020 году до 30% серверов в дата-центрах будут иметь процессоры с FPGA.

Intel начинает поставки двухчиповой платформы для разработки, состоящей из процессора Xeon E5-2600 v4 (Broadwell) и FPGA Altera Arria 10 [1] — такую информацию озвучила вице-президент Intel Diane Bryant в своей речи на конференции IDF 2016 в Китае [2]. Предполагается, что с помощью подобного гибрида удастся получить 70% прирост производительности при том же энергопотреблении и частоте. Плоды сотрудничества Intel и Altera, которое продолжается далеко не первый год, мы уже видели в лице прототипа платформы 5G [3] — там скрещивались FPGA и Intel Core. И вот теперь — новый дуэт. В планах на будущее — полная интеграция обоих компонентов на одном кристалле. Первыми потребителями гибрида станут крупнейшие облачные сервисы и дата-центры. По прогнозам Intel, к 2020 году до 30% серверов в дата-центрах будут иметь процессоры с FPGA.

Тут уместно упомянуть, что в прошлом году стартовал совместный проект компаний Intel и eASIC [4] по созданию платформы Xeon + ASIC для кастомизации процессоров под конкретные предварительно оговоренные нагрузки. Воистину, больше Xeon'ов, хороших и разных!

Под катом — немного информации о FPGA Altera Arria 10.

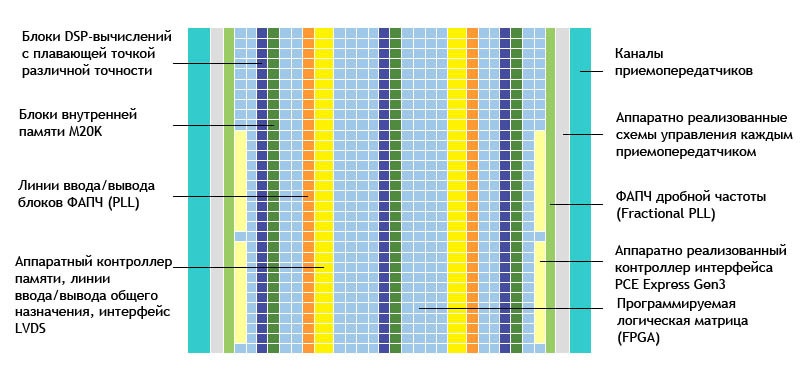

Устройство FPGA семейства Arria 10

Новые ПЛИС FPGA семейства Arria 10 выполнены по технологическим нормам 20 нм. Устройства семейства Arria 10 отличаются на 40% меньшим энергопотреблением, чем ПЛИС FPGA предыдущего поколения, и являются единственными в отрасли программируемыми логическими схемами с аппаратно реализованными блоками цифровой обработки сигналов с плавающей точкой с производительностью 1500 GFLOPS (млрд. операций с плавающей точкой).

- Пропускная способность интегрированных приемопередатчиков до 28.3 Гбит/с

- Высокопроизводительный интерфейс внешней памяти с пропускной способностью 2666 Мбит/с

- Аппаратные блоки DSP-вычислений с плавающей точкой, соответствующие требованиям спецификации IEEE 754

- До 96 каналов приемопередатчиков обеспечивают тракт последовательной передачи данных с пропускной способностью до 3.6 Тбит/с

Программное использование возможностей FPGA будет осуществляться посредством Altera OpenCL SDK [5]

Автор: Intel

Источник [6]

Сайт-источник PVSM.RU: https://www.pvsm.ru

Путь до страницы источника: https://www.pvsm.ru/fpga/119353

Ссылки в тексте:

[1] Altera Arria 10: https://www.altera.com/products/fpga/arria-series/arria-10/overview.html

[2] конференции IDF 2016 в Китае: http://www.intel.com/content/www/us/en/intel-developer-forum-idf/shenzhen/2016/idf-2016-shenzhen.html

[3] прототипа платформы 5G: https://habrahabr.ru/company/intel/blog/278201/

[4] eASIC: http://www.easic.com/

[5] Altera OpenCL SDK: https://www.altera.com/products/design-software/embedded-software-developers/opencl/overview.html

[6] Источник: https://habrahabr.ru/post/282570/?utm_source=habrahabr&utm_medium=rss&utm_campaign=best

Нажмите здесь для печати.