Современные ПЛИС содержат мультигигабитные линия связи и существует большое количество протоколов для обмена. Однако при ближайшем рассмотрении применять стандартные протоколы в ПЛИС не всегда удобно. Например, для ПЛИС Xilinx доступны реализации PCI Express, RapidIO, Aurora; у каждого из них есть недостатки. PCI Express и RapidIO работают с кодировкой 8/10 что сразу ограничивает пропускную способность. Aurora может работать с кодировкой 64/66, но не обеспечивает восстановление данных после сбоя. С учётом недостатков стандартных протоколов и особенностей применения я решил реализовать свой протокол обмена. Название PROTEQ досталось по наследству от предыдущего проекта, для которого была высказана похожая идея восстановления данных после сбоя.

Читать полностью »

Метка «fpga»

PROTEQ — протокол обмена по мультигигабитными линиям для ПЛИС Xilinx

2014-12-06 в 22:58, admin, рубрики: Песочница, метки: fpgaIntel собирается выпустить серверные процессоры Xeon со встроенной FPGA

2014-06-21 в 8:11, admin, рубрики: fpga, gpgpu, intel xeon, высокая производительность, Железо, Процессоры, метки: fpga, gpgpu, intel xeon

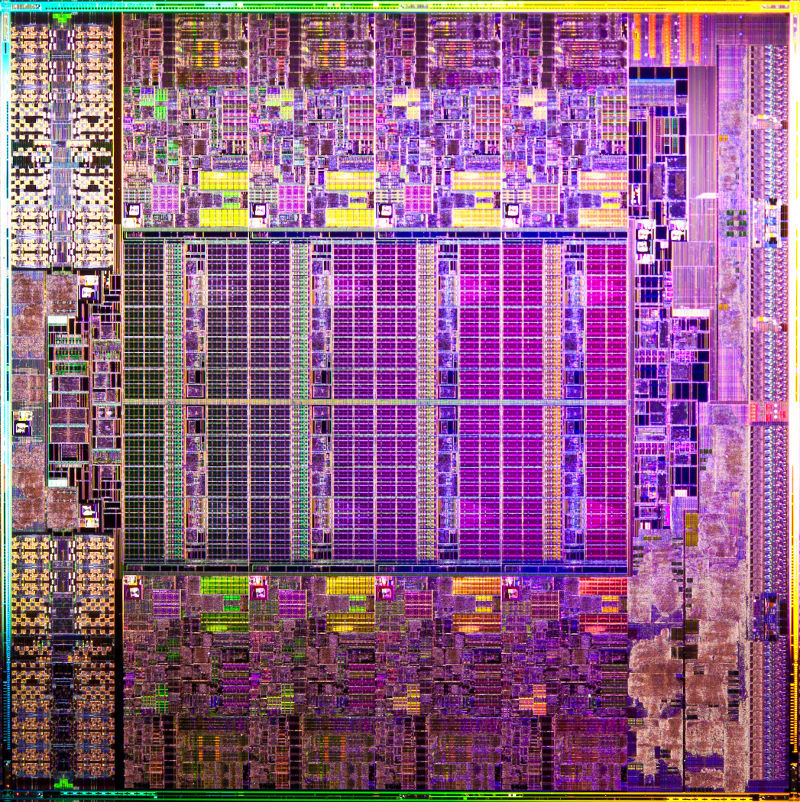

Восьмиядерный процессор Xeon

Корпорация Intel планирует включить в состав своих чипов Xeon программируемую пользователем вентильную матрицу (FPGA). FPGA позволяет пользователю переконфигурировать логику работы интегральной схемы, оптимизировав её под решение конкретной задачи. Это позволяет ускорить некоторые вычисления на порядок, или намного снизить энергопотребление. Другими словами, это позволит каждому пользователю создавать на кристалле Xeon собственный сопроцессор, заточенный под конкретные задачи.

Читать полностью »

Quaternion Encryption Scheme (QES) на FPGA, XeonPhi, GPU

2014-06-19 в 8:17, admin, рубрики: c++, fpga, nvidia tesla, opencl, Алгоритмы, высокая производительность, ПЛИС, сопроцессор, шифрование, метки: fpga, nvidia tesla, opencl, ПЛИС, сопроцессор, шифрование -na-FPGA-XeonPhi-GPU.jpg)

Привет!

Шифрование данных с помощью кватернионов выполнялось на FPGA DE5-NET, XeonPhi 7120P, GPU Tesla k20.

У всех троих приблизительно одинаковая пиковая производительность, но имеется разница в энергопотреблении.

Дабы не нагромождать статью лишней информацией предлагаю вам ознакомиться с краткой информацией о том что такое кватернион и матрица поворота в соответствующих статьях википедии.

Каким же образом можно зашифровать и расшифровать данные с помощью кватернионов? Довольно просто!

Для начала возьмем кватернион: q = w + x*i + y*j + z*k и составим на его основе матрицу поворота, которую назовем, например P(q).

Прим. картинка ниже из википедии и матрица там названа Q.

Microsoft переходит на процессоры собственной разработки

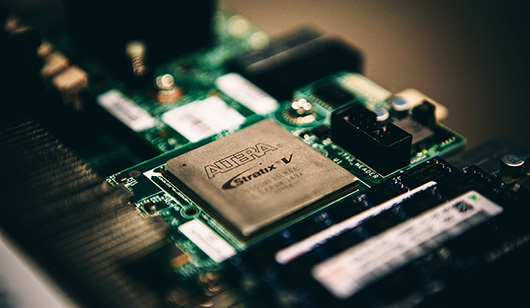

2014-06-18 в 12:12, admin, рубрики: Bing, fpga, microsoft, xeon, высокая производительность, Процессоры, метки: Bing, fpga, microsoft, xeon Союз между компаниями Microsoft и Intel всегда задавал стандарты для всей компьютерной индустрии, однако времена потихоньку начинают меняться. В Microsoft не очень довольны темпами развития современных серверных процессоров, и потому решили начать экспериментировать с чипами FPGA, в целях добиться более высокой производительности в обслуживании своей поисковой системы Bing.

Производителем FPGA чипов выступает компания Altera, пионер в области программируемых чипов. В пилотном тестировании было задействовано 1632 сервера, каждый из которых был оснащён классическим x86-процессором Intel Xeon и платой с чипом FPGA. Платы были объединены в единую машинную поисковую сеть под названием Catapult, через которую шли запросы с сайта Bing в обход процессоров Xeon.

Читать полностью »

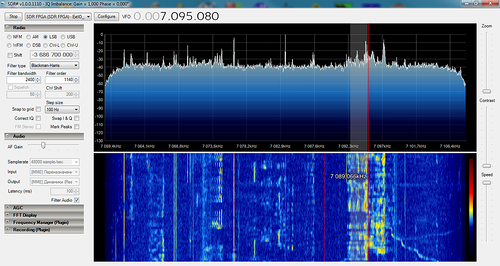

Простой SDR приёмник на ПЛИС

2013-12-01 в 20:11, admin, рубрики: diy или сделай сам, fpga, SDR, ПЛИС, радиосвязь, Электроника для начинающих, метки: fpga, SDR, ПЛИС В этой статье я расскажу о том, как на базе отладочной платы DE0-nano сделать достаточно простой КВ SDR приёмник.

Пример принимаемых сигналов:

Читать полностью »

Коротенькое сравнение VHDL и Verilog в помощь начинающим знакомство с ПЛИС

2013-11-06 в 7:48, admin, рубрики: fpga, SystemVerilog, Verilog, vhdl, ПЛИС, Электроника для начинающих, метки: fpga, SystemVerilog, Verilog, vhdl, ПЛИС Исторически так сложилось что ПЛИС я начал изучать только на новой работе.

Это были серии ПЛИС фирмы Altera.

Старшие коллеги на перебой рекомендовали как AHDL так и VHDL для программирования этих микросхем.

В итоге я остановился на языке VHDL, поскольку он является языком высокого уровня, в отличии от ADHL.

Хоть и листинг у последнего был куда приятнее.

И я приступил к изучению всех хитростей и ограничений языка VHDL.

В итоге сошелся на мысли что конструкции языка просто ужасны, а ограничения избыточны для проектирования аппаратуры.

Приведу пример листинга из статьи Делаем таймер или первый проект на ПЛИС

Читать полностью »

Описание блоков памяти на языке VHDL

2013-10-16 в 9:53, admin, рубрики: fpga, vhdl, ПЛИС, Электроника для начинающих, метки: fpga, vhdl, ПЛИС В данной статье показаны основные принципы описания модулей ПЗУ и ОЗУ на языке VHDL. Статья ориентирована на начинающих. Ее цель — дать общее понятие об описании модулей памяти на языке VHDL. Примеры и иллюстрации предены для пакета Quartus II v. 9.1. Предполагается, что читатель знает как создавать проект в пакете Quartus II, проводить его компиляцию и симуляцию.

Читать полностью »

Прямая передача данных между ПЛИС Virtex-7 по шине PCI Express

2013-09-13 в 11:08, admin, рубрики: fpga, pcie, высокая производительность, Железо, ПЛИС, метки: fpga, pcie, ПЛИСАннотация

В данной статье рассматривается передача данных по шине PCI Express с одновременным участием нескольких ПЛИС. В компьютерной системе, к PCI Express шине которой подключено несколько (в нашем случае 8) оконечных устройств (PCIe endpoints) ПЛИС запускается одновременно несколько транзакций передачи данных двух типов: А) DMA передача между ОЗУ и ПЛИС (чтение/запись) и Б) прямая передача данных между двумя ПЛИС (запись). Используя соединение PCI Express x4 Gen 2.0 при обращении в память была получена скорость записи 1451 МБ/с (90% от максимальной). Скорость записи данных между ПЛИС была равна 1603 МБ/с (99 % от максимальной) при длине пакетов 128 байт и 1740 МБ/с (99% от максимальной) при длине пакета 256 байт. Латентность передачи данных между ПЛИС зависит от количества промежуточных коммутаторов, и была равна 0,7 мкс для одного коммутатора и 1 мкс для трех. Также показано, что при одновременных передачах через общий канал скорость отдельных передач не уменьшается до тех пор, пока суммарная скорость передачи не превышает пропускную способность общего канала; затем канал используется на 100%, а его пропускная способность делится поровну между устройствами.

Читать полностью »

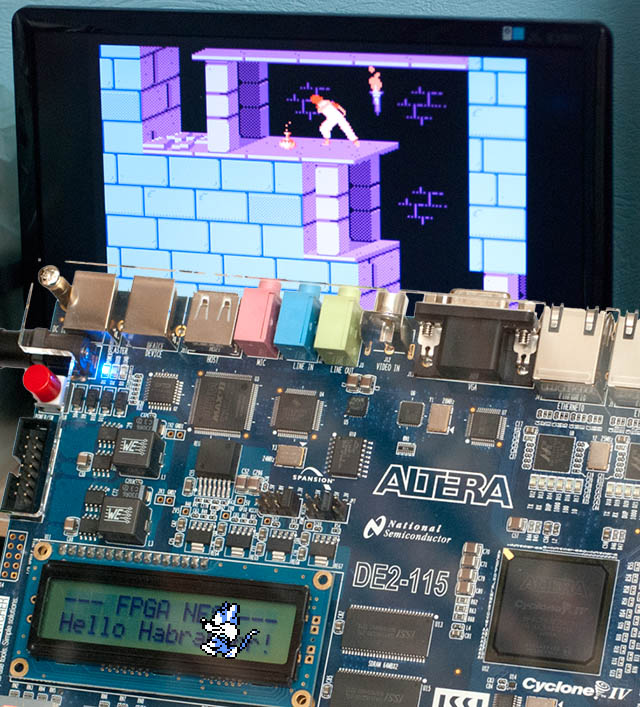

NES, реализация на FPGA

2013-07-08 в 7:58, admin, рубрики: Altera, dendy, diy или сделай сам, fpga, Nes, Verilog, денди, игровая консоль, Игровые приставки, ностальгия, ПЛИС, метки: Altera, dendy, fpga, Nes, Verilog, денди, игровая консоль, ностальгия, ПЛИСДобрый день!

Я хочу рассказать о проекте игровой консоли Nintendo Entertainment System (NES) в реализации на FPGA. На постсоветском пространстве она известна как Dendy.

Желающих посмотреть видео и поностальгировать прошу под кат.

Читать полностью »

-na-FPGA-XeonPhi-GPU-2.png)