Есть несколько событий и тем, которыми хотелось бы поделиться с сообществом. По-хорошему, по каждой можно писать отдельную статью, но общий дефицит времени заставляет немного схалтурить. Наши сегодняшние темы:

- релиз MIPSfpga 2.0;

- процессор schoolMIPS и Летняя школа юных программистов в Новосибирске;

- школа-семинар по цифровому дизайну и компьютерной архитектуре в Томске;

- запуск ванильного ядра Linux на MIPSfpga-plus;

- поддержка АЦП Altera MAX10 в MIPSfpga-plus;

- логотип MIPSfpga-plus.

Если тематика MIPSfpga-plus вам не безразлична, то в конце есть небольшой опрос на тему чего мне писать (или не писать) следующую статью. Ваш выбор поможет мне сориентироваться и расставить приоритеты. Welcome!

Релиз MIPSfpga 2.0

Спустя 2 года после первого релиза MIPSfpga компания Imagination Technologies выпустила вторую версию пакета: MIPSfpga 2.0 [L1].

На что следует обратить внимание:

- как и прежде MIPSfpga преподносится не только как открытые под академической лицензией исходные коды промышленного процессорного ядра, а еще и как набор образовательных материалов, включающий также документацию и лабораторные работы. И это прекрасно, потому что в комплекте с не так давно переведенной на русский язык книгой "Цифровая схемотехника и архитектура компьютера" (H&H) [L2] мы получаем очень качественный и доступный набор теории и практики, преподносимый на примере архитектуры MIPS;

- на недавно прошедшем в Торонто симпозиуме [L3] Сара Харрис (один из авторов H&H) представила коллективную статью [L14], в которой приводится достатовно подробное описание MIPSfpga 2.0, а также анализ распространения образовательной инициативы Imagination Technologies по ВУЗам.

И (вау!) там даже упоминается мое имя в связи с активностью в проекте MIPSfpga-plus. - если первый релиз был в основном сконцентрирован на том, как собрать систему на кристалле (СнК) на базе MIPSfpga, то втором акцент смещен именно на работу самого процессора:

1 Create a Project in Vivado or Quartus-II

2 Learn how to compile, debug and run C programs

3 Learn MIPS Assembly Programming system

4 More C Programming Practice (optional)

5 Expand the system to add 7-segment displays

6 Expand the system to add a counter

7 Expand the system to add a buzzer

8 Expand the system to add an SPI-Light Sensor

9 Expand the system to add a SPI-LCD

10 Interact with peripherals using interrupts

11 Build a DMA engine for transfers between peripherals

12 Build a Data Encryption Standard (DES) engine

13 Learn how to use the Performance Counters

14 Execution of ADD and other arithmetic instruction

15 Execution of AND and other logic instructions

16 Execution of LW and other related instructions

17 Execution of BEQ and other related instructions

18 Learn how the Hazard Unit is implemented

19 Learn how to use the CorExtend interface

20 Introduction to the caches available in MIPSfpga

21 Analyze the D$ and implement new configurations

22 Cache Controller: Analyze a cache hit and miss

23 Cache Controller: Analyze D$ management policies

24 Cache Controller: Analyze the Store and Fill Buffers

25 Implement an Instruction Scratchpad RAM

- само ядро по предварительной информации особых изменений не претерпело, это все то же MIPS microAptiv UP, на базе которого построен, к примеру, Microchip PIC32MZ;

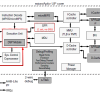

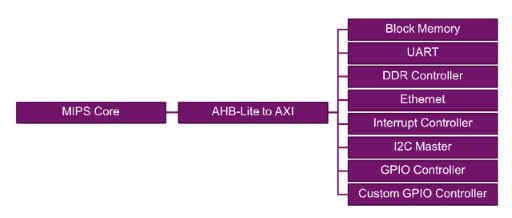

- неизменной осталась и ориентированность на Xilinx при построение СнК в лабораторных работах. Так, общая схема используемой в лабораторных работах СнК выглядит следующим образом, что несколько ограничивает запуск на Altera-based платах:

Если учесть, что компания Digilent искуственно ограничивает поставки своих плат на без ПЛИС Xilinx в Россию и на Украину, то картина получается не очень приятная. Но тут нам на помощь приходит MIPSfpga-plus — opensource проект по построению СнК на базе MIPSfpga с платформонезависимой периферией [L4]. Для корректного взаимодействия с MIPSfpga 2.0 его, возможно, придется немного доработать.

schoolMIPS и Летняя школа юных программистов

Сегодня в Новосибирске открылась Летняя школа юных программистов [L5]. Учебная программа школы предполагает разделение на мастерские [L6], одна из которых ориентирована на преподавание Verilog и архитектуры микросхем. Преподавателем у ребят будет Юрий Панчул YuriPanchul, который специально ради этого дела прилетел из Штатов.

Мастер: Юрий Панчул

Цифровое железо, от логических элементов до собственного процессора

Хотите узнать, как проектируют микросхемы в современных устройствах — от телефона до космического корабля? Последние 25 лет это делают с помощью методологии логического синтеза кода на языках описания аппаратуры. Именно эту технологию мы выучим в нашей мастерской и применим для проектирования собственных устройств.

Мы начнем с трех ключевых кирпичиков цифровой электроники — логического элемента, тактового сигнала и D-триггера, памяти для одного бита информации. Для наглядности мы освоим их старомодным способом, соединяя проводами микросхемы малой степени интеграции на макетной плате.

Затем мы повторим построенные схемы на языке описания аппаратуры SystemVerilog и промоделируем их на программе-симуляторе. Но как мы можем воплотить их в микросхемы? Ведь заказ коммерческой микросхемы на фабрике очень дорогой? К счастью, существуют “перестраиваемые” программируемые логические интегральные схемы (ПЛИС), платы с которыми которые мы и будем использовать для наших занятий.

Помимо упражнений с арифметическими блоками и конечными автоматами, мы попробуем построить простой процессор, похожий по микроархитектуре на процессор Mongoose-V внутри космического корабля New Horizons, который год назад пролетел мимо Плутона.

Заодно мы изучим немного программирования на ассемблере, концепцию прерываний, сравним свой процессор с промышленными микроконтроллерами и встроенными микропроцессора, вплоть до микропроцессора EyeQ5 для самодвижущегося автомобиля, который планируется для выпуска в 2020 году.

Это круто, и я, если честно, немного завидую этим школьникам — в моем детстве такого не было.

Специально для данного мероприятия мы написали небольшой процессор MIPS-архитектуры: schoolMIPS [L7], который планируется использовать в образовательном процессе. Он построен путем упрощения процессора Сары Харрис, описанного в H&H [L2]. Основные особенности:

- язык описания аппаратуры Verilog;

- подмножество архитектуры MIPS с памятью инструкций, с регистрами общего назначения, но без памяти данных;

- однотактовая микроархитектура;

- минимальный набор инструкций, первоначально достаточный для вычисления числа Фибоначчи и целочисленного квадратного корня итеративным способом;

- максимально упрощенные в целях преподавания микроархитектура и код;

- компиляция программ осуществляется средствами MIPS toolchain.

В комплекте идет небольшая инструкция и слайды, описывающие построение процессорного ядра в стиле аналогичном H&H [L2].

Помимо написания процессора был выполнен достаточно масштабный перевод на русский язык различных образовательных материалов. Эту тему я затрагивать не буду, т.к. не участвовал, полагаю, что Юрий YuriPanchul в будущем об этом еще напишет.

Школа-семинар по цифровому дизайну и компьютерной архитектуре в Томске

С 18 по 22 сентября на базе Томского государственного университета пройдет Школа–семинар по цифровому дизайну и компьютерной архитектуре в эпоху систем на кристалле (SoC) и интернет технологий (IoT). Предварительная программа школы и список участников опубликованы на сайте [L8]. Там будет выступать и ваш покорный слуга: планирую рассказать про AHB-Lite, подключение периферии к MIPSfpga, работу с SDRAM — это со сцены. А неофициально можем обсудить Linux, подключение отладчика и любой код, который я принес в MIPSfpga-plus. Приходите!

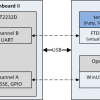

Запуск Linux на MIPSfpga-plus

Лабораторные работы MIPSfpga описывают запуск Linux на СнК, построенной с использованием Xilinx-специфических периферийных модулей. Вкупе с уже упомянутой выше проблемой с доступом к платам это создавало некоторые трудности. Необходимым минимумом для запуска ОС Linux являются: MMU (есть в составе MIPS fpga), достаточный объем памяти и UART. При этом большая часть работ по портированию системы уже выполнена Imagination Technologies, соответствующий код включен в основную ветку ядра [L9]. Буквально неделю назад у меня получилось запустить Linux на Terasic DE10-Lite и не скажу, что необходимый для этого патч получился очень сложным.

Основные особенности:

- конфигурация системы: ПЛИС Altera MAX10, SDRAM 64Мб,MIPSfpga-plus, UART16550;

- ядро загружается в память с помощью EJTAG [L10];

- mmc/sdcard пока не поддерживаются, поэтому о загрузке с карты памяти говорить не приходится. С другой стороны, в лабораторных работах MIPSfpga о загрузки с флешки речь также не идет.

Linux version 4.12.2+ (stas@ubuntu) (gcc version 4.9.2 (Codescape GNU Tools 2016.05-03 for MIPS MTI Linux) ) #67 Wed Jul 19 00:07:19 MSK 2017

CPU0 revision is: 00019e60 (MIPS M14KEc)

MIPS: machine is terasic,de10lite

Determined physical RAM map:

memory: 04000000 @ 00000000 (usable)

Initrd not found or empty - disabling initrd

Primary instruction cache 4kB, VIPT, 2-way, linesize 16 bytes.

Primary data cache 4kB, 2-way, VIPT, no aliases, linesize 16 bytes

Zone ranges:

Normal [mem 0x0000000000000000-0x0000000003ffffff]

Movable zone start for each node

Early memory node ranges

node 0: [mem 0x0000000000000000-0x0000000003ffffff]

Initmem setup node 0 [mem 0x0000000000000000-0x0000000003ffffff]

Built 1 zonelists in Zone order, mobility grouping on. Total pages: 16256

Kernel command line: console=ttyS0,115200

PID hash table entries: 256 (order: -2, 1024 bytes)

Dentry cache hash table entries: 8192 (order: 3, 32768 bytes)

Inode-cache hash table entries: 4096 (order: 2, 16384 bytes)

Memory: 60512K/65536K available (1827K kernel code, 97K rwdata, 320K rodata, 948K init, 184K bss, 5024K reserved , 0K cma-reserved)

NR_IRQS:8

clocksource: MIPS: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 38225208935 ns

sched_clock: 32 bits at 50MHz, resolution 20ns, wraps every 42949672950ns

Console: colour dummy device 80x25

Calibrating delay loop... 10.81 BogoMIPS (lpj=21632)

pid_max: default: 32768 minimum: 301

Mount-cache hash table entries: 1024 (order: 0, 4096 bytes)

Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes)

devtmpfs: initialized

clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 7645041785100000 ns

futex hash table entries: 256 (order: -1, 3072 bytes)

clocksource: Switched to clocksource MIPS

random: fast init done

workingset: timestamp_bits=30 max_order=14 bucket_order=0

Serial: 8250/16550 driver, 4 ports, IRQ sharing disabled

console [ttyS0] disabled

b0400000.serial: ttyS0 at MMIO 0xb0401000 (irq = 0, base_baud = 3125000) is a 16550A

console [ttyS0] enabled

Freeing unused kernel memory: 948K

This architecture does not have kernel memory protection.

mount: mounting devpts on /dev/pts failed: No such device

mount: mounting tmpfs on /dev/shm failed: Invalid argument

mount: mounting tmpfs on /tmp failed: Invalid argument

mount: mounting tmpfs on /run failed: Invalid argument

Starting logging: OK

Initializing random number generator... done.

Starting network: ip: socket: Function not implemented

ip: socket: Function not implemented

FAIL

Welcome to MIPSfpga

mipsfpga login: root

Jan 1 00:00:09 login[43]: root login on 'console'

# uname -a

Linux mipsfpga 4.12.2+ #67 Wed Jul 19 00:07:19 MSK 2017 mips GNU/Linux

# free -m

total used free shared buffers cached

Mem: 60 3 56 0 0 2

-/+ buffers/cache: 0 59

Swap: 0 0 0В ближайшее время планирую подготовить небольшое HOWTO о том, как воспроизвести эти результаты. А большую статью, наверное, напишу после добавления в MIPSfpga-plus модуля для работы с mmc/sdcard, допиливания загрузчика и отладки всего, что необходимо для автономного запуска. Если кому-то нужно "вот прямо сейчас" — дайте знать.

MIPSfpga-plus и АЦП Altera MAX10

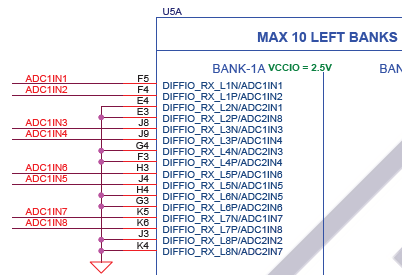

В июне закончил работу по интеграции АЦП, который есть на борту Altera MAX10, в MIPSfpga-plus. Соответствующий код добавлен в основную ветку проекта [L11], с документацией [L12] и примером [L13]. Модуль, фактически, является конвертером между шиной AHB-Lite и Avalon-ST, выполненный учетом специфики конкретного АЦП. Он очень прост по архитектуре — старался сделать его программный интерфейс максимально похожим на АЦП микроконтроллера Atmel ATmega88.

Не обошлось, конечно, и без подводных камней, так на используемой в Terasic DE10-Lite ПЛИС доступно 2 канала АЦП (с независимым наборов вводов на каждом), при разводке этих вводов второй канал оказался целиком заземлен, т.о. параллельная работа каналов на DE10-Lite — невозможна:

Хочется верить, что в академических проектах будет чуть чаще использоваться MIPSfpga-plus там, где до этого ради встроенного АЦП нужно было брать микроконтроллер или конфигурацию MAX10 + NIOS-II.

Опять же, нужна ли отдельная статья, где детально разбирается работа с АЦП? Или для того, чтобы разобраться, вам достаточно уже приведенных мной ссылок на исходный код модуля, примера и документацию?

Логотип MIPSfpga-plus

Как вы считаете, проект MIPSfpga-plus достаточно созрел для того, чтобы у него появился свой узнаваемый логотип? Мне, наверное, потратив на него не один десяток часов, уже хочется, чтобы он ассоциировался с какой-нибудь позитивной картинкой. Почему-то в голову приходит только Большой Ух из одноименного мультика (см. КДПВ), возможно, что из-за его конфедератки, которая хорошо ассоциируется с изначально образовательной направленностью проекта. Да и в принципе данный персонаж мне глубоко симпатичен.

Что думаете на эту тему? Может быть вы сможете предложить какой-то альтернативный вариант или, вдруг, среди читателей есть художник, который может изобразить "мультипликационного персонажа, отдаленно напоминающего Большого Уха, но не до степени смешения"?

Благодарности

Автор выражает благодарность коллективу переводчиков учебника Дэвида Харриса и Сары Харрис «Цифровая схемотехника и архитектура компьютера» [L2], компании Imagination Technologies [L1] за академическую лицензию на современное процессорное ядро и образовательные материалы, а также персонально Юрию Панчулу YuriPanchul за его работу по популяризации MIPSfpga. Отдельное большое спасибо Александру Романову (ВШЭ) [L15] за дельный и скрупулезный подход к микроархитектуре schoolMIPS, а также всем участникам списка рассылки Young Russian Chip Architects, принявшим участие в обсуждении.

Ссылки

[L1] — Пресс-релиз о выходе MIPSfpga 2.0;

[L2] — Цифровая схемотехника и архитектура компьютера;

[L3] — Workshop on Computer Architecture Education (Toronto);

[L4] — Проект MIPSfpga-plus на github;

[L5] — Летняя школа программистов (Новосибирск);

[L6] — Летняя школа программистов (Новосибирск). Учебная программа;

[L7] — Проект schoolMIPS на github;

[L8] — Школа–семинар по цифровому дизайну и компьютерной архитектуре (Томск);

[L9] — Поддержка MIPSfpga в ядре Linux;

[L10] — MIPSfpga и внутрисхемная отладка;

[L11] — MIPSfpga-plus. Модуль поддержки АЦП Altera MAX10;

[L12] — MIPSfpga-plus. Модуль поддержки АЦП Altera MAX10. Документация;

[L13] — MIPSfpga-plus. Модуль поддержки АЦП Altera MAX10. Пример;

[L14] — Practical experiences based on MIPSfpga;

[L15] — Профиль Александра Романова на сайте ВШЭ.

Автор: SparF