На Хабре есть статьи для начинающих ПЛИСоводов, есть статьи с обзорами средств трассировки печатных плат. На некоторые из них я уже ссылался в своей первой статье о создании печатных плат. Во второй статье про SimBank в комментариях у меня состоялся диалог о сложности разработки ПЛИС и поддержки проектов с ней. Было высказано мнение, что легче собрать несколько простых устройств вместо одного сложного. Иногда так действительно проще. Когда речь идёт о двух, четырёх, восьми устройствах. Ряд можно продолжать с привычной вам кратностью. До преодоления порога комфорта. Два — это куча? А что делать, если есть желающие на 100 или 200 однотипных устройств?

Использовать или не использовать ПЛИС в той или другой задаче каждый решает сам (или с коллегами).

Сегодня хочу предложить вашему вниманию статью об особенностях создания печатной платы с ПЛИС. За основу возьмём инструмент «IO Designer» от компании Mentor Graphics. Кому-то может материал оказаться полезным, кому-то просто интересным, а кто-то может и не согласиться со мной.

Читать полностью »

Рубрика «fpga» - 34

Cхема > плата > ПЛИС

2014-11-10 в 21:31, admin, рубрики: Altera, Cyclone, Expedition PCB, fpga, IO Designer, Kintex, mentor graphics, pcb, разработка, Электроника для начинающихSimBank или 200 SmartCard в одной коробке

2014-10-22 в 14:10, admin, рубрики: fpga, gsm, ip-телефония, ISO-7816, linux, pcb, PCI, ram, SignalTap, sim-карта, Smart Card, sms, Verilog, voip, ПЛИС, разработкаКак я уже писал в своём первом топике на Хабре про создание печатной платы, моя фирма занимается разработкой устройств для телефонии разного рода VoIP-, GSM-, PBX-шлюзов, розетки-ребутеры управляемые через GSM и прочее. Сегодня я опишу процесс разработки прошивки для устройства SimBank в его PCI версии, где я выступил в роли разработчика схемы для ПЛИС.

История постановки задачи от руководства + история работы устройства

Устройство SimBank предназначено для работы с SIM (Subscriber Identification Module — модуль идентификации абонента) картой. Данные карты являются разновидностью ISO-7816 карт.

Читать полностью »

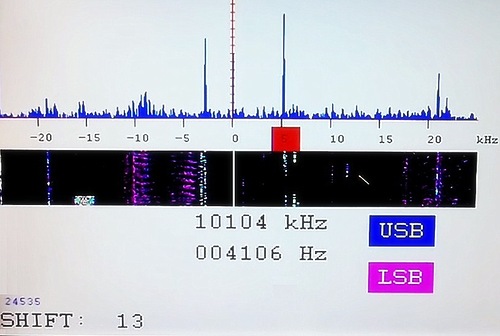

Автономный SDR приёмник на ПЛИС

2014-10-06 в 20:12, admin, рубрики: diy или сделай сам, fpga, Nios. ПЛИС, SDR, приемник, Электроника для начинающих

Ранее я уже писал про самодельный SDR приемник, сделанный на базе отладочной платы DE0-nano. Как и большинство других SDR приемников, он не был способен работать без подключения к компьютеру. При этом в использованной ПЛИС оставалось еще большое количество неиспользованных ресурсов, так что я решил сделать приемник полностью автономным.

О том, как же работает весь SDR приемник целиком, и как его реализовать — далее.

Читать полностью »

Создание печатных плат для мелкосерийного производства

2014-10-02 в 6:29, admin, рубрики: fpga, voip, Железо, печатные платы, разработкаНа Хабре много статей по настройке и сопровождению IP телефонии и сопутствующего оборудования. Встречаются статьи и по разработке печатных плат. Есть статьи и о том, как самому сделать печатную плату при помощи ЛУТ технологии. Например, «ЛУТ на виниле или домашняя Arduino Mini». Есть описание разных систем проектирования печатных плат: Cadence, Eagle , DipTrace или описание отдельных процессов при разработке печатных плат, таких как передача информаци из Altium в AutoCAD.

Хочу представить статью о том, как происходит постановка на производство печатной платы на основе опыта фирмы и собственного опыта по другим работам. Моей задачей является модернизация существующей платы для усовершенствования существующих качеств и, возможно, открытия новых, доселе не виданных для нее горизонтов.

Читать полностью »

Пару слов о конвейерах в FPGA

2014-09-23 в 10:59, admin, рубрики: fmax, fpga, loop_engine, mac_swap, pipeline, SystemVerilog, Verilog, высокая производительность, конвейер, ПЛИС, Электроника для начинающихВсем привет!

Многим известно, что во всех современных процессорах есть вычислительный конвейер. Бытует заблуждение, что конвейер — это какая-то фишка процессоров, а в чипах для других приложений (к примеру, сетевых) этого нет. На самом деле конвейеризация (или pipelining) — это ключ к созданию высокопроизводительных приложений на базе ASIC/FPGA.

Очень часто для достижения высокой производительности выбирают такие алгоритмы, которые легко конвейеризируются в чипе. Если интересно узнать о низкоуровневых подробностях, добро пожаловать под кат!

Читать полностью »

Ты ждал знак? Вот он!

Много лет я не решался начать программировать ПЛИС, потому что это сложно, дорого и больно (как мне казалось). Но хорошо, когда есть друзья, которые помогают сделать первый шаг. И теперь я не понимаю одного — ПОЧЕМУ Я ЖДАЛ ТАК ДОЛГО?

Сейчас я помогу сделать первый шаг и тебе!

Сумбурные размышления о будущем технологии FPGA

2014-09-09 в 8:10, admin, рубрики: fpga, виртуальная память, игра жизнь, ненормальное программирование, параллельное программирование, ПЛИС, Электроника для начинающих

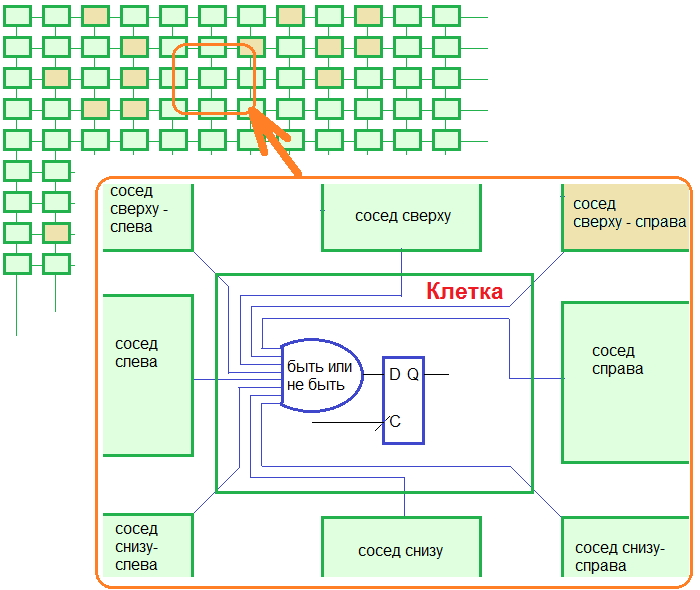

Работая над очередным игровым (обучающим) проектом ПЛИС для платы Марсоход2 я столкнулся с тем, что мне явно не хватает места в кристалле. Кажется и проект не очень сложный, но моя реализация такова, что требует много логики. В принципе, это ерунда, дело-то житейское. Ну, если очень будет нужно, то можно выбрать ПЛИС с большей емкостью. Собственно мой проект — это игра «Жизнь», но реализованная в ПЛИС на языке Verilog HDL.

Про логику игры, рассказывать не буду, про нее и так написано уже достаточно.

Идея проекта вот такая: каждая клетка в игровом поле представляет собой самостоятельный вычислитель. В каждом вычислителе есть своя логическая функция и свой регистр, который хранит текущее состояние клетки (живая/не живая). Все пространство для жизни клеток — это двумерный массив вычислителей, вычислители образуют целую сеть. Все вычислители работают синхронно, так как на все регистры подается единая тактовая частота. Рисунок вверху должен прояснить схему проекта.

Так вот. На моей плате стоит ПЛИС Cyclone III EP3C10E144C8 компании Альтера. 10тыс логических элементов. Сперва я думал, что смогу сделать двумерный массив клеток 128x64=8192 клетки. Не помещается. 64x64=4096 — то же не помещается в кристалл. Как же так. Я сумел вместить в ПЛИС только 32x16=512 клеток. Пичалька…

Размышления приводят меня к мысли, что возможно, в будущем, технология ПЛИС перерастет в нечто большее, чем программируемая логика. Вот об этом своем видении я хотел бы рассказать. Искушенному читателю сразу скажу, что многое далее написанное есть просто плод воображения и может быть даже бред.

Однако..Читать полностью »

Взгляд на 10G Ethernet со стороны FPGA разработчика

2014-08-24 в 9:47, admin, рубрики: 10g, 10gbe, ethernet, fpga, phy, xaui, xgmii, ПЛИС, Сетевое оборудование, Сетевые технологииВсем привет!

Многие специалисты знают, что топовое сетевое оборудование использует специальные чипы для обработки трафика. Я принимаю участие в разработке таких молотилок и хочу поделиться своим опытом в создании таких высокопроизводительных девайсов (со интерфейсами 10/40/100G Ethernet).

Для создания нового канала сетевики чаще всего берут оптику, пару SFP+ модулей, втыкают их в девайсы: радостно загораются лампочки, пакеты начинают приходить и чип начинает его передавать получателям. Но как чип получает пакет из среды передачи? Если интересно, то добро пожаловать под кат.

Читать полностью »

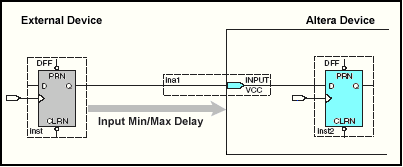

Временной анализ FPGA или как я осваивала Timequest

2014-08-07 в 12:50, admin, рубрики: Altera, fpga, Quartus II, timequest, ПЛИС, Программинг микроконтроллеровДоброго времени суток, уважаемые читатели.

На самом деле я инженер-радиофизик и программирование ПЛИС не является моей непосредственной деятельностью, но в один момент понадобилось написать программу для синхронизации нескольких осцилографических модулей. Пришлось осваивать эту науку. О том, какие у меня возникли с этим проблемы, под катом.