Что нам стоит UAV построить 2 – От поликремния к кристаллу

В комментариях к статье Вредные заблуждения о нанометрах. Или почему наличие в России доступа только к 90нм – это катастрофа [1] проявилась масса экспертов со свежей регистрацией и продемонстрированным отсутствием понимания работы индустрии в целом. В моей попытке раскрыть тему производства с самого начала [2] экспертов было меньше, возможно в методичке не было нужной главы или, как там у последнего Пелевина – проекционно-идеологический ресурс, усиленный тремя медиа-валькириями, перебросили на азиатское направление. Но тут уже стало интересно мне, а чего там сложного.

Напомню: Оборудование можно сделать и самим, но пока можно и просто привезти серым импортом. Оборудование выглядит примерно как большой ящик с дырками, включённый в розетку; в одну дырку складываешь кремний, в другую заливаешь фоторезистор. Под третью дырку надо подставить ведро — в него будут ссыпаться чипы. Вёдра мы делать умеем (хотя и импортируем сейчас, но чертежи-то остались), фоторезистор научатся намешивать в Зелинограде; с кремнием разберемся, не всё сразу. Надо ещё заранее заказать в Китае переходник с европейской розетки на нормальную — лучше сразу 3 или 4, они постоянно горят. Вроде все ясно. И надо ещё 3 или 4 росгвардейца, чтобы ведро не (стащили). © [3] @hippohood [4](кстати - автор в RO).

В первой части [2] я остановился на том, что полученный монокристалл распиливают на будущие ядра. Или будущие модули памяти. Или FPGA. Или SSD – разных классов чипов в готовом ПК довольно много, начиная от диодов в блоке питания [5], там же диоды Шоттки, ШИМ –контроллеры, стабилитроны, тиристоры - вплоть до микроконтроллеров управления с своим микрокодом. Почитайте, кто забыл или не знал [5]. Ситуация с российской электронной базой описывается словом ВЕЧНОСТЬ, только букв для сборки слова всего 4 – А, О, П, дальше знаете [6] (очень богатая на комментарии и плюсы статья). Попытка поискать кошку в темной комнате была в 2020 [7], сейчас, похоже, ситуация изменилась (неужели все же что то случилось?)

Начав в 1960 году с 1-дюймовых (в диаметре) полупроводниковых пластин, индустрия пришла к стандартным размерам полуфабрикатов – 1976 – 100мм диаметра и 0.525 мм толщиной, 1981 – 125 мм / 0.625 мм, 1983-150/0.675, 1992 – 200/0.725 (запомним год), 2002 – 300/0.775 – довольно тонкие пластины. (Примечание – 200 мм пластины при фактическом диаметре маркируются как 8-дюймовые, 300мм – 11.8 фактически, 12 дюймов по маркировке). 450 –мм пластины находятся «в разработке». Причины таких ограничений – растить монокристалл сложно, в какой-то момент монокристалл начинает расти «не как надо». К тому же еще и кристалл растет как не всегда надо – или даже совсем как не надо. [8]

Проблема на этом этапе – производителей полупроводниковых пластин (wafers) в мире .. пять штук. Как верно написано тут [9]- В отличие от AMD, Apple и TSMC имена производителей этих материалов известных лишь среди специалистов: Air Liquide, Cabot, Linde, JSR, Sumco, GlobalWafer и другие.

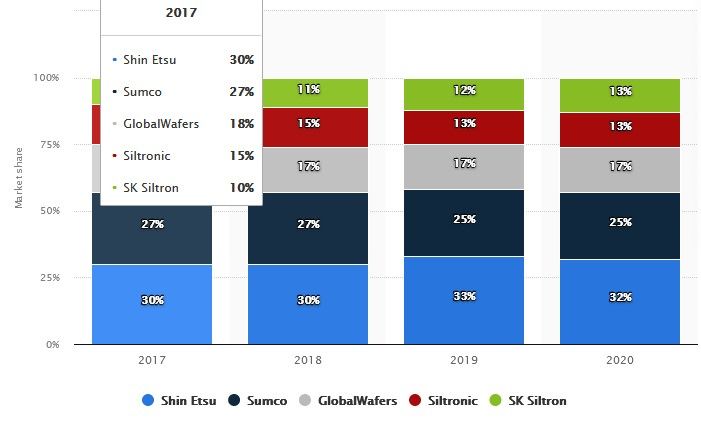

2020 год, доли рынка:

-

Shin Etsu - 32% (Япония),

-

Sumco - 25% (Япония, итог слияния трех подразделений - The company was formed in 2002 as Sumitomo Mitsubishi Silicon Corp. in a merger between Mitsubishi Materials Silicon Corp. and the Sitix Division of Sumitomo Metal Industries, Ltd. The company changed its name to SUMCO [10]in 2005, and acquired Komatsu Electronic Metals Co., Ltd. the following year.),

-

GlobalWafers- 17% (Тайвань),

-

Siltronic- 13% (Заводы: Германия, США, Сингапур – совместно с Samsung Electronic of South Korea),

-

SK Siltron- 13% (Южная Корея, но производство только 150 и 200 мм) (источник [11])

При этом Sumco объявила (2021, [12]2022 [13]) – что расширять производство не будет, потому что расширение не окупится.

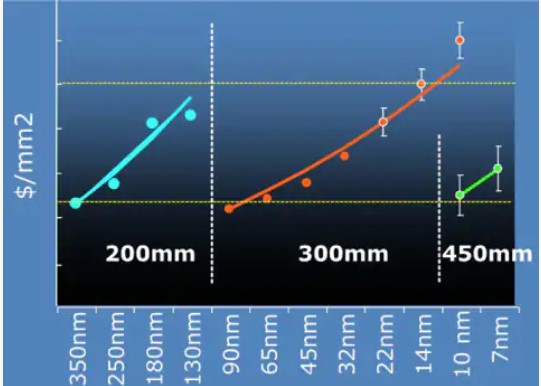

Вы, конечно, спросите, зачем вообще растить толстые кристаллы? Давайте растить тонкие, 100-мм вырастить проще, и дефектов меньше. Все так, тонкие (меньшего диаметра) растить проще, но давайте говорить за деньги

Rising cost of device production associated with greater scaling can be curbed by adopting larger wafer diameters.

Source: Intel

Источник [10]

Все от денег – на плате большего диаметра умещается больше блоков (die, он же dice, они же dies – кубики [14]). Процесс нарезки называется dicing.

Конечно, можно делать и на 100, и на 125 мм пластине. Но на 300-мм дешевле.

Заграница нам поможет: поможет, да. В 2020 году в Китае делали пластины в 156.75 мм под солнечные батареи и переходили на 182 мм.

Дальше пластину начинают полировать. От блока толщиной в 0.775 мм (775 µm – микрометров или микрон, или 775000 нанометров) остается несколько меньше – от 0.1 мм для логических ворот, они же вентили (logic gates) до 0.05 мм для DRAM и 0.03 для микроэлектромеханики (MEMS [15])

Полируют, разумеется, не пастой государственного оптического института номер 2. Точность полировки – я не искал, поищите кто хочет. Полученную пластину измеряют [15]- и затем начинается процесс поиска масок.

С масками все очень просто, там было всего 11 стадий подготовки:

-

Step 1: Plasma Cleaning

-

Step 2: HMDS Application

-

Step 3: Resist Application

-

Step 4: Pre-Bake

-

Step 5: Lithographic Patterning

-

Step 6: Post Bake

-

Step 7: Develop

-

Step 8: Plasma De-scum

-

Step 9: Cr Etch

-

Step 10: Resist Removal and Mask Clean

-

Step 11: Final Inspection

Источник [16]

Чуть не забыл: маску сначала надо спроектировать так, чтобы:

К основным методам вычислительной литографии относятся фазосдвигающие маски (PSM) и оптическая коррекция близости (OPC). Используемая с 90-нанометрового процесса (2006 г.) технология PSM — это коррекция толщины отдельных «пикселей» маски для изменения их прозрачности, что меняет фазу проходящего сквозь них света. Учитывая волновые свойства, это позволит (не считаясь с длиной волны) экспонировать на фоторезисте рисунок, отдельные элементы которого либо усилены синфазным наложением волновых пиков, либо удалены противофазным — это увеличивает разрешение, приближая тот самый параметр k1 к идеалу. Более современная OPC искажает рисунок маски для компенсации ошибок получаемого изображения из-за дифракции падающих волн. OPC нужна уже не для увеличения разрешения, а для исправления искажений одиночных структур, форма которых при таких размерах получается куда хуже, чем если бы элементы были регулярными. (Источник [17])

И затем, когда в одном помещении удалось собрать подложки, маски, фоторезист, степперы и откачать из помещения всю пыль, и заодно обеспечить передачу пластин с одного этапа (например, химической полировки) в степпер без загрязнения пластины пылью – можно уже начинать само производство – согласно статье Закон Мура против нанометров: Всё, что вы хотели знать о микроэлектронике, но почему-то не узнали [17]…

Литература

(2007) Photomask Making [16]

(2010) От песка до процессора [18]

Как на самом деле производят процессоры [19]

(2010) Закон Мура против нанометров [20]

(2018) Photomask – с массой видео как это делается [21]

(2020) Intel Lakefield 3D Stacked CPU Gives a Glimpse of the Future [22]

Что такое импульсный блок питания (ИБП) и как он работает [5]

(2020) Где прячется Российская электроника [23]

(2022) Микроэлектроника в России до и после 24.02.2022 [24]

(2022) Про импортозамещение [6]

Wafer (electronics [25])

Does size matter? Understanding Wafer Size [26]

From 20 mm to 450 mm: The Progress in Silicon Wafer Diameter Nodes [27]

Kerf-Less Exfoliated Thin Silicon Wafer Prepared by Nickel Electrodeposition for Solar Cells [28]

(2022) Полюса силы в мире чипов [9]

(2021) Глобальный дефицит микросхем коснулся поставок мониторов [12]

(2022) Ключевой поставщик пластин для чипов Sumco оказался загружен заказами до 2026 года [13]

Market share of wafer producers worldwide from 2017 to 2020 [11]

Wafer Backgrinding and Semiconductor Thickness Measurements [15]

PS. Я думаю, что имеет какой-то практический смысл написать еще две статьи. Первую про платы как таковые, про число слоев и сложности проектирования и производства, и вторую - про то, что ввоз чемодана процессоров 2010 года мало значим. Или нет, про ожирение статьи нужнее и популярнее.

Автор: MechanicusJr

Источник [29]

Сайт-источник PVSM.RU: https://www.pvsm.ru

Путь до страницы источника: https://www.pvsm.ru/chital-ny-j-zal/380494

Ссылки в тексте:

[1] Вредные заблуждения о нанометрах. Или почему наличие в России доступа только к 90нм – это катастрофа: https://habr.com/ru/post/698176/

[2] тему производства с самого начала: https://habr.com/ru/post/698706/

[3] ©: https://habr.com/ru/company/selectel/blog/664260/comments/#comment_24332758

[4] @hippohood: https://habr.com/users/hippohood

[5] начиная от диодов в блоке питания: https://elektroznatok.ru/info/elektronika/impulsnyj-blok-pitaniya

[6] А, О, П, дальше знаете: https://habr.com/ru/post/599671/

[7] 2020: https://habr.com/ru/company/lamptest/blog/512812

[8] или даже совсем как не надо.: https://www.universitywafer.com/silicon-wafer-thickness-range.html

[9] тут : https://habr.com/ru/company/first/blog/697452/

[10] SUMCO : https://www.tel.com/museum/magazine/material/150430_report04_03/02.html

[11] источник : https://www.statista.com/statistics/895360/global-wafer-producers-market-share/

[12] 2021, : https://habr.com/ru/news/t/551186/

[13] 2022: https://habr.com/ru/news/t/650717/

[14] они же dies – кубики: https://www.merriam-webster.com/dictionary/die

[15] MEMS: https://mtiinstruments.com/wafer-backgrinding-semiconductor-thickness/

[16] Источник: https://cleanroom.utdallas.edu/manuals/photomask-making/

[17] Источник: https://www.ixbt.com/cpu/microelectronics.shtml

[18] От песка до процессора: https://habr.com/ru/company/intel/blog/110234/

[19] Как на самом деле производят процессоры: https://thecode.media/intel_inside/

[20] Закон Мура против нанометров: https://www.ixbt.com/cpu/microelectronics-1.shtml

[21] Photomask – с массой видео как это делается: https://semiengineering.com/knowledge_centers/manufacturing/lithography/photomask/

[22] Intel Lakefield 3D Stacked CPU Gives a Glimpse of the Future: https://play3r.net/news/press-release/intel-lakefield-3d-stacked-cpu-gives-a-glimpse-of-the-future/

[23] Где прячется Российская электроника: https://habr.com/ru/company/lamptest/blog/512812/

[24] Микроэлектроника в России до и после 24.02.2022: https://habr.com/ru/post/656677/

[25] electronics: https://en.wikipedia.org/wiki/Wafer_(electronics)#Historical_increases_of_wafer_size

[26] Does size matter? Understanding Wafer Size: https://anysilicon.com/does-size-matter-understanding-wafer-size/

[27] From 20 mm to 450 mm: The Progress in Silicon Wafer Diameter Nodes: https://www.tel.com/museum/magazine/material/150430_report04_03/

[28] Kerf-Less Exfoliated Thin Silicon Wafer Prepared by Nickel Electrodeposition for Solar Cells: https://www.ncbi.nlm.nih.gov/pmc/articles/PMC6339913/

[29] Источник: https://habr.com/ru/post/698996/?utm_source=habrahabr&utm_medium=rss&utm_campaign=698996

Нажмите здесь для печати.