Разработка процессорного модуля на базе микросхемы 1892ВА018 СнК «СКИФ» и его первый запуск

Версия данной статья для "off-line прочтения" в формате PDF доступна по адресу: ссылка на статью в в формате PDF [1].

1. Вступление [2]

3. Система-на-кристалле 1892ВА018 «СКИФ» [4]

4. Внутренняя структура 1892ВА018 СнК «СКИФ» [5]

5. Система обеспечения безопасности микросхемы 1892ВА018 СнК «СКИФ» [6]

6. Загрузка микросхемы 1892ВА018 СнК «СКИФ» [7]

7. Загрузка СнК «СКИФ» — более подробно [8]

8. Первый запуск СнК «СКИФ» [9]

9. Собираем и исполняем «Hello,World» на СнК «СКИФ» [10]

10. Сборка SBL, DDRINIT, TF-A и U-Boot [11]

11. Прошиваем SBL загрузчик во flash память на порту QSPI0 [12]

12. Загрузка SBL и U-Boot [13]

13. Подготавливаемся к загрузке ОС AltLinux [14]

15. Просмотр основных параметров системы [16]

16. Проблема с архитектурным таймером [17]

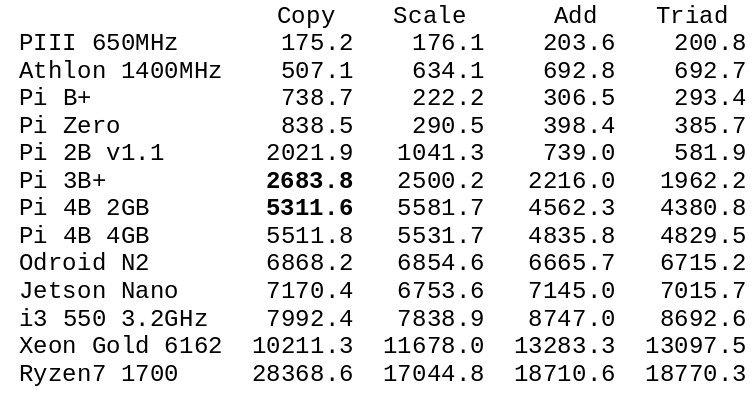

17. Тест производительности подсистемы памяти [18]

18. Тест производительности CPU [19]

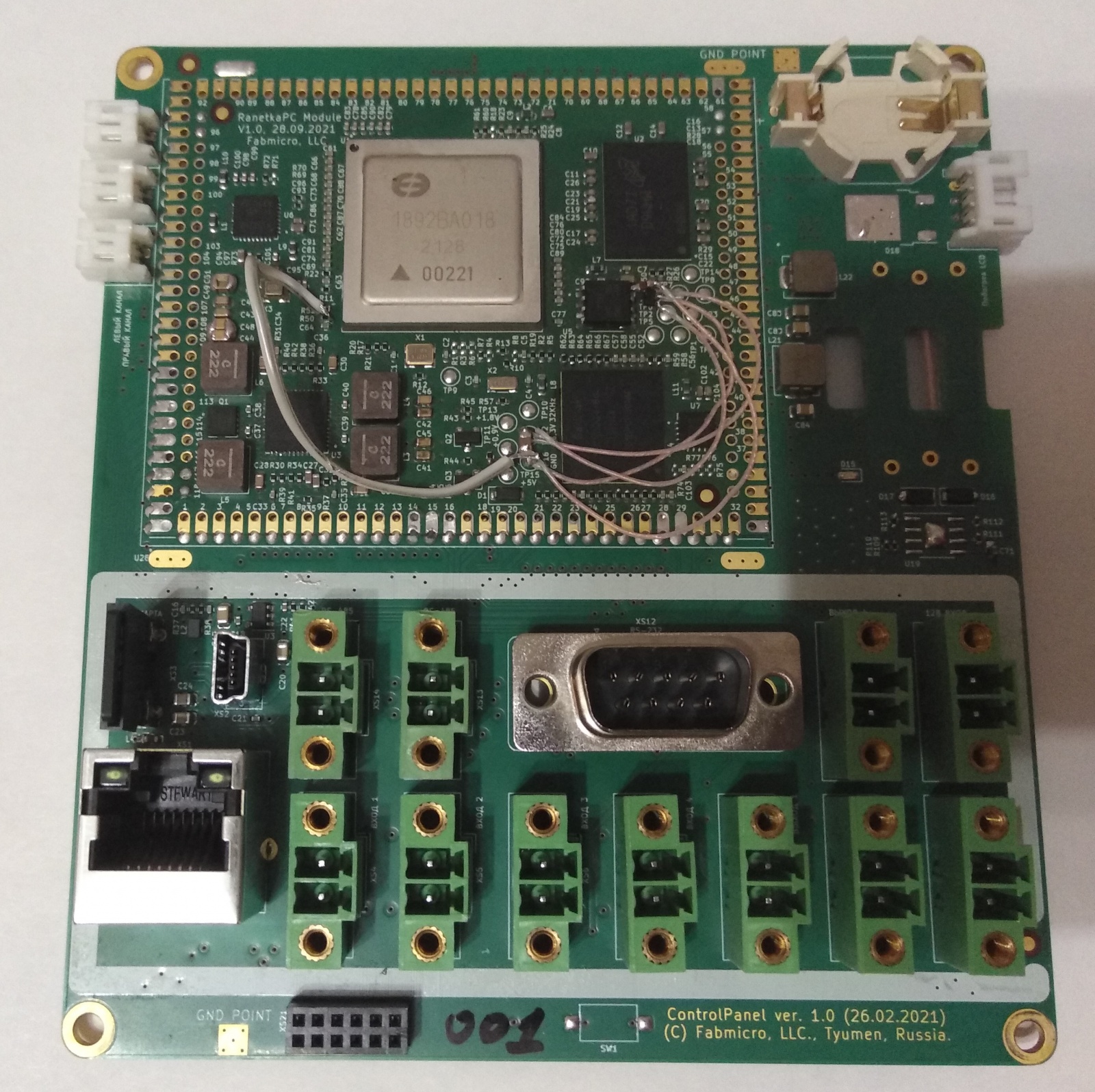

19. Устройство процессорного модуля «RanetkaPC» [20]

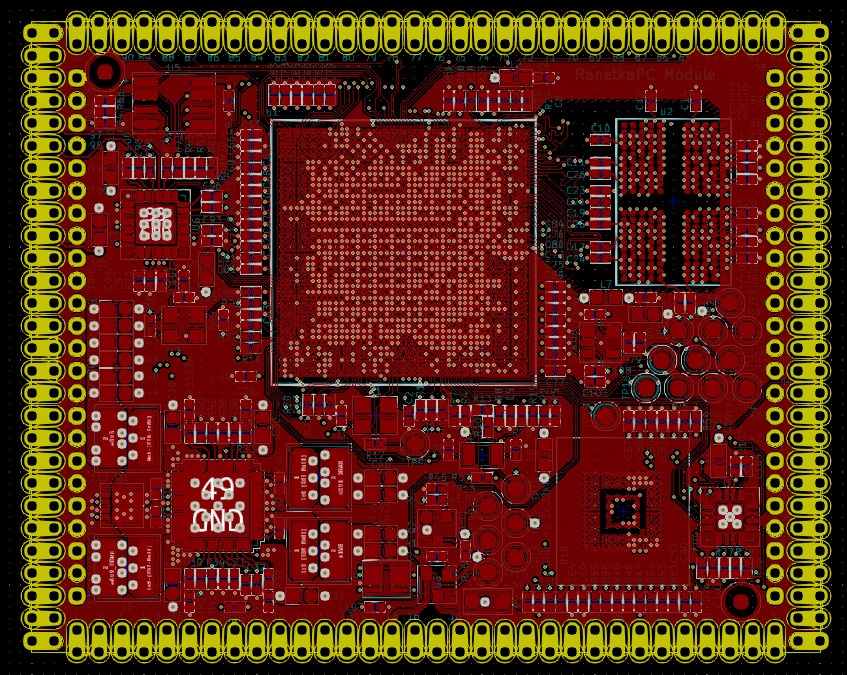

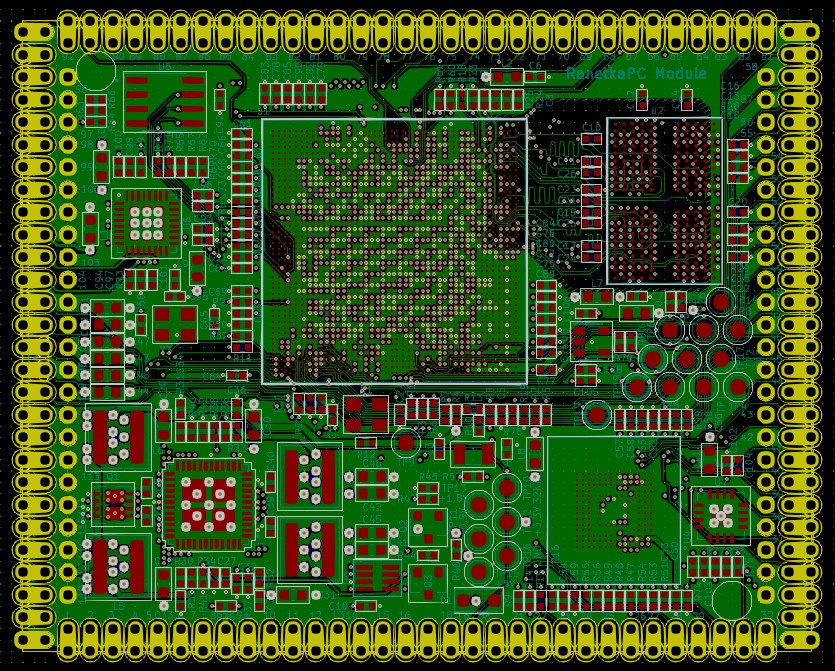

20. Разработка печатной платы процессорного модуля «RanetkaPC» [21]

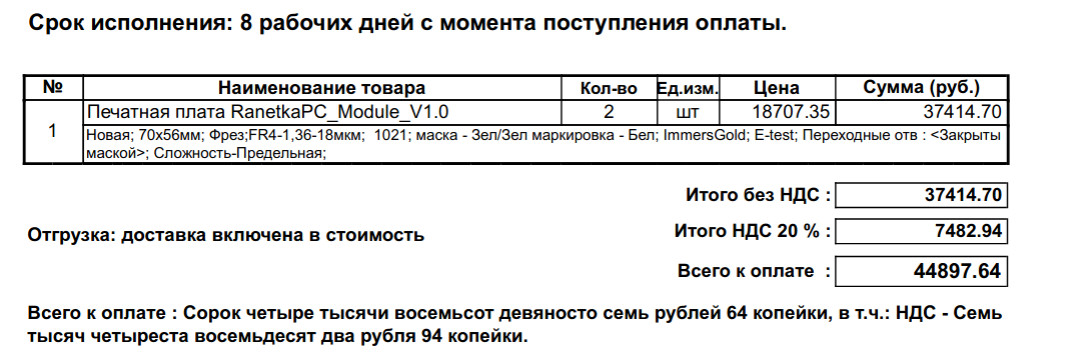

21. «Анбоксинг» микросхем 1892ВА018 [22]

22. Финальная сборка процессорного модуля «RanetkaPC» [23]

23. Проблемы запуска процессорного модуля «RanetkaPC» и СнК «СКИФ» [24]

24. Перспективы [25]

I. Ссылки на ресурсы по микросхеме 1892ВА018 «СКИФ» и процессорному модулю «RanetkaPC» [26]

1. Вступление

В первой половине 2021 года в РФ резко обострились дебаты на тему импортозамещения, инициированные рядом изменений внесенных ранее в декабре 2020г в постановление N719 [27] относительно закупок вычислительной техники, и бурно обсуждаемых на различных площадках и IT-форумах, таких как Elbrus Tech Day [28], YADRO Лекторий [29], а так же у ряда популярных блогеров. Основной посыл нововведений состоял в том, что вся вычислительная техника, закупаемая за бюджетные средства, должна иметь в основе микропроцессор, разработанный или произведенный в России или имеющий статус такового. Насколько такое решение Правительства годное и исполнимое — тема отдельного разговора, которую я не хотел бы сейчас затрагивать. Так или иначе, мы, в нашей небольшой компании, пришли к выводу, что данное решение Правительства может приоткрыть пусть не окно, но хотя бы форточку возможностей для мелких разработчиков электроники, которым является наша компания. Имея за плечами опыт разработки изделий [30] на основе импортных (в основном китайских) систем-на-кристалле, мы решили, что на рынке могут быть востребованы одноплатные ПК, аналогичные Raspberry Pi и выполненные на отечественном СнК, по возможности близкие по габаритам и pin-to-pin совместимые с «малиной», а также процессорные модули, устанавливаемые на несущую плату, позволяющие упростить разработку конечного изделия и вынести сложную топологию за его границы.

В данном случае процесс разработки мы решили начать именно с процессорного модуля, так как у нас уже имелся ряд изделий, построенных по модульному принципу, в которых процессорный модуль на отечественном СнК может быть применен с пользой. По мимо этого, разработать и отладить модуль значительно легче, чем конечное изделие, а затраты на изготовление печатных плат инженерных образцов модуля существенно ниже.

Этому проекту мы дали название «RanetkaPC». «Малина» есть, «бананы», «ананасы» и «апельсины» — тоже. Пусть будет еще и «ранетка». К тому же, ранетка — пожалуй самое популярное плодовое растение в нашем городе (Тюмень), все центральные улицы города засажены им еще со времен СССР, что очень приятно радует глаз, особенно по весне, когда цветут ранетки [31], и осенью — когда деревья покрываются сочными плодами.

2. Проблема выбора

Первым делом встал вопрос — на каком СнК проектировать такое изделие и какова будет его конечная цена. Не секрет, что отечественные производители микроэлектроники не стесняются брать за неё приличные деньги, и на то есть веские основания, но очень хотелось сделать изделие доступным.

На слуху уже были Эльбрусы с их самобытной VLIW архитектурой, Байкал BE-T1000 на ядрах MIPS и недавно вышедший BE-M1000 с восемью ядрами ARM Cortex-A57. Так же в прессе просачивалась информация о ряде СнК от таких производителей, как НТЦ Модуль, «Миландр», НИИСИ, НИИЭТ и НТЦ «Элвис». В целом, какой-то выбор предоставлялся.

СнК Эльбрус-2С3 отпал сразу — общая аура секретности вокруг технической документации на эти процессоры и проприетарные средства разработки отбивали всякое желание иметь дело с его производителем. К тому же заявленная потребляемая мощность в 30Вт была слишком высока для нашего одноплатного ПК.

СнК Байкал BE-T1000 на архитектуре MIPS оказался слаб в части производительности. А вот Байкал BE-M1000 неожиданно удивил — 68000 пунктов по Coremark. Правда потребляет он при этом те же 30Вт что и Эльбрус-2С3. Теоретически, с этим можно жить, если правильно спроектировать охлаждение. Мы запросили КП и даташит на этот СнК у производителя. КП получили быстро, один «камень» при штучных заказах нам предлагался по 30 000 рублей с НДС. Однако с получением технической документации и референс-дизайна на это изделие вышла неурядица — производитель микросхемы «Байкал Электроникс» попросил нас подписать договор о не разглашении (NDA), на что получил наш отказ. Многие скажут, что NDA — это нормальная общемировая практика. Да, это так, и это один из сдерживающих факторов развития Open Source Hardware. Подписав тогда этот NDA, я бы сейчас не смог написать эту статью. Байкал — не наш выбор.

Стали перебирать и перечитывать информационные листки от других, менее раскрученных производителей. На мой взгляд, неплохо выглядят некоторые СнК от НТЦ Модуль. Например, СБИС 1879ВМ8Я [32], содержащий 4 ядра ARM Cortex-A5, работающих на частоте 800МГц, и кучу неройровычислителей NMC4. Продукция ПКК «Миландр» больше походит на микроконтроллеры для embedded приложений и к нашей задаче оказалась слабо применима.

В какой-то момент мне попалась информация про СнК 1892ВМ14Я [33] производства НЦТ «Элвис» — два ядра ARM Cortex-A9, работающих на частоте 816МГц, очень близок к Allwinner A20/T2, на котором у нас уже есть свой процессорный модуль. В этом СнК содержится вся необходимая нам периферия: GPU Mali, два порта SD/MMC, MIPI DSI, MIPI CSI, аппаратные кодеки для видео. Но самое главное — на сайте доступна вся документация, SDK и готовые сборки Linux, есть репозиторий на Github-е. В общем, мы запросили КП и начали обговаривать технические моменты. В ответ на запрос КП, мне перезвонил представитель «Элвиса» и предложил рассмотреть еще пару перспективных (находившихся в разработке) СнК их компании: 1892ВА018 «СКИФ» [34] и 1892ВМ248 «RoboDeus» [35]. Оба эти СнК из серии «Multicore» представляют из себя гетерогенные многоядерные вычислители, т.е. содержат вычислительные ядра как общего назначения, так и некоторое количество специализированных, в том числе — DSP ядер. Так СнК «RoboDeus» содержит четыре MIPS64 ядра работающих на частоте 1.5ГГц + четыре ядра DSP Elcore-50 и позиционируется производителем для средств видео-аналитики и нейросетевых вычислений. СнК «СКИФ» содержит четыре ARM Cortex-A53 на частоте до 2.0 ГГц + два DSP Elcore-50 и предлагается для использования в мобильных средствах связи - смартфоны, планшеты, цифровые радиостанции. Оба СнК содержат весь спектр «стандартной» для таких решений периферии — GPU, VPU, DSI, CSI, SPI, I2C, I2S, PCIe и т.д. В Скифе предлагается еще отдельный вычислитель для SDR (Software-Define Radio) с двумя интерфейсами JESD 204B, с помощью которого подключаются высокоскоростные ЦАП и АЦП, что позволяет реализовывать различные протоколы радиосвязи, в том числе WIFI и GNSS в софте.

Обсудив и взвесив различные варианты, мы решили остановиться на микросхеме 1892ВА018 СнК «СКИФ». Запросили и получили на неё коммерческое предложение — цена за один «камень» на июль 2021 года составляла 23 000 рублей с НДС. Срок начала отгрузки — октябрь 2021г. «Руководство» на 2100 с плюсом страниц и референс-дизайн платы «MCOM03 Bring-Up-Board» нам прислала служба технической поддержки «Элвиса» без подписания каких-либо NDA. Сборки начального загрузчика, U-Boot и ядра Linux для MCOM-03 [36] доступны на Github-е.

*MCOM03 — кодовое название микросхемы 1892ВА018, используется в «Руководстве», в схемотехнике и программном обеспечении.

3. Система-на-кристалле 1892ВА018 «СКИФ»

И так — встречайте, СнК «СКИФ» производства НТЦ «Элвис». С подробным описанием технических характеристик этого СнК можно ознакомиться на сайте НТЦ «Элвис» по адресу: ссылка на сайт [34]. Ниже я позволю себе привести только некоторые, на мой взгляд самые интересные, из них:

-

Центральный процессор (CPU):

-

4-х ядерный кластер ARM Cortex-A53 с тактовой частотой 1,2 ГГц (2,0 ГГц макс — прим автора); L1 кэш - 32 кбайт, L2 кэш - 1 Мбайт;

-

контроллер прерываний ARM GIC500;

-

128-бит SIMD/FPU сопроцессоры NEON.

-

-

Доверенный контур и служебная подсистема:

-

ядро RISC0 32 бит MIPS, 600 МГц;

-

механизм доверенной загрузки.

-

-

Цифровой блок для связных и мобильных приложений:

-

ядро RISC1 32 бит MIPS, 600 МГц;

-

высокопроизводительное сдвоенное DSP ядро с тактовой частотой ядра 600 МГц:

-

навигационное ядро GNSS поддержка 4 стандартов: ГЛОНАСС/GPS/BeiDou/GALILEO;

-

поддержка функций для реализации алгоритмов на базе нейросетей;

-

цифровые фильтры и акселераторы;

-

накристальная память 2 Мбайт;

-

-

Мультимедиа и обработка видео:

-

ISP ядро:

-

поддержка 2 потоков 4К @ 30 или 1 потока 4К @ 60;

-

-

Видеопроцессор VPU ARM Mali V61:

-

HEVC/H.264;

-

формат данных: 10/8 бит 4.2.2 и 4.2.0;

-

поддержка 1 потока 4К @ 60 или 2 потоков 4K @ 30;

-

поддержка JPEG/MPEG.

-

-

Графический процессор GPU PowerVR Series8XE GE8300:

-

тактовая частота 550 МГц;

-

поддержка OpenGL, OpenCL, OpenVG;

-

OpenCL API;

-

поддержка Vulkan;

-

-

-

Интерфейсы:

-

2 контроллера DDR памяти: DDR3/ LPDDR3/ DDR4/LPDDR4, 32 бита, 3200 Мбит/с на каждую линию с поддержкой ECC;

-

2 контроллера PCIe: конфигурация линий 2 x 4; поддержка PCI Express 3.0 скорость на линию 8 ГТ/с;

-

2 контроллера Ethernet 1 Гбит/с;

-

2 контроллера JESD 204B, 4 линии, до 12,5 Гбит/с на линию;

-

2 контроллера USB 3.0 DRD;

-

2 контроллера SD/eMMC 4.5;

-

порт видеовывода для подключения дисплеев: MIPI DSI или RGB, поддержка разрешения 4К@30, поддержка HDR;

-

2 контроллера QuadSPI NOR Flash (XiP);

-

сторожевой таймер WDT.

-

-

Технология изготовления: КМОП, 28 нм, процесс TSMC.

-

Температурный диапазон: -60...+85 °C.

-

Встроенные датчики температуры и напряжения.

-

Типовое потребление: до 5-7 Вт.

-

Контроллер гибкого управления энергопотреблением, поддержка батарейного питания и режима сна.

-

Основные напряжения питания: 3.3 В/1.8 В/0.9 В.

-

Тип корпуса: 1936 HFCBGA, 23 мм x 23 мм, шаг по выводам 0,5 мм.

Обратите внимание на тип корпуса этой микросхемы: HFCBGA с числом выводов 1936 и шагом 0.5мм. К этому моменту мы еще не имели опыта проектирования плат, содержащих микросхемы с таким количеством выводов. Для того, чтобы «выйти» из под такой микросхемы нам потребовалось 10 слоёв металлизации с шириной/зазором проводника 0.1/0.075мм и диаметром переходного отверстия 0.3/0.1мм, но подробнее об этом читайте в главе 20. Разработка печатной платы процессорного модуля «RanetkaPC». А сейчас предлагаю немного подробнее рассмотреть внутренности микросхемы 1892ВА018 СнК «СКИФ».

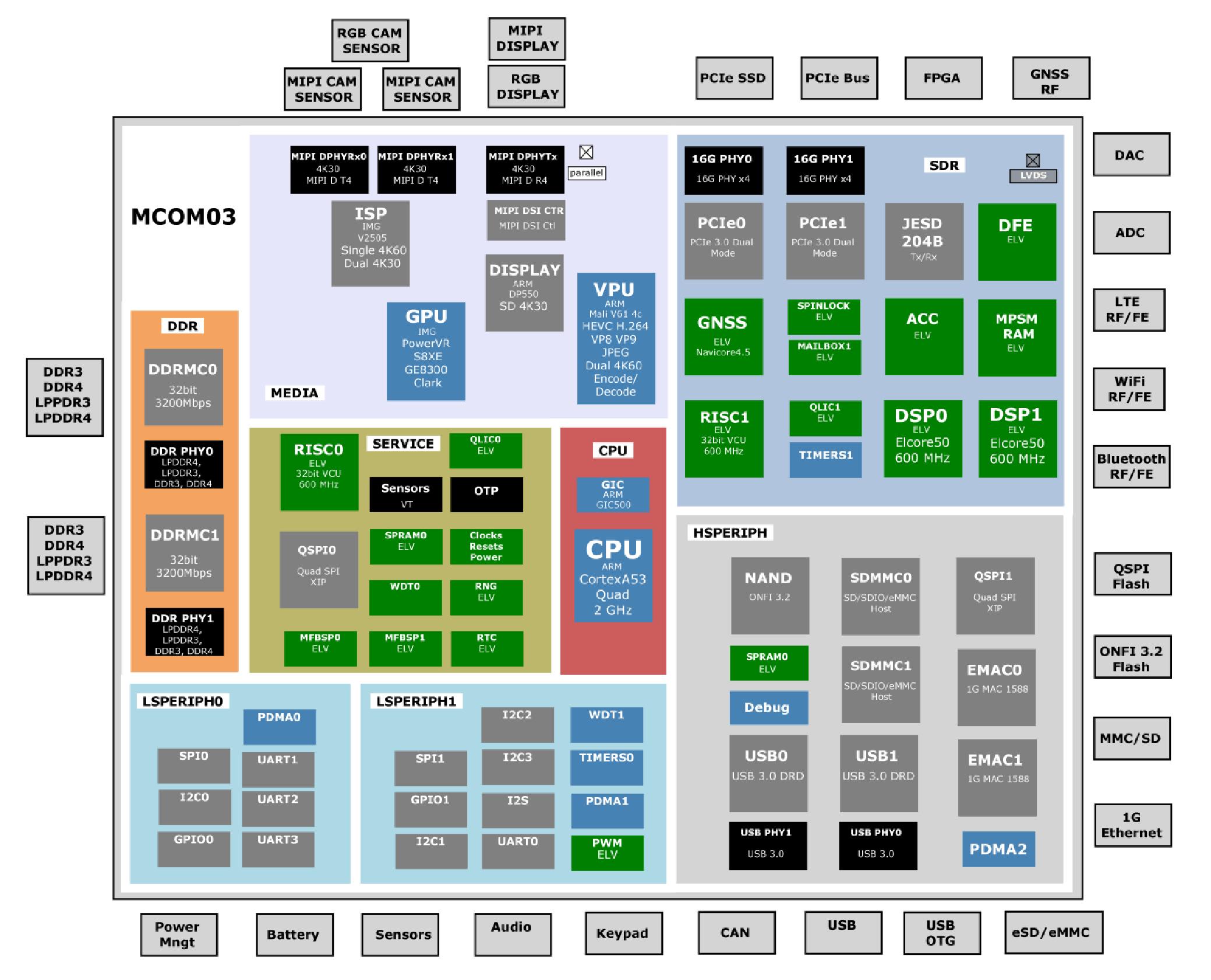

4. Внутренняя структура 1892ВА018 СнК «СКИФ»

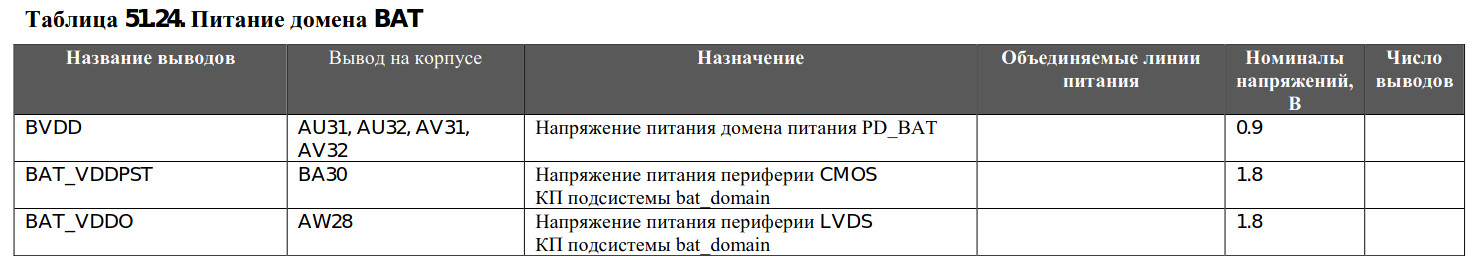

Рассмотрим структуры микросхемы 1892ВА018 СнК «СКИФ» (MCOM03) которая проиллюстрирована на рисунке 2 ниже.

Видно, что все функциональные блоки СнК объединены в несколько групп, которые, называются «подсистемами» (subsystems или subs). Каждая подсистема имеет свой набор управляющих и конфигурационных регистров, а так же свой набор тактирующих сигналов, свой сигнал сброса, одну или несколько линии питания. Выделяются следующие подсистемы:

-

служебная подсистема (service_subs);

-

подсистема SDR (sdr_subs);

-

подсистема портов динамической памяти (ddr_subs);

-

подсистема центрального процессора (cpu_subs);

-

подсистема мультимедиа (media_subs);

-

подсистема высокоскоростной периферии (hsperiph_subs);

-

подсистема низкоскоростной периферии #0 (lsperiph0_subs);

-

подсистема низкоскоростной периферии #1 (lsperiph1_subs).

Базовой подсистемой микросхемы, т.е. подсистемой ответственной за формирование опорных частот, сброса, управления питанием для других подсистем и содержащей логику и регистры системных настроек микросхемы, а также блоки, работающие при старте и начальной загрузке микросхемы, является служебная подсистема (service_subs).

Система коммутации верхнего уровня, в виде набора соединений и коммутаторов, логики и регистров их настройки, логики формирования частот и сброса также выделена в отдельную подсистему.

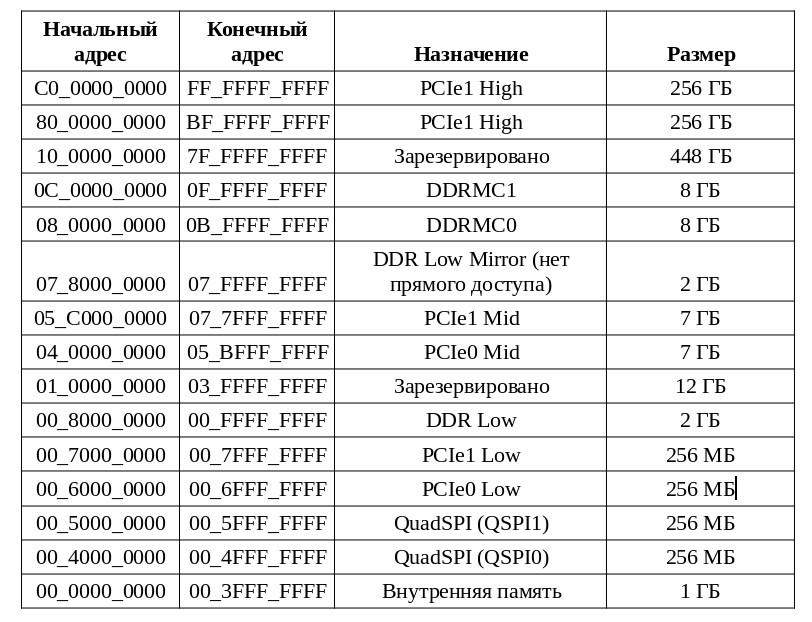

Карта распределения адресного пространства микросхемы СнК «СКИФ» (MCOM03) приведена в таблице ниже.

Из таблицы 1 видно, что СнК может адресовать 16 ГБ синхронной динамической памяти по 8 ГБ на каждый их двух каналов DDRMC0 и DDRMC1. Согласно «Руководству», каналы DDR поддерживают режим работы с чередованием (interleaving) для ускорения доступа к памяти.

Так же следует упомянуть, что часть аппаратных блоков микросхемы может адресовать только 32 бита. Для таких устройств можно настроить смещение физического диапазона 4ГБ (0x00_0000_0000 – 0x00_FFFF_FFFF), адресуемого устройством, в области памяти старше адреса 0x00_FFFF_FFFF.

С адреса 00_0000_0000 по 00_0000_FFFF находится область статической памяти SPRAM0 размером 64КБ доступной для загрузки и исполнения программ на ядре RISC0.

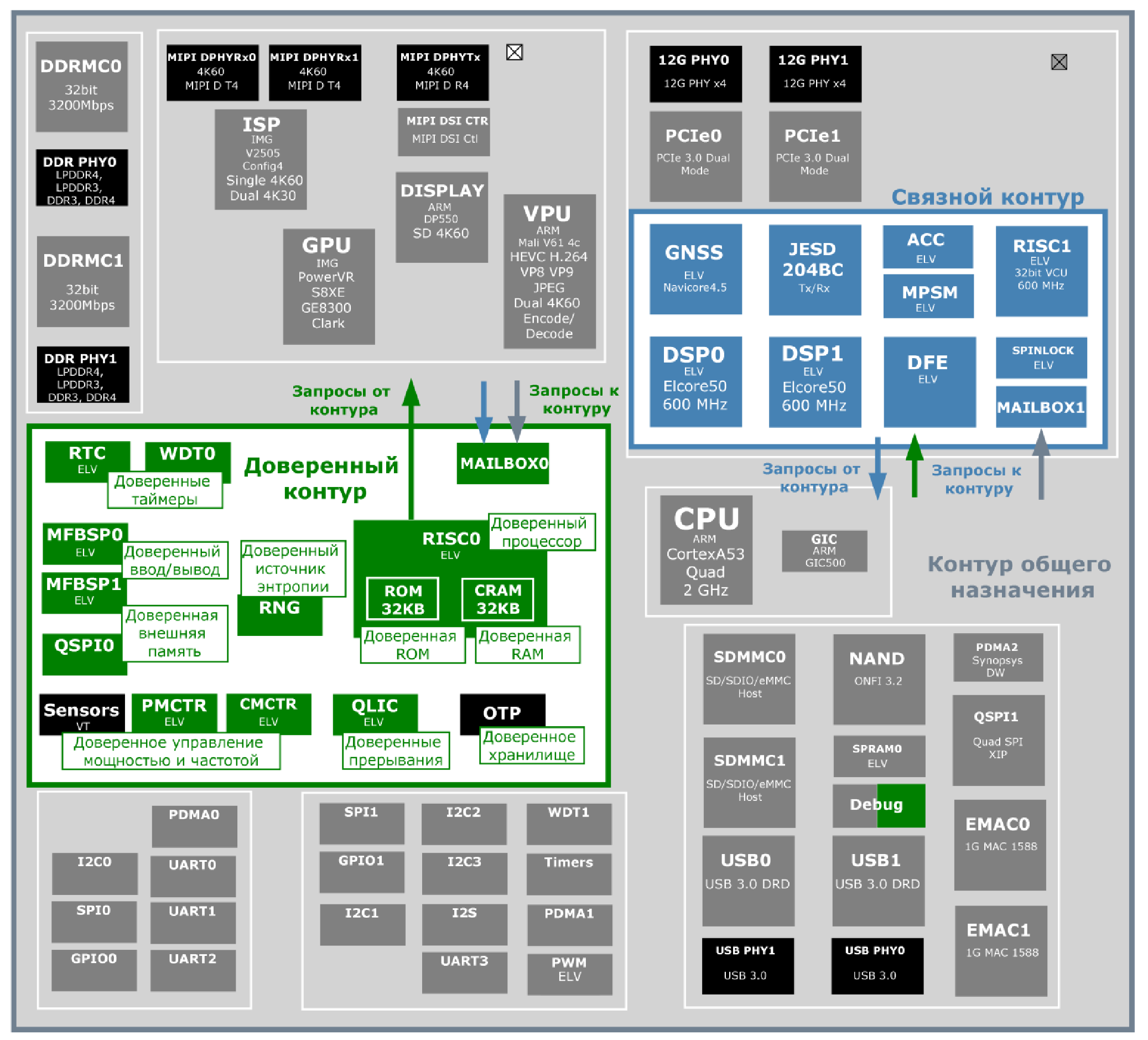

5. Система обеспечения безопасности микросхемы 1892ВА018 СнК «СКИФ»

Важной и интересной особенностью микросхемы 1892ВА018 СнК «СКИФ» является система обеспечения безопасности. По мимо того, что микросхема аппаратно совместима с технологией ARM TrustZone и следует концепции Trusted Execution Environment (TEE), в ней предприняты дополнительные меры.

Все подсистемы микросхемы поделены между тремя контурами безопасности:

-

«доверенный» - во главе с ядром RISC0 (MIPS) обеспечивает процесс начальной загрузки, а так же контроль доступа между подсистемами. В «доверенном» контуре содержится «доверенное хранилище ключевой информации» (OTP), ключи из которого могут быть использованы для верификации и загрузки доверенной операционной системы, которая в свою очередь обеспечивает загрузку операционной системой общего назначения и контроль над ней.

-

«связной» - во главе с ядром RISC1 (MIPS) содержит специализированные вычислители, в том числе два ядра DSP Elcore-50, вычислитель для GNSS и интерфейс высокоскоростных ЦАП/АЦП. Данный контур исполняет связное программное обеспечение.

-

«контур общего назначения» - содержит четыре вычислительных ARM ядра CPU0-3 общего назначения и всю остальную периферию. Является аппаратной базой для операционной системы общего назначения (Linux, Android, и т.д.).

Ниже приведена схема разделения подсистем на контуры, показаны возможные варианты взаимодействия между ними.

Взаимодействие между контурами осуществляется посредством механизма «почтовых ящиков» (MAILBOX-ов). Почтовые ящики представляют собой набор набор FIFO. При необходимости передать сообщение, одна из сторон записывает сообщение в соответствующее FIFO, а другая считывает из него. При появлении данных во входном FIFO почтового ящика, вычислительное ядро, обслуживающее данный контур, получает сигнал прерывания, по которому производится считывание сообщения. Ответное сообщение помещается в выходное FIFO этого же почтового ящика. При этом (цитирую «Руководство»):

-

Любые запросы в «доверенный» контур от «общего» или «связного» контура разрешены только через доверенный почтовый ящик MAILBOX0.

-

Любые запросы в «связной» контур от «общего» контура разрешены только через почтовый ящик MAILBOX1.

-

Запросы от «доверенного» контура имеют прямой неограниченный доступ в «связной» и «общий» контур.

-

Запросы от «связного» контура имеют прямой неограниченный доступ в «общий» контур.

В системе коммутации микросхемы СнК существует несколько уровней доступа и, соответственно, уровней запросов. В порядке убывания уровня доступа:

-

Доверенный уровень (trusted) – запросы от «доверенного» контура и внутри него от его компонентов.

-

Связной уровень (sdr) – запросы от «связного» контура и внутри него от его компонентов.

-

Безопасный уровень (secure) – запросы от компонентов «общего» контура, в рамках архитектуры ARM TrustZone помеченных как безопасные.

-

Общий уровень (non-secure) – запросы от компонентов «общего» контура, в рамках архитектуры ARM TrustZone помеченные как небезопасные.

Области памяти имеют такие же уровни по доступу, отмечающие, какого уровня запросы допустимы к этой области. Более высокий уровень доступа для запроса означает, что для него допустимы обращения к областям памяти с уровнями равными, либо ниже его. Т.е. для запросов trusted допустимы обращения к областям trusted, sdr, secure и non-secure, для запросов sdr к областям sdr, secure, non-secure и т.д.

Для областей памяти существует также особый признак, касающийся доступа – securable, это означает что области памяти, изначально по сбросу, имеющей другой уровень доступа можно присвоить уровень доступа secure. Это работает как в случае повышения уровня, когда области памяти с уровнем доступа non-secure можно сделать secure, так и в случае понижения уровня – некоторые области доверенного (trusted) и связного (sdr) контура можно сделать доступными для secure обращений.

Отметим, что микросхема 1892ВА018 поддерживает режим загрузки, при котором все эти дополнительные меры обеспечения безопасности могу быть отключены подачей логической «1» на специальный вывод VS_EN микросхемы.

Авторизация загрузчика (проверка электронной подписи) на данном СнК по умолчанию отключена. Включение авторизации осуществляется подачей логической «1» на вывод BS_EN микросхемы.

Наша промежуточная цель на этапе «подъема» разработанной нами платы процессорного модуля «RanetkaPC» является загрузка и запуск ОС Linux. Образ рабочей сборки AltLinux был предоставлен нам службой технической поддержки «Элвиса», но вот сам процесс загрузки оказался совсем не тривиален и с ним пришлось детально разобраться.

6. Загрузка микросхемы 1892ВА018 СнК «СКИФ»

Процесс загрузки микросхемы 1892ВА018 радикально отличается от всего того, с чем мы имели дело ранее. Основное отличие состоит в том, что первым, после подачи питания и снятия состояния RESET, всегда запускается служебное MIPS ядро RISC0 из доверенного контура. Это ядро исполняет т.н. первичный загрузчик, который находится в встроенной ROM (32К) памяти расположенной в доверенном контуре и «прошитой» в процессе производства микросхемы, либо сразу переходит к исполнению загрузчика из NOR flash, если выбран соответствующий режим. Остальные вычислительные ядра в этом момент остановлены и обесточены. В задачи первичного загрузчика входит инициализация остальных вычислительных ядер, инициализация (трэйнинг) SDRAM, поиск и размещение загрузчика следующего уровня и размещение его в SDRAM, запуск вычислительного ядра общего назначения.

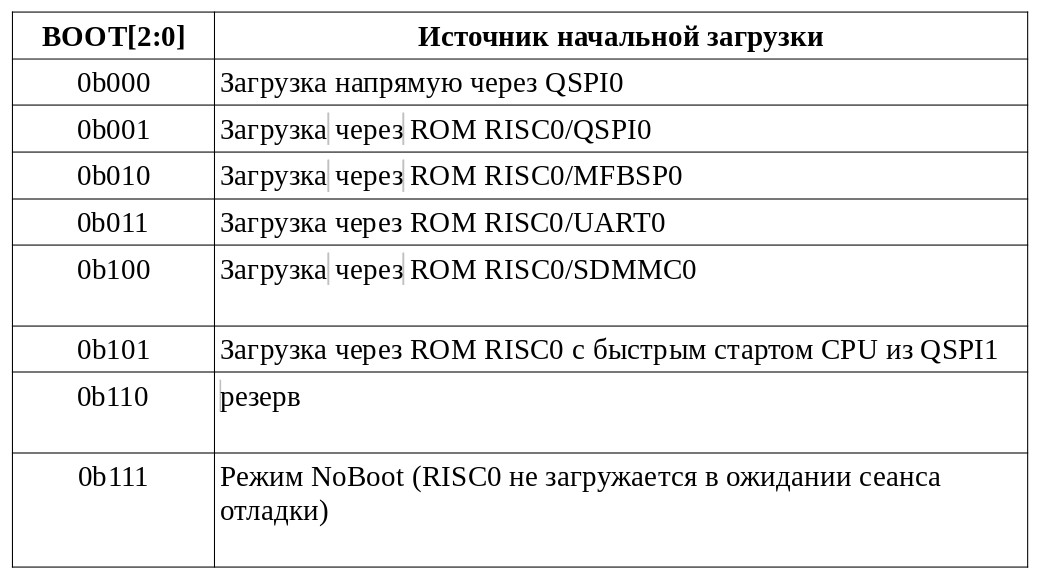

Следующая особенность — это выбор способа загрузки. Микросхема 1892ВА018 имеет три служебные линии BOOT[0:2], выведенные на корпус для задания режима загрузки. Логические состояния по входу этих линий определяют дальнейшее поведение ROM загрузчика, за исключением режима 0b000. В таблице ниже приведены все режимы (варианты) загрузки.

Если в момент подачи питания на входных линиях (пинах) микросхемы на сигнальной линии BOOT2 присутствует логический «0», на BOOT1 присутствует «0» и на BOOT0 присутствует «0», то выбран режим 0b000. В этом режиме ядро RISC0 начинает исполнение с физического адреса 0x00_4000_0000. Из таблицы распределения адресного пространства (см. выше) можно увидеть, что с этого адреса располагается область памяти QSPI0 - нулевой порт QuadSPI NOR Flash памяти. Как правило, микросхемы NOR flash памяти с интерфейсом QSPI обладают возможностью исполнения кода прямо из изнутри, то есть без копирования кода в статическую или динамическую память. Эта особенность называется XiP (eXecution in Place). Другими словами, в режиме 0b000 загрузчик исполняется прямо из flash памяти, минуя ROM.

Если в момент подачи выбран любой другой режим, то RISC0 всегда передает управление загрузчику вшитому в ROM, который располагается по адресу 0x00_1fc0_0000. Этот загрузчик так же анализирует состояние сигнальных линий BOOT[2:0] и выполняет соответствующую процедуру загрузки.

Особый интерес представляет режим загрузки 0b011 - «Загрузка через ROM RISC0/UART0». В данном режиме, после подачи питания, ядро RISC0 исполняет код из ROM, программа которого переходит в командный (CLI) режим, т.е. ожидает ввода команды из последовательного порта UART0 — классический «монитор». Простейший интерпретатор команд «монитора» позволяет выполнить ряд операций:

-

вывести дамп области памяти, заполнить область значением;

-

загрузить блок из UART0 и поместить его в память;

-

передать управление по адресу.

Данный режим «монитора» интересен тем, что имея в распоряжении только подключенный последовательный порт и линии питания, можно протестировать СнК и даже загрузить в него и исполнить свою собственную «bare metal» программу на MIPS ядре RISC0, при этом загрузка кода программы осуществляется в специализированный блок памяти SPRAM0, находящийся по адресу 0x00_0000_000 и размером 64K. Загруженной таким образом программе доступно 32К статической памяти SRAM расположенной с адреса 0x00_1fa0_0000.

Далее я покажу, как мы воспользовались этой возможность для тестирования СнК при первом запуске нашего изделия и это сильно упростило нам работу. Хочу выразить отдельную благодарность инженерам НТЦ «Элвис» за такую полезную возможность!

7. Загрузка СнК «СКИФ» — более подробно

Рассмотрим немного более подробно режим загрузки 0b000 - «Загрузка напрямую через QSPI0» и проследим весь процесс загрузки до запуская ядра ОС общего назначения (ядра ОС Linux).

Как я уже отмечал выше, в этом режиме при подаче питания первым делом запускается MIPS ядро RISC0, которое начинает исполнять код с физического адреса 0x00_4000_0000 — это адресное пространство аппаратно маппируется на содержимое NOR flash памяти, подключенной к порту QSPI0. В NOR flash памяти должен быть размещен загрузчик SBL (Simple Boot Loader), состоящий их последовательно идущих друг за другом нескольких программных модулей:

-

первым располагается сам SBL — код для MIPS32;

-

далее следует DDRINIT — код для AArch64;

-

далее следует TF-A — код для AArch64;

-

и завершает цепочку U-Boot — код для AArch64.

SBL (Simple Boot Loader), как следует из названия, представляет собой примитивный загрузчик, в задачи которого входит инициализация DDR контроллеров, после чего SBL помещает в SDRAM код TF-A и U-Boot и запускает ARM ядро. SBL исполняясь на MIPS производит следующие действия:

-

Инициализирует основные сигналы тактирования и поднимает частоту для RISC0 до 1.2ГГц;

-

Подает питание на контроллеры DDR памяти и на ARM ядра;

-

Копирует код модуля DDRINIT из QSPI0 в статическую память SPRAM0 которая маппируется на адресное пространство 0x00_0000_0000, эта память внутри ядра RISC0 видна с адреса 0x80000000;

-

Стартует ARM ядро CPU0 таким образом, что это ядро начинает исполнять код в SPRAM0, где находится DDRINIT;

-

Дожидается результата исполнения DDRINIT на CPU0 и если он успешный, то -

-

Копирует из QSPI0 в SDRAM начиная с физ адреса 0x80000000 код модуля TF-A;

-

Копирует из QSPI0 в SDRAM начиная с физ адреса 0x80080000 код модуля U-Boot;

-

Перезапускает CPU0 и зависает в вечном цикле, в то время как CPU0 исполняет код TF-A, который в свою очередь передает управление коду U-Boot.

Тут следует отметить, что в конфигурациях вычислительных систем с межконтурной защитой, вместо SBL должно быть что-то более серьезное — то, что называется «доверенной операционной системой». Эта доверенная ОС на начальных этапах выполняет все те же функции, что и SBL, но после запуска TF-A переходит в режим контроля и обслуживания запросов от ОС общего назначения. К сожалению, в наше распоряжение такой операционной системы предоставлено не было, соответственно опробовать все прелести и тонкости этого механизма пока что не предоставилось.

DDRINIT - это программный модуль, который исполняясь на ARM ядре, производит загрузку начальных параметров в блоки управления контроллеров динамической памяти DDRMC0 и DDRMC1. После чего, DDRINIT последовательно инициирует процедуру тренировки и калибровки временных параметров физических трансиверов при работе с конкретными микросхемами DDR памяти (PHY training). Взаимодействие с контроллерами DDRMC0 и DDRMC1 производится через MAILBOX так, как ядро ARM и контролеры памяти находятся в различных контурах.

Для ускорения задачи, DDRINIT имеет возможность считать уже ранее рассчитанные калибровочные параметры из микросхемы EEPROM на шине I2C, если таковая предусмотрена, и передать их контроллерам.

TF-A или «ARM Trusted Firmware A» - это программный модуль распространяемый по лицензии BSD-3 одноименным консорциумом [37] во главе с ARM, Ltd., представляет собой референсную имплементацию системы защиты внутри ARM ядра. Если сильно не вдаваться в подробности, то основной смысла таков:

TF-A исполняясь на ARM ядре в режиме EL3 (Execution Level 3) — самый высокий уровень исполнения, имеет доступ к абсолютно всем аппаратным возможностям ARM. TF-A производит инициализацию служебных векторов прерываний и исключений, конфигурирует MMU таким образом, чтобы защитить (ограничить) доступ к ряду областей памяти и аппаратуре при исполнении кода работающего на пониженных уровнях (EL2, EL1, EL0), загружает и запускает свою (ARM-овскую) доверенную ОС, после чего запускает загрузчик ОС общего назначения U-Boot с пониженым EL2 (или EL1) уровнем исполнения. Таким образом U-Boot и ОС Linux функционируют уже с пониженным уровнем привилегий «под присмотром» доверенной ОС. Доверенные ОС нас пока не интересуют, по этому в TF-A оставим заглушку по умолчанию, которая стартует U-Boot.

Для желающих погрузиться в этот удивительный мир уровней исполнения и безопасности ARM, приведу ссылку на документ под названием «ARM Trusted Firmware Design [38]».

U-Boot, популярный загрузчик ОС общего назначения, своего рода стандарт «de-facto» в embedded и мобильной индустрии. Задача U-Boot — поиск, загрузка и запуск ядра ОС общего назначения (в нашем случае ОС Linux) и конфигурационного файла к нему (Device-Tree). U-Boot обладает гибким скриптовым языком, умеет работать с сетью и множеством различной периферии, в том числе SPI, I2C, MMC/SD карты, NAND и NOR Flash и даже SATA. Честно говоря, возможности последних версий U-Boot настолько многообразны, что U-Boot можно рассматривать как однозадачную ОС общего назначения с сетевым стеком и некоторыми зачатками графического интерфейса.

8. Первый запуск СнК «СКИФ»

Более подробно аппаратное устройство разработанного нами процессорного модуля «RanetkaPC» на базе СнК «СКИФ» я рассмотрю ниже. Здесь же упомяну, что модуль был спроектирован таким образом, чтобы максимально облегчить его запуск: для включения модуля достаточно подвести сигналы GND, TX и RX порта UART0 от модуля к «USB2Serial» преобразователю, а так же подать напряжение +5V от источника питания на соответствующий вход модуля. Даже если плата модуля имеет какие-то дефекты монтажа, СнК «СКИФ», получив питание, перейдет в режим загрузки 0b000, т.е. начнет исполнение кода SBL из QSPI0, а в терминале мы сможем наблюдать диагностический вывод от программных модулей SBL.

Но как начать запуск, если во Flash памяти процессорного модуля, который только что вышел из печи, отсутствует какой либо код для данного СнК? Здесь нам и придет на помощь режим загрузки 0b011 - «Загрузка через ROM RISC0/UART0». Напомню, что в этом режиме СнК стартует программу «монитор» из своего ROM прошитого при его производстве, программа переходит в режим командной строки и начинает общаться с разработчиком через порт UART0.

Запаяем перемычки BOOT[2:0] на плате процессорного модуля таким образом, чтобы выставить режим 0b011, подключим к рабочей машине USB2Serial преобразователь и подсоединим его к модулю, запустим утилиту эмуляции терминала cu (далее я буду использовать утилиту cu(1) — «call Unix» из стандартной поставку ОС FreeBSD) с параметрами порта 115200 8N1 и подадим питание 5V на модуль. Вот что мы увидим в терминале:

rz@butterfly:/home/rz/mcom03 $ cu -l /dev/ttyU0 -s 115200

RnD Center "ELVEES", JSC

MCom-03, Bootrom rev.1.0

#Введем команду help и посмотрим, каким инструментарием мы располагаем:

#help

List of commands:

help

dump

set

run

boot

sdopen

mfbspopen

qspiopen

devdump

devsetp

devcommit

otpdump

otpcommitПроверим, доступна ли нам SPRAM0, попробуем считать её содержимое с адреса 0x80000000:

#dump 0x80000000

0x80000000: 0xcfcdfeef, 0xf7f9dfaf, 0x4c516ddb, 0x3e120fce

0x80000010: 0x5be2d54f, 0xfedc7dde, 0x2f0a382b, 0x3e697820Как видно, dump возвращает нам какие-то данные. Попробуем изменить содержимое одной ячейки памяти и еще раз считать её:

#set 0x80000000 0xaabbccdd

#dump 0x80000000

0x80000000: 0xaabbccdd, 0xf7f9dfaf, 0x4c516ddb, 0x3e120fce

0x80000010: 0x5be2d54f, 0xfedc7dde, 0x2f0a382b, 0x3e697820Видим, что данные записываются в память и успешно считываются обратно.

Тут встает логичный вопрос: каким образом область памяти SPRAM0, которая расположена с физического адреса 0x00_0000_0000 размером 64КБ, стала доступна ядру RISC0 по 32-битному адресу 0x80000000. Я задал его в службу технической поддержки и ниже привожу ответ инженера «Элвиса», цитирую:

В режиме загрузки 0b011 процессор (имеется в виду RISC0) находится в режиме Kernel. При этом если три старших бита виртуального адреса равны 0b100 , выбирается 32-разрядное виртуальное адресное пространство kseg0. Это область размером 512 MB, которая расположена внутри границ, определяемых адресами 0x8000_0000 и 0x9FFF_FFFF. Ссылки к kseg0 не отображаются, а физический адрес получается вычитанием 0x8000_0000 из виртуального адреса. Таким образом при обращении по виртуальному адресу 0x8000_0000 обращение идет в физический адрес 0x00_0000_0000, что соответствует стартовому адресу памяти SPRAM0.

Вспомним это, когда будем загружать нашу тестовую программу «hello-world» и прошивать NOR flash.

Теперь посмотрим, что содержится в OTP памяти, для этого воспользуемся командой otpdump. OTP — это память в которой сохраняются ключи для верификации загрузчиков и прочая сопутствующая информация, связанная с безопасностью микросхемы. Мы не собираемся использовать эту возможность, но знать о ней не помешает.

#otpdump

OTP [virtual 0x9fa00000]:

0x00: ZeroCount : 0x0000 (0)

0x02: Flags : 0x0000

[ ForceSign : 0 ]

[ ForceEncrypt : 0 ]

[ DisableLog : 0 ]

[ EnableWatchdog : 0 ]

0x04: Serial : 0x00000000

0x08: DUK : 0x00000000000000000000000000000000

0x18: RootKeyDigest : 0x00000000000000000000000000000000

00000000000000000000000000000000

0x38: RevocationList : 0x00000000(0x00000000) ERROR

0x3c: 0x00000000(0x00000000) ERROR

0x40: 0x00000000(0x00000000) ERROR

0x44: 0x00000000(0x00000000) ERROR

0x48: 0x00000000(0x00000000) ERROR

0x4c: 0x00000000(0x00000000) ERROR

0x50: 0x00000000(0x00000000) ERROR

0x54: 0x00000000(0x00000000) ERROR

0x58: FW_counter : 0x00000000000000009. Собираем и исполняем «Hello,World» на СнК «СКИФ»

Следующим этапом попробуем загрузить свою небольшую программу hello-world в SPRAM0 через UART0 и исполнить её на ядре RISC0. Для этого требуется подготовить бинарник в формате HEX. Данный формат был введен в обиход компанией Intel в далеком 1973 году и с тех пор часто используется для сохранение слепков ROM, прошивок микроконтроллеров и еще много для чего.

Файл формата HEX представляет собой ASCII текст, каждая строка которого содержит небольшой блок данных в hexadecimal формате, адрес для размещения этого блока и его контрольную сумму. Каждая строка начинается с символа «:» (двоеточие), что позволяет легко детектировать и парсить данные, поступающие через последовательный интерфейс. Детальное описание Intel HEX формата можно прочитать в Wikipedia.

Если мы будем подавать такие строки с блоками данных в HEX начинающиеся с символа «:» в порт UART0, то программа ROM «монитор» будет декодировать их, изымать данные и сохранять по указанному адресу. Таким образом, нам потребуется скомпилировать свою программу hello-world для архитектуры MIPS32 без использования каких либо библиотек (режим компиляции bare-metal); слинковать её таким образом, чтобы текст (код) программы располагался с адреса 0x80000000; преобразовать получившийся бинарник в HEX формат и побайтово скопировать его в порт UART0 нашего модуля. Передать управление по любому адресу (в том числе в место загрузки нашей программы) можно с помощью команды run <addr> монитора. Команда run без параметра передает управление по адресу 0x80000000.

Начнем с того, что выкачаем Codescape GNU IMG Bare Metal Toolchain для архитектуры MIPS32 по следующей ссылке [39].

Развернем его командой tar в каталог /opt на рабочей Linux (x86_64) машине:

rz@devbox:~$ tar -zxpf Codescape.GNU.Tools.Package.2018.09-03.for.MIPS.IMG.Bare.Metal.CentOS-6.x86_64.tar.gz -C /optСоздадим скрипт следующего содержания для установки переменных окружения для кросс-компиляции:

rz@devbox:~$ cat /opt/setenv_gcc7_mips.sh

export ARCH=mips

export CONFIG_ARCH=mips

export CROSS_COMPILE=/opt/mips-img-elf/2018.09-03/bin/mips-img-elf-

export SYSROOT=/opt/mips-img-elf/2018.09-03/

export INSTALL_MOD_PATH=output

export DESTDIR=output

export CFLAGS="-Wno-misleading-indentation -Wno-int-to-pointer-cast -Wno-pointer-to-int-cast -I${SYSROOT}/include -I${SYSROOT}/usr/include "

export LDFLAGS="-L${SYSROOT}/lib -L${SYSROOT}/usr/lib -L${SYSROOT}/lib64"

export LIBS=""

export CC=${CROSS_COMPILE}gcc

export AS=${CROSS_COMPILE}as

export ASM=${CROSS_COMPILE}gcc

export LD=${CROSS_COMPILE}ld

export PKG_CONFIG_EXECUTABLE=/usr/bin/arm-linux-gnueabihf-pkg-config

export PKG_CONFIG_SYSROOT_DIR=${SYSROOT}

export PKG_CONFIG_PATH=${SYSROOT}/lib/pkgconfigЗагрузка переменных окружения для данного сеанса осуществляется командой:

rz@devbox:~$ . /opt/setenv_gcc7_mips.shВыкачаем готовый пример bare-metal утилит с репозитория НТЦ «Элвис» на Github-е:

rz@devbox:~$ git clone https://github.com/elvees/mcom03-baremetal-tools.gitПодправим исходный код программы «hello-world», содержащейся в файле mcom03-baremetal-tools/hello-world/main.c — добавим номер порта и линии GPIO, к которому у нас подключен светодиод, а так же код инициализации этого GPIO, как показано ниже.

/*

* Copyright 2021 RnD Center "ELVEES", JSC

*/

#include <stdint.h>

#include <regs.h>

#include <uart.h>

int main(void)

{

uint32_t gpio_state = 1;

REG(LSPERIPH1_SUBS_PPOLICY) = PP_ON; // Enable LSPERIPH1

REG(TOP_CLKGATE) |= BIT(6); // Enable clock to LSPERIPH1

while ((REG(LSPERIPH1_SUBS_PSTATUS) & 0x1f) != PP_ON) {

}

REG(LSP1_UCG_CTRL4) = 0x2; // GPIO_DBCLK CLK_EN

REG(LSP1_UCG_CTRL6) = 0x2; // UART_CLK CLK_EN

REG(GPIO1_SWPORTB_CTL) |= 0xc0; // UART0 in hardware mode

REG(GPIO1_SWPORTD_CTL) = 0; // GPIO1_PORTD in GPIO mode

REG(GPIO1_SWPORTD_DDR) |= 0x1; // GPIO1_PORTD_0 to output

REG(GPIO1_SWPORTA_CTL) = 0; // GPIO1_PORTA in GPIO mode

REG(GPIO1_SWPORTA_DDR) |= 0x10; // GPIO1_PORTA_4 to output

uart_init(XTI_FREQUENCY, 115200);

while (1) {

REG(GPIO1_SWPORTD_DR) = gpio_state;

REG(GPIO1_SWPORTA_DR) = (gpio_state << 4); // GPIO1_PORTA_4

uart_puts("Hello, world!n");

gpio_state = !gpio_state;

for (volatile int i = 0; i < 10000; i++) {

asm volatile ("nop");

}

}

return 0;

}Выполним сборку нашей программы:

. /opt/setenv_gcc7_mips.sh

cd mcom03-baremetal-tools

mkdir build

cmake ..

makeВ результате в каталог build будут собраны две программы: hello-world и spi-flasher, каждая в двух вариантах: для исполнения из flash памяти (XiP) порта QSPI0 и для исполнения путем загрузки в SPRAM0 через UART0:

rz@devbox:~/mcom03-baremetal-tools/build$ ll */*.hex

-rw-rw-r-- 1 rz rz 2166 Mar 21 00:05 hello-world/hello-world-mips-ram.hex

-rw-rw-r-- 1 rz rz 2166 Mar 21 00:05 hello-world/hello-world-mips-xip0.hex

-rw-rw-r-- 1 rz rz 26916 Mar 21 00:05 spi-flasher/spi-flasher-mips-ram.hex

-rw-rw-r-- 1 rz rz 26916 Mar 21 00:05 spi-flasher/spi-flasher-mips-xip0.hexЗагрузим файл hello-world-mips-ram.hex через терминал в порт UART0 нашего модуля и выдадим монитору команду run на исполнение:

rz@butterfly:/home/rz/mcom03 $ cu -l /dev/ttyU0 -s 115200

Connected

RnD Center "ELVEES", JSC

MCom-03, Bootrom rev.1.0

#

~>Local file name? hello-world-mips-ram.hex

752 bytes

#run

Starting 0x80000000...

Hello, world!

Hello, world!

...Как видим, исполняясь, программа производит вывод в последовательный порт строки текста, при этом моргает светодиод, подключенный к порту GPIO1_PORTA_4 на внешнем периметре нашего модуля.

Если кто не совсем понял, как происходит передача содержимого файла из локальной файловой системы в порт, поясню: утилита cu из стандартного дистрибутива ОС FreeBSD имеет возможность побайтовой передачи содержимого файла в последовательный порт. Для того чтобы вызвать эту функцию, необходимо нажать последовательность из двух символов ~> , на вопрос Local file name? задать имя локального файла и два раза нажать Ввод. Процесс передачи окончится сообщением числа переданных байт: 752 bytes.

10. Сборка SBL, DDRINIT, TF-A и U-Boot

Чтобы продолжить работу, а именно — начать загрузку ОС общего назначения, нам понадобиться загрузчик SBL. Напомню, что SBL содержит следующие программные модули, которые исполняются последовательно: сам SBL, DDRINIT, TF-A и U-Boot. Разные модули SBL выполняются на вычислительных ядрах различных архитектур внутри СнК «СКИФ», краткое описание каждого приводилось выше.

Для того чтобы выполнить полную сборку блоба (получить файл sbl-mips.bin), нам потребуется целых два toolchain-а: Codescape GNU IMG Bare Metal toolchain для MIPS32 и GCC 8.2 Toolchain для Aarch64 (ARM64). Выкачаем и установим недостающий toolchain для AArch64 согласно приведенной ниже инструкции:

-

Скачиваем GCC 8.2 toolchain для архитектуры AArch64 (little-endian) с официального сайта ARM, Ltd., ссылка на страницу сайта [40].

Нам потребуются следующие файлы:

-

Распаковываем toolchain так, чтобы пакеты библиотек sysroot и runtime оказались внутри каталога /opt/gcc-arm-8.2-2018.08-x86_64-aarch64-linux-gnu:

# cd /opt

# tar -xzpf ~/Downloads/gcc-arm-8.2-2018.08-x86_64-aarch64-linux-gnu.tar.xz

# cd /opt/gcc-arm-8.2-2018.08-x86_64-aarch64-linux-gnu

# tar -zxpf ~Downloads/sysroot-glibc-8.2-2018.08-x86_64-aarch64-linux-gnu.tar.xz

# tar -zxpf ~Downloads/runtime-gcc-8.2-2018.08-x86_64-aarch64-linux-gnu.tar.xz-

Создаем скрипт /opt/setenv_gcc8_arm64.sh , устанавливающий переменные окружения для кросс-компиляции:

rz@devbox:~/linux-kernels/linux-mcom03$ cat /opt/setenv_gcc8_arm64.sh

export ARCH=aarch64

export CROSS_COMPILE=/opt/gcc-arm-8.2-2018.08-x86_64-aarch64-linux-gnu/bin/aarch64-linux-gnu-

export SYSROOT=/opt/gcc-arm-8.2-2018.08-x86_64-aarch64-linux-gnu

export INSTALL_MOD_PATH=output

export DESTDIR=output

export CFLAGS="-Wno-misleading-indentation -Wno-int-to-pointer-cast -Wno-pointer-to-int-cast -I${SYSROOT}/include "

export LDFLAGS="-L${SYSROOT}/lib -L${SYSROOT}/lib64"

export CC=${CROSS_COMPILE}gcc

export CXX=${CROSS_COMPILE}g++

export CPP=${CROSS_COMPILE}cpp

export LD=${CROSS_COMPILE}ld

export AS=${CROSS_COMPILE}as

export ASM=${CROSS_COMPILE}as

export PKG_CONFIG_EXECUTABLE=/usr/bin/arm-linux-gnueabihf-pkg-config

export PKG_CONFIG_SYSROOT_DIR=${SYSROOT}

export PKG_CONFIG_PATH=${SYSROOT}/lib/pkgconfigТеперь нам потребуется выкачать исходные коды каждого из программных модулей, входящих в состав SBL, сделаем это путем клонирования соответствующих репозиториев с Github-а:

$ git clone https://github.com/elvees/mcom03-sbl.git

$ git clone https://github.com/elvees/ddrinit.git mcom03-ddrinit

$ git clone -b mcome02 --depth 1 https://github.com/elvees/arm-trusted-firmware.git mcom03-arm-trusted-firmware

$ git clone -b mcom03 --depth 1 https://github.com/elvees/u-boot.git mcom03-u-boot Собирать модули будем в обратной последовательности. Нам важно, чтобы mcom03-sbl собирался последним, так как именно в нем происходит линковка всех бинарников в единый блоб и сборка финального файла sbl-mips.bin используемого для прошивки во flash память.

Собираем U-Boot для архитектуры AArch64:

$ . /opt/setenv_gcc8_arm64.sh

$ cd ~/mcom03-u-boot

$ make mcom03bub_defconfig

$ make Собираем TF-A для архитектуры AArch64:

$ . /opt/setenv_gcc8_arm64.sh

$ cd ~/mcom03-arm-trusted-firmware

$ make PLAT=mcom03В результате получаем файл ~/mcom03-arm-trusted-firmware/build/mcom03/release/bl31.bin

Собираем DDRINIT для архитектуры AArch64:

$ . /opt/setenv_gcc8_arm64.sh

$ cd ~/mcom03-ddrinit

$ makeВ результате получаем файл ~/mcom03-ddrinit/output/ddrinit.bin

И самым последним собираем SBL для архитектуры MIPS32. В процессе сборки SBL будет собран финальный блоб. Чтобы это состоялось, перед сборкой SBL нам потребуется подредактировать файл CMakeLists.txt и исправить в нём пути к собранным ранее .bin файлам. Сборка блоба происходит средствами линковщика ld, для чего в файле link.ld.in для каждого из бинарных модулей заведена отдельная поименованная секция с глобальной ссылкой.

Ниже приведен фрагмент файла CMakeLists.txt, который требуется подредактировать вручную:

set(DDRINIT_PATH "~/mcom03-ddrinit/output/ddrinit.bin")

if(NOT DDRINIT_PATH)

message(FATAL_ERROR "DDRINIT_PATH is not specified")

endif()

set(TFA_PATH "~/mcom03-arm-trusted-firmware/build/mcom03/release/bl31.bin")

if(NOT TFA_PATH)

message(FATAL_ERROR "TFA_PATH is not specified")

endif()

set(UBOOT_PATH "~/mcom03-u-boot/u-boot.bin")

if(NOT UBOOT_PATH)

message(FATAL_ERROR "UBOOT_PATH is not specified")

endif()

Процедура сборки типовая:

$ . /opt/setenv_gcc7_mips.sh

$ cd ~/mcom03-sbl

$ vi CMakeLists.txt ### < --- исправить пути к .bin файлам

$ mkdir build

$ cd build

$ cmake ..

$ makeФинальный блоб будет находится в файле ~/mcom03-sbl/build/sbl-mips.bin

11. Прошиваем SBL загрузчик во flash память на порту QSPI0

Следующим этапом попробуем выяснить, работает ли у нас NOR flash память. Для этого нам нужно загрузить и исполнить программу spi-flasher из пакета mcom03-baremetal-tools. После сборке, проведенной выше, данная программа будет находится в файле spi-flasher-mips-ram.hex.

По аналогии с hello-world, подключимся терминалом к нашему модулю, загрузим и запустим файл spi-flasher-mips-ram.hex:

rz@butterfly:/home/rz/mcom03 $ cu -l /dev/ttyU0 -s 115200

Connected

#~>Local file name? spi-flasher-mips-ram.hex

9552 bytes

#run

Starting 0x80000000...

QSPI Flasher

#Программа spi-flasher готова к работе и принимает свой набор команд:

#help

help - show this message

qspi - select active QSPI controller: qspi <id>

erase - erase sector: erase <offset_in_bytes>

write - turn to write mode (requred binary data) : write <offset>

read - read data from SPI flash: read <offset> <size> [text|bin]

readcrc - return CRC16 of data: readcrc <offset> <size>

custom - send custom command byte and read answer: custom <cmd> <size>Попытаемся считать идентификатор микросхемы flash памяти подключенной к порту QSPI0 отправив следующие команды:

# qspi 0

# custom 0x9f 3Команда qspi 0 выбирает порт QSPI0, а команда custom посылает кастомную команду с номером 0x9F микросхеме flash памяти и дожидается ответа из неё 3-х байт. Вот какой ответ мы получим от микросхемы flash памяти на нашем модуле «RanetkaPC»:

ef 40 16

#Это говорит нам о том, что микросхема flash памяти отвечает на запросы. Её ID ={0xef, 0x40, 0x16}, что соответсвует значению из даташита на используемую нами микросхему Winbond W25Q32. А значит можно попытаться «прошить» в неё SBL загрузчик.

Для того чтобы осуществить запись загрузчика в микросхему flash памяти, нам потребуется пакет программ mcom03-flash-tools, который в свою очередь состоит из следующих утилит:

-

mcom03-flash — flont-end утилита для прошивки написанная на языке Python для ОС общего назначения. Взаимодействует с СнК MCOM03 через UART0, загружает и запускает spi-flasher-mips-ram.hex, после чего, используя командный интерфейс, по-блочно передает и записывает файл из локальной файловой системы в NOR flash на одном из портов СнК: QSPI0 или QSPI1.

-

mcom03-read-flash — front-end утилита для чтения содержимого flash памяти и сохранения в локальный файл.

Выкачать данный пакет можно с Github репозитория следующей командой:

$ git clone https://github.com/elvees/mcom03-flash-tools.gitУстановка пакета конвенциональна для программ на Python-е:

cd mcom03-flash-tools

pip3 install . --user

# or if you want to hack the code

pip3 install -e . --userПодробная инструкция по сборке и установке, как обычно, находится в файле README.rst.

Здесь следует сделать небольшое замечание. В файле mcom03_flash_tools/__init__.py имеется массив структур, описывающих параметры различных микросхем flash памяти c QSPI интерфейсом, с которыми может работать утилита. Используемой нами микросхемы Winbond W25Q32 в этом массиве не было, по этому пришлось добавить следующую строку:

FlashType("W25Q32", 4 * MiB, 64 * KiB, 256, [0xEF, 0x40, 0x16]),Если этого не сделать, то утилита mcom03-flash, считав идентификатор из микросхемы памяти, сообщит о том, что данная микросхема не поддерживается и на этом закончит свое исполнение. Формат структуры очень простой: строка названия микросхемы, размер микросхемы в байтах, размер erase блока, размер страницы для записи и массив байтов идентификатора микросхемы. Вся эта информация легко добывается из даташита на микросхему, либо угадывается опытным путем. :)

Разумеется, после внесения изменений, нужно выполнить установку пакета еще раз.

Попробуем прошить во flash память загрузчик SBL, который хранится в локальном файле sbl-mips.bin на локальной машине (о том как собрать SBL из исходных кодов я расскажу ниже). Для этого выполним следующую команду:

rz@mustodon:/home/rz/mcom03 $ mcom03-flash -v -p /dev/ttyU0 flash qspi0 sbl-mips.binВ моём случае /dev/ttyU0 это последовательное устройство, созданное конвертором USB2Serial, к которому подключен порт UART0 СнК. Параметр -v включает режим «verbose», т.е. утилита будет многословно сообщать нам о ходе процесса записи во flash память.

Вот как выглядит сам процесс записи:

Uploading flasher to on-chip RAM...

RnD Center "ELVEES", JSC

MCom-03, Bootrom rev.1.0

#Sending flasher...

#9568 bytes

#run

Starting 0x80000000...

QSPI Flasher

#qspi 0

Selected QSPI0

#custom 0x9f 6

ef 40 16 00 00 00

#Found W25Q32 memory on QSPI0

Flash size: 4 MiB, erase sector: 64 KiB, page: 256 B

Erasing 644508 bytes, rounded to 655360 bytes (10 sectors, starting from 0)...

[ ] 0.0%erase 0

OK

[██ ] 10.0%erase 65536

OK

[████ ] 20.0%erase 131072

OK

[██████ ] 30.0%erase 196608

OK

[████████ ] 40.0%erase 262144

OK

[██████████ ] 50.0%erase 327680

OK

[████████████ ] 60.0%erase 393216

OK

[██████████████ ] 70.0%erase 458752

OK

[████████████████ ] 80.0%erase 524288

OK

[██████████████████ ] 90.0%erase 589824

OK

Erase: 1.9 s (323 KiB/s)

Writing to flash 629.40 KB...

write 0

Ready for data

#Write: 80.5 s (8 KiB/s)

Checking...

readcrc 0 644508

0x6ec6

#Check: 1.9 s (334 KiB/s)

Total: 84.3 sУтилита mcom03-flash закончила своё выполнение без ошибок, запись во flash память и последующая проверка CRC выполнена успешно.

12. Загрузка SBL и U-Boot

На предыдущем этапе мы собрали и «прошили» содержимое файла sbl-mips.bin во flash память подключенной к порту QSPI0 СнК «СКИФ».

Для того чтобы инициировать процесс загрузки с SQPI0 flash, необходимо обесточить процессорный модуль и перепаять перемычки BOOT[2:0], для задания режима 0b000. После подачи питания, если не возникло никаких проблем с инициализацией аппаратуры, мы увидим следующую картину:

rz@mustodon:/home/rz $ cu -l /dev/ttyU0 -s 115200

Connected

DDRMC0: Initialized successfully within 2082649 us, 1 ranks, speed 3200 MT/s

Ranks: 1

Die size: -230055451

Rank size: 2048 MB

Full size: 2048 MB

Full SDRAM Width: 146 bits

Primary SDRAM Width: 121 bits

ECC SDRAM Width: 128 bits

Device Width: 16 bits

Number of Row Addresses: 65536

Number of Column Addresses: 1024

Number of Bank Addresses: 8

Bank Group Addressing: 1

Clock Cycle Time (tCK): 625 ps

Minimum Clock Cycle Time (tCK min): 4457 ps

Maximum Clock Cycle Time (tCK max): 1602 ps

CAS# Latency Time (tAA min): 12500 ps

Minimum Four Activate Windows Delay (tFAW): 40000 ps

RAS to CAS Delay Time (tRCD min): 30000 ps

Row Precharge Delay Time (tRP min): 101875 ps

Active to Precharge Delay Time (tRAS min): 42500 ps

Normal Refresh Recovery Delay Time (tRFC1 min): 35390000 ps

2x Mode Refresh Recovery Delay Time (tRFC2 min): 30196875 ps

4x Mode Refresh Recovery Delay Time (tRFC4 min): 30936250 ps

Short Row Active to Row Active Delay (tRRD_S min): 57500 ps

Long Row Active to Row Active Delay (tRRD_L min): 144375 ps

Long CAS to CAS Delay Time (tCCD_L min): 20000 ps

Minimum Active to Auto-Refresh Delay (tRC): 63750 ps

DDRMC1: Failed to get configuration: Failed to configure DIMM

Total DDR memory size 2048 MiB

Memory interleaving: disabled

U-Boot 2021.01-ge8f2ec33ac (Feb 07 2022 - 21:22:13 +0000)

Model: MCom-03 Bring-Up Board r1.3.0

DRAM: 1 GiB

MMC: sdhci0@10220000: 0, sdhci1@10230000: 1

Loading Environment from SPIFlash... jedec_spi_nor s25fl128s@0: unrecognized JEDEC id bytes: ef, 40, 16

*** Warning - spi_flash_probe_bus_cs() failed, using default environment

In: serial0@1750000

Out: serial0@1750000

Err: serial0@1750000

Warning: ethernet@10200000 (eth0) using random MAC address - 5a:91:76:00:a1:be

eth0: ethernet@10200000

Warning: ethernet@10210000 (eth1) using random MAC address - 7e:52:8c:db:29:1b

eth1: ethernet@10210000

Hit any key to stop autoboot: 0Из выше приведенного лога интерес представляет следующее:

1) Контроллер динамической памяти DDRMC0 успешно провел тестирование (трейнинг) микросхемы памяти и готов работать на скорости 3200 МT/s, о чем свидетельствует следующее сообщение:

DDRMC0: Initialized successfully within 2082649 us, 1 ranks, speed 3200 MT/sСразу скажу, что на такой скорости микросхема LPDDR4 памяти в нашем процессорном модуле работает нестабильно и скорость пришлось занизить до 1600 MT/s. С причинами мы сейчас разбираемся.

2) Контроллер динамической памяти DDRMC1 ничего не обнаружил, что совершенно справедливо, так как в нашем модуле использована только одна микросхема памяти и один контроллер:

DDRMC1: Failed to get configuration: Failed to configure DIMM3) Исполнение дошло до вторичного загрузчика U-Boot, который успешно стартовал, обнаружил 1 ГБ динамической памяти и ряд периферии, в том числе QSPI flash, MMC0, MMC1, MAC0 и MAC1:

U-Boot 2021.01-ge8f2ec33ac (Feb 07 2022 - 21:22:13 +0000)

Model: MCom-03 Bring-Up Board r1.3.0

DRAM: 1 GiB

MMC: sdhci0@10220000: 0, sdhci1@10230000: 1

...

Warning: ethernet@10200000 (eth0) using random MAC address - 5a:91:76:00:a1:be

eth0: ethernet@10200000

Warning: ethernet@10210000 (eth1) using random MAC address - 7e:52:8c:db:29:1b

eth1: ethernet@10210000Почему U-Boot видит только 1ГБ оперативной памяти, вместо имеющихся 2ГБ — вопрос интересный. Мы задали его в службу технической поддержки «Элвиса» и получили ответ примерно следующего содержания: «есть проблема, над её разрешением работают». Проблема, как я понимаю, связана с DDRMC контроллером, по этому в TF-A временно встроено искусственное ограничение. Проблему обещали разрешить программным способом — перепрошивкой ПО в DDRMC.

4) U-Boot готов к поиску и загрузке ядра ОС Linux.

На самом деле при первом запуске SBL у нас все было не так радужно.

Во-первых, выяснилось, что DDRINIT не поддерживал память формата LPDDR4, соответственно не мог детектировать микросхему памяти MT53D512M32D2DS, установленную на нашем процессорном модуле и не мог проводить трейнинг DDR трансивера. Эта проблема решилась после общения с технической поддержкой — нам прислали патч для DDRINIT из двух строк:

diff --git a/src/phy/phy-lpddr4.c b/src/phy/phy-lpddr4.c

index c9fffe2..8fa89c4 100644

--- a/src/phy/phy-lpddr4.c

+++ b/src/phy/phy-lpddr4.c

@@ -273,9 +273,9 @@ void phy_training_params_load(int ctrl_id, struct ddr_cfg *cfg)

- params.CsPresentChA = 3;

+ params.CsPresentChA = (CONFIG_DRAM_RANKS == 2) ? 3 : 1;

params.EnabledDQsChB = 16;

- params.CsPresentChB = 3;

+ params.CsPresentChB = (CONFIG_DRAM_RANKS == 2) ? 3 : 1;Во-вторых, обнаружилось, что после загрузки U-Boot, СнК потребляет достаточно большой ток и сильно нагревается без радиатора. Проблему решил патч для U-Boot, который останавливает и выключает незадействованные аппаратные блоки, в частности, SDR и два DSP ядра.

В-третьих, как я уже отметил, хоть трейнинг памяти на скорости 3200 MT/s и заканчивался успешно, но дальнейшая загрузка ядра ОС Linux почти в половине случаев застревала при инициализации и запуске дополнительных ARM ядер (напомню, в данном СнК всего четыре ARM ядра, в процессе загрузки используется только одно — CPU0). Опытным путем было установлено, что память работает стабильно на скорости 1600 MT/s. На этой скорости успешно стартует ОС AltLinux и проходит ряд нагрузочных тестов, но об этом позже.

13. Подготавливаемся к загрузке ОС AltLinux

Следующим логичным шагом является загрузка ОС общего назначения — Linux (AltLinux в нашем случае). Чтобы было откуда загружать AltLinux, мы смонтировали наш процессорный модуль «RanetkaPC» на несущую плату изделия «ControlPanel», посадочное место на которой было изначально предназначено для другого нашего процессорного модуля — «Module A20» на базе СнК Allwinner A20. В процессе работы над модулем «RanetkaPC» мы постарались сделать его совместимым, насколько это представлялось возможным, с модулем «Module A20» в рамках доступной нам периферии внутри СнК «СКИФ». На рис.1 вначале статьи как раз приведена фотография такой конструкции. В результате у нас появился доступ к слоту SD-карты, USB порту и прочей интересной периферии, часть из которой до сих пор находится в стадии тестирования и подгонки драйверов.

Служба технической поддержки «Элвиса» выдала нам ссылку на скачивание образа SD карты с установленной ОС AltLinux — вот такой файл:

-rw-r--r-- 1 rz rz 2807212980 Jan 26 13:15 mcom03-altlinux-sdcard-2021-09-08.bz2Ссылки на образы и документацию приведены в конце данной статьи.

Образ AltLinux был успешно развернут на SD-карту размером 16ГБ с помощью команды dd:

$ sudo dd bs=8192 if=mcom03-altlinux-sdcard-2021-09-08.bz2 of=/dev/sdb status=progressПеред тем как осуществить загрузку, нам потребовалось выполнить еще одну важную процедуру — выполнить сборку ядра ОС Linux версии 4.19.106-mcom03 из исходных кодов и создание адаптированного под наш процессорный модуль конфигурационного файла Device-Tree (DTB). Без правильного DTB в процессе загрузки ядро Linux-а может натолкнуться на «непреодолимые препятствия».

Сборка ядра Linux выполняется достаточно конвенциально, в несколько шагов:

1) Клонируем исходный код ядра Linux адаптированного для микросхемы MCOM-03 из репозитория «Элвиса» на Github-а:

$ git clone -b mcom03 --depth 1 https://github.com/elvees/linux.git linux-mcom032) Конфигурируем и собираем ядро Linux:

$ . /opt/setenv_gcc8_arm64.sh

$ cd linnux-mcom03

$ make ARCH=arm64 mcom03_defconfig

$ make ARCH=arm643) Создаем DTS файл arch/arm64/boot/dts/elvees/mcom03-RanetkaPC_Module-1.0.dts [44] для нашего модуля «RanetkaPC».

4) Выполняем компиляцию DTS в DTB:

$ make ARCH=arm64 dtbs5) Копируем результирующие файлы в раздел boot на SD-карту с AltLinux-ом:

$ sudo mount -t vfat /dev/sdb1 /mnt

$ sudo cp arch/arm64/boot/Image /mnt

$ sudo cp arch/arm64/boot/dts/elvees/mcom03-RanetkaPC_Module-1.0.dtb /mnt

$ sudo umount /mntНа этом с подготовительными работами закончено и можно приступать к загрузке ОС AltLinux.

14. Загрузка ОС AltLinux

Вставим SD-карту в слот и перезапустим модуль «по питанию». Напомню, что СнК находится в режиме загрузки 0b000 — «Загрузка напрямую через QSPI0», т.е. происходит исполнение кода SBL прямо из NOR flash на порту QSPI0.

Дождемся пока исполнение перейдет к U-Boot и в терминале появится сообщения:

Hit any key to stop autoboot: 3Нажмем любую клавишу, чтобы U-Boot не приступил к исполнению «вшитого» в него при компиляции скрипта и попадем в командную строку U-Boot:

Hit any key to stop autoboot: 0

=>Наша задача сейчас состоит в том, чтобы последовательно загрузить в память ядро ОС Linux и файл конфигурации (.dtb) с SD-карты и передать управление ядру с нужными параметрами командной строки.

1) Выясним, работает ли у нас SD/MMC интерфейс, для этого воспользуемся командами mmc list, mmc dev и mmc info:

=> mmc list

sdhci0@10220000: 0 (eMMC)

sdhci1@10230000: 1 (SD)

=> mmc dev 0

switch to partitions #0, OK

mmc0(part 0) is current device

=> mmc info

Device: sdhci0@10220000

Manufacturer ID: 45

OEM: 100

Name: DG400

Bus Speed: 25000000

Mode: MMC legacy

Rd Block Len: 512

MMC version 5.1

High Capacity: Yes

Capacity: 7.3 GiB

Bus Width: 4-bit

Erase Group Size: 512 KiB

HC WP Group Size: 8 MiB

User Capacity: 7.3 GiB WRREL

Boot Capacity: 4 MiB ENH

RPMB Capacity: 4 MiB ENH

Boot area 0 is not write protected

Boot area 1 is not write protected

=> mmc dev 1

switch to partitions #0, OK

mmc1 is current device

=> mmc info

Device: sdhci1@10230000

Manufacturer ID: 27

OEM: 5048

Name: SD16G

Bus Speed: 50000000

Mode: SD High Speed (50MHz)

Rd Block Len: 512

SD version 3.0

High Capacity: Yes

Capacity: 14.5 GiB

Bus Width: 4-bit

Erase Group Size: 512 BytesВидно, что U-Boot обнаружил два SD/MMC устройства mmc 0 и mmc 1. Нулевое — это запаянная на процессорный модуль микросхема eMMC (DG400 объёмом 7.3 GiB), а первое — вставленная в слот SD-карта (SD16G фактическим объёмом 14.5 GiB).

2) Командой fatls просмотрим содержимое загрузочного раздела на SD карте который представляет собой FAT32 файловую систему:

=> fatls mmc 1

alt/

extlinux/

13936648 Image

6291456 vmlinux

26277 mcom03-RanetkaPC_Module-1.0.dtb

3 file(s), 2 dir(s)Здесь у нас располагается ядро ОС Linux (файл Image), конфигурационный файл для ядра (файл mcom03-RanetkaPC_Module-1.0.dtb), а так же ряд других файлов и подкаталогов которые находились на развернутом образе. Нам потребуются только первые два файла.

3) Загрузим в оперативную память с адреса 0x82000000 ядро ОС Linux с помощью команды fatload:

=> fatload mmc 1 0x82000000 Image

13936648 bytes read in 975 ms (13.6 MiB/s)4) Загрузим в оперативную память с адреса 0x88800000 файл конфигурации ядра (Device-Tree):

4) Загрузим в оперативную память с адреса 0x88800000 файл конфигурации ядра (Device-Tree):

=> fatload mmc 1 0x88800000 mcom03-RanetkaPC_Module-1.0.dtb

26277 bytes read in 16 ms (1.6 MiB/s)5) Установим переменную окружения U-Boot отвечающую за параметры командной строки Linux ядра:

=> setenv bootargs earlycon console=ttyS0,115200 root=/dev/mmcblk1p2 rw rootwait initcall_debug=1 drm.debug=0x1f loglevel=8 video=DPI-1:800x480Здесь мы указываем ядру слудующее:

-

root - монтировать rootfs с устройства mmcblk1p2, т.е. второй раздел на MMC1;

-

rootwait - перед монтированием rootfs нужно дождаться готовности устройств;

-

включаем максимум диагностических сообщений, в том числе сообщение на каждый вызов процедур внутри драйверов;

-

earlycon - инструктируем ядро о том, что вывод диагностических сообщений нужно осуществлять специальным способом — работая с «железом» напрямую, а не через драйвер, иначе часть сообщений будет утеряна.

6) Используя команду booti передадим микрофон ядру ОС Linux:

=> booti 0x82000000 - 0x88800000

Moving Image from 0x82000000 to 0x82080000, end=82e23000

## Flattened Device Tree blob at 88800000

Booting using the fdt blob at 0x88800000

Loading Device Tree to 00000000bf745000, end 00000000bf74e6a4 ... OK

Starting kernel ...

[ 0.000000] Booting Linux on physical CPU 0x0000000000 [0x410fd034]

[ 0.000000] Linux version 4.19.106-g54f4366ee-dirty (rz@devbox) (gcc version 8.2.1 20180802 (GNU Toolchain for the A-profile Architecture 8.2-2018-08 (arm-rel-8.23))) #20 SMP Fri Feb 18 15:38:50 UTC 2022

[ 0.000000] Machine model: MCom-03 RanetkaPC_Module ver 1.0

[ 0.000000] earlycon: uart0 at MMIO32 0x0000000001750000 (options '115200n8')

[ 0.000000] bootconsole [uart0] enabled

[ 0.000000] cma: Reserved 128 MiB at 0x00000000b7400000

[ 0.000000] On node 0 totalpages: 262144

[ 0.000000] DMA32 zone: 4096 pages used for memmap

[ 0.000000] DMA32 zone: 0 pages reserved

[ 0.000000] DMA32 zone: 262144 pages, LIFO batch:63

[ 0.000000] psci: probing for conduit method from DT.

[ 0.000000] psci: PSCIv1.1 detected in firmware.

[ 0.000000] psci: Using standard PSCI v0.2 function IDs

[ 0.000000] psci: MIGRATE_INFO_TYPE not supported.

[ 0.000000] psci: SMC Calling Convention v1.1

[ 0.000000] random: get_random_bytes called from start_kernel+0xa0/0x44c with crng_init=0

[ 0.000000] percpu: Embedded 22 pages/cpu s51672 r8192 d30248 u90112

[ 0.000000] pcpu-alloc: s51672 r8192 d30248 u90112 alloc=22*4096

[ 0.000000] pcpu-alloc: [0] 0 [0] 1 [0] 2 [0] 3

[ 0.000000] Detected VIPT I-cache on CPU0

[ 0.000000] Speculative Store Bypass Disable mitigation not required

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 258048

[ 0.000000] Kernel command line: earlycon console=ttyS0,115200 root=/dev/mmcblk1p2 rw rootwait initcall_debug=1 drm.debug=0x1f loglevel=8 video=DPI-1:800x480

[ 0.000000] Dentry cache hash table entries: 131072 (order: 8, 1048576 bytes)

[ 0.000000] Inode-cache hash table entries: 65536 (order: 7, 524288 bytes)

[ 0.000000] Memory: 885048K/1048576K available (8638K kernel code, 1194K rwdata, 2948K rodata, 768K init, 329K bss, 32456K reserved, 131072K cma-reserved)

[ 0.000000] SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=4, Nodes=1

[ 0.000000] ftrace: allocating 29486 entries in 116 pages

[ 0.000000] rcu: Hierarchical RCU implementation.

[ 0.000000] NR_IRQS: 64, nr_irqs: 64, preallocated irqs: 0

[ 0.000000] GICv3: GIC: Using split EOI/Deactivate mode

[ 0.000000] GICv3: Distributor has no Range Selector support

[ 0.000000] GICv3: no VLPI support, no direct LPI support

[ 0.000000] ITS: No ITS available, not enabling LPIs

[ 0.000000] GICv3: CPU0: found redistributor 0 region 0:0x0000000001180000

[ 0.000000] arch_timer: cp15 timer(s) running at 27.45MHz (phys).

[ 0.000000] clocksource: arch_sys_counter: mask: 0xffffffffffffff max_cycles: 0x6550ab484, max_idle_ns: 440795202486 ns

[ 0.000003] sched_clock: 56 bits at 27MHz, resolution 36ns, wraps every 4398046511095ns

...

[ 0.334934] smp: Bringing up secondary CPUs ...

[ 0.350055] Detected VIPT I-cache on CPU1

[ 0.350087] GICv3: CPU1: found redistributor 1 region 0:0x00000000011a0000

[ 0.350121] CPU1: Booted secondary processor 0x0000000001 [0x410fd034]

[ 0.360435] Detected VIPT I-cache on CPU2

[ 0.364408] GICv3: CPU2: found redistributor 2 region 0:0x00000000011c0000

[ 0.364423] CPU2: Booted secondary processor 0x0000000002 [0x410fd034]

[ 0.374687] Detected VIPT I-cache on CPU3

[ 0.381794] GICv3: CPU3: found redistributor 3 region 0:0x00000000011e0000

[ 0.381809] CPU3: Booted secondary processor 0x0000000003 [0x410fd034]

[ 0.381872] smp: Brought up 1 node, 4 CPUs

[ 0.430510] SMP: Total of 4 processors activated.

[ 0.435544] CPU features: detected: GIC system register CPU interface

[ 0.442447] CPU features: detected: 32-bit EL0 Support

[ 0.448226] CPU: All CPU(s) started at EL2

...

[ 2.564194] EXT4-fs (mmcblk1p2): recovery complete

[ 2.568931] EXT4-fs (mmcblk1p2): mounted filesystem with ordered data mode. Opts: (null)

[ 2.576900] VFS: Mounted root (ext4 filesystem) on device 179:18.

[ 2.599291] devtmpfs: mounted

[ 2.603911] Freeing unused kernel memory: 768K

[ 2.608387] Run /sbin/init as init process

[ 2.935442] random: fast init done

[ 3.568437] drm_mcom03_mode_valid: requested_rate = 33000000, real_rate = 33000000

[ 3.576054] drm_mcom03_mode_valid: requested_rate = 33000000, real_rate = 33000000

[ 3.583600] drm_mcom03_mode_set: type = 0, cmos0_clk_clock = 148500000, mode->clock * 1000 = 33000000, ret = 0

[ 3.593498] drm_mcom03_enable: type = 0, cmos0_clk_clock = 148500000

[ 4.026070] systemd[1]: System time before build time, advancing clock.

[ 4.045788] systemd[1]: Failed to find module 'autofs4'

[ 4.181753] systemd[1]: systemd v246.14-alt1 running in system mode. (+PAM +AUDIT +SELINUX +IMA -APPARMOR +SMACK +SYSVINIT +UTMP +LIBCRYPTSETUP +GCRYPT +GNUTLS +ACL +XZ +LZ4 +ZSTD +SECCOMP +BLKID +ELFUTILS +KMOD +IDN2 -IDN +PCRE2 default-hierarchy=hybrid)

[ 4.204397] systemd[1]: Detected architecture arm64.

...

Welcome to Simply Linux 9.1 (Destiny)!

altlinux login:Ура товарищи!

Не будут сильно вдаваться в процесс загрузки ОС Linux, приведу лишь некоторые ключевые момент:

1) Перед передачей управления ядру ОС Linux, U-Boot осуществил релокацию (перенос) образа ядра с адреса загрузки 0x82000000 на адрес 0x82008000. Для этого есть несколько причин: во-первых, требуется выравнять код по границе 2БМ из-за особенностей работы виртуальной памяти, во-вторых, добавлено смещение 0x80000 указанное в заголовке ядра.

2) U-Boot распаковал загруженный DTB (Flattened Device-Tree в бинарном формате) в полноценную структуру данных и разместил её почти в самый конец доступной оперативной памяти, по адресу 0x00000000bf745000 (напоминаю, что на данный момент нам доступен только 1ГБ ОЗУ).

3) Запуск ядра ОС Linux осуществляется на одном вычислительном ядре (CPU0). На ранних стадиях инициализации аппаратуры, ядро ОС Linux проводит поиск и запуск остальных трех вычислительных ядер. Результат мы видим в следующих сообщениях:

[ 0.430510] SMP: Total of 4 processors activated.

[ 0.448226] CPU: All CPU(s) started at EL24) ОС Linux на всех четырех вычислительных ядра работает в режиме Execution Level 2 (EL2). Это говорит о том, что над ядром ОС общего назначение находится супервизор, в данном случае TF-A, работающий в режиме исполнения EL3.

5) Ядро ОС Linux успешно осуществило монтирование корневой файловой системы с устройства mmcblk1p2, которое содержит файловую систему типа EXT4FS.

[ 2.564194] EXT4-fs (mmcblk1p2): recovery complete

[ 2.568931] EXT4-fs (mmcblk1p2): mounted filesystem with ordered data mode. Opts: (null)

[ 2.576900] VFS: Mounted root (ext4 filesystem) on device 179:18.6) Процесс /sbin/init успешно стартовал и начал исполнение rc скриптов, в том числе запустился системный демон systemd.

7) Процесс login запущен и мы видим приглашение к входу в систему.

15. Просмотр основных параметров системы

Войдем в систему под пользователем altlinux (с пустым паролем), после чего перейдем в режим супер-пользователя командой su - (символ «минус» обязателен при работе в AltLinux) и немного осмотримся:

[root@altlinux ~]# cat /proc/cpuinfo

processor : 0

BogoMIPS : 54.91

Features : fp asimd crc32 cpuid

CPU implementer : 0x41

CPU architecture: 8

CPU variant : 0x0

CPU part : 0xd03

CPU revision : 4

processor : 1

BogoMIPS : 54.91

Features : fp asimd crc32 cpuid

CPU implementer : 0x41

CPU architecture: 8

CPU variant : 0x0

CPU part : 0xd03

CPU revision : 4

processor : 2

BogoMIPS : 54.91

Features : fp asimd crc32 cpuid

CPU implementer : 0x41

CPU architecture: 8

CPU variant : 0x0

CPU part : 0xd03

CPU revision : 4

processor : 3

BogoMIPS : 54.91

Features : fp asimd crc32 cpuid

CPU implementer : 0x41

CPU architecture: 8

CPU variant : 0x0

CPU part : 0xd03

CPU revision : 4Видно, что операционной системе доступно 4 вычислительных ядра ARMv8 с поддержкой Advanced SIMD, блоком вычислений с плавающей точкой (FP) и аппаратным вычислителем CRC. Производительность каждого ядра оценена в 54.91 BogoMIPS, но об этом чуть позже.

Запустим утилиту top и посмотрим сколько у нас имеется оперативной памяти и как она задействована:

[root@altlinux ~]# top

top - 18:14:55 up 4 min, 2 users, load average: 1,11, 1,95, 0,94

Tasks: 150 total, 1 running, 149 sleeping, 0 stopped, 0 zombie

%CPU(s): 0,2 us, 0,0 sy, 0,0 ni, 99,8 id, 0,0 wa, 0,0 hi, 0,1 si, 0,0 st

MiB Mem : 993,1 total, 347,2 free, 324,2 used, 321,6 buff/cache

MiB Swap: 0,0 total, 0,0 free, 0,0 used. 593,2 avail Mem Выясним, что за дистрибутив ОС Linux нам достался:

root@altlinux ~]# cat /etc/os-release

NAME="Simply Linux"

VERSION="9.1 (Destiny)"

ID=altlinux

VERSION_ID=9.1

PRETTY_NAME="Simply Linux 9.1 (Destiny)"

ANSI_COLOR="1;36"

CPE_NAME="cpe:/o:alt:slinux:9.1"

HOME_URL="https://www.basealt.ru/products/simplylinux/"

BUG_REPORT_URL="https://bugs.altlinux.org/"[root@altlinux ~]# ps ax | grep xfce

433 ? Ssl 0:01 xfce4-session

568 ? Sl 0:00 /usr/lib64/xfce4/xfconf/xfconfd

857 ? Sl 0:00 xfce4-panel --display :0.0 --sm-client-id 2b22d59c6

871 ? Sl 0:00 /usr/lib64/xfce4/panel/wrapper-2.0 /usr/lib64/xfce4

876 ? Sl 0:00 /usr/lib64/xfce4/panel/wrapper-2.0 /usr/lib64/xfce4

877 ? Sl 0:03 /usr/lib64/xfce4/panel/wrapper-2.0 /usr/lib64/xfce4

878 ? Sl 0:00 /usr/lib64/xfce4/panel/wrapper-2.0 /usr/lib64/xfce4

879 ? Sl 0:00 /usr/lib64/xfce4/panel/wrapper-2.0 /usr/lib64/xfce4

880 ? Sl 0:00 /usr/lib64/xfce4/panel/wrapper-2.0 /usr/lib64/xfce4

881 ? Sl 0:00 /usr/lib64/xfce4/panel/wrapper-2.0 /usr/lib64/xfce4

910 ? Ssl 0:00 xfce4-power-manager --restart --sm-client-id 2e896e

939 ? Ssl 0:00 /usr/lib64/xfce4/notifyd/xfce4-notifydВидно, что у нас полноценный десктопный вариант AltLinux-а с запущенным xfce4 в качестве оконного менеджера. Из этого так же следует, что Xorg обнаружил и задействововал встроенный видеоадаптер.

Посмотрим в файла /var/log/Xorg.0.log и выясним, что у нас запущен Xorg 1.20.8, в качестве дисплейного драйвера использован modesetting (универсальный драйвер) без поддержки OpenGL:

[ 31.453] (II) modeset(0): Refusing to try glamor on llvmpipe

[ 31.500] (EE) modeset(0): glamor initialization failed

[ 31.500] (II) modeset(0): ShadowFB: preferred NO, enabled NO

[ 31.509] (II) modeset(0): Output DPI-1 has no monitor section

[ 31.517] (II) modeset(0): EDID for output DPI-1

[ 31.517] (II) modeset(0): Printing probed modes for output DPI-1

[ 31.517] (II) modeset(0): Modeline "800x480"x59.6 33.00 800 979 1009 1055 480 501 502 525 -hsync (31.3 kHz eP)

[ 31.517] (II) modeset(0): Output DPI-1 connected

[ 31.517] (II) modeset(0): Using exact sizes for initial modes

[ 31.517] (II) modeset(0): Output DPI-1 using initial mode 800x480 +0+0

[ 31.517] (==) modeset(0): Using gamma correction (1.0, 1.0, 1.0)

[ 31.517] (==) modeset(0): DPI set to (96, 96)К сожалению, нам не удалось подключить LCD дисплей на порт DPI нашего модуля, чтобы опробовать все прелести работы в графической среде, так как обнаружилась несовместимость по уровням сигналов: СнК «СКИФ» выдает сигналы напряжением 1.8V, в то время как все имеющиеся у нас LCD принимают сигнал минимум от 3.0V. Очевидно, что найти дисплей с уровнями сигналов 1.8V будет крайне не просто, а значит потребуется ввести в схему модуля микросхемы преобразователя уровней, что скажется на максимальной частоте развертки и вообще усложнит и удорожает схему включения LCD.

Изменить уровни выходных сигналов для DPI не представляется возможным, это стало понятно после общения со службой технической поддержки «Элвиса». Честно говоря, я был крайне разочарован таким решением инженеров «Элвиса».

В СнК «СКИФ» имеется четыре датчика температуры, по одному на каждую из подсистем. Попробуем прочитать их текущие значения:

[root@altlinux ~]# cat /sys/devices/platform/*/*.pvt/hwmon/hwmon*/temp*

54987

cpu

54465

sdr

54639

media

54987

serviceВидно, что температура микросхемы составляет около 54.8°C. При этом на микросхеме установлен небольшой алюминиевый радиатор. В целом, это допустимо, при том что в данном случае, ARM ядра СнК работают на частоте 1.4ГГц и напряжении питания 0.9V.

Попутно выяснили, что в процессе работы ОС Linux наш модуль «RanetkaPC» потребляет ток до 0.65A от внешней линии питания 5V, итого 3.25W.

16. Проблема с архитектурным таймером

Теперь вернемся к BogoMIPS-ам. Изначально, до версии Linux 3.6, параметр BogoMIPS использовался операционной системой для внутренних циклов задержки (delay loops), для расчета минимального кванта времени используемого при переключении контекста (jiffies), а так же для еще ряда служебных нужд. BogoMIPS рассчитывался (калибровался) каждый раз при загрузке операционной системы, как количество холостых циклов процессора за один квант времени и выражался в «миллионах циклов процессора в секунду». Разумеется, такой подсчет не является точным с научной точки зрения и поэтому имеет в названии приставку Bogo от английского слова «bogus» (кривой, убогий). Придумал этот параметр, кстати, сам Линус Торвальдс в 1993 году.

Однако с появлением технологий динамического изменения частоты вычислительного ядра, а так же технологии big.LITTLE [45], использование такого параметра, как BogoMIPS, стало наталкиваться на проблемы, и с версии Linux 3.6 начали использовать другой параметры — lpj или loops_per_jiffies. Расчет lpj так же производится при загрузки системы, но не полагаясь на производительность вычислительного ядра, а на частоту системного таймера, частота которого всегда постоянна и, зачастую, заранее известна. Параметр BogoMIPS остался, но он теперь почти не связан с количеством циклов процессора, а является своего рода индексом (показателем) производительности вычислительного ядра на максимальной тактовой частоте.

Более подробно об этой особенности ОС Linux можно прочитать в статье на Wikipedia [46].

Чтобы правильно рассчитать BogoMIPS (а точнее уже lpj — loops_per_jiffies, так как мы используем ядро 4.19), системе требуется такая штука, которая называется «Архитектурный Таймер». Архитектурный таймер, в ядре ОС Linux называется arch_timer, это аппаратный таймер внутри микросхемы СнК или микропроцессора, частота которого заранее известна, стабильна (не зависит от режимов работы вычислительных ядер) и существенно ниже самой низкой тактовой частоты процессора, при этом счетчик таймера постоянно и монотонно нарастает и не переполняется.

Архитектурный таймер участвует не только в переключении контекста, но и для выдачи системного времени от начала запуска вычислительного ядра, того самого, которое возвращает системный вызов gettimeofday(), а так же выводит утилита date, разумеется, после корректировки смещения полученного от RTC (часов реального времени) или по протоколу NTP от сервера точного времени. Иными словами, архитектурный таймер является опорой всей операционной системы.

И тут нас ожидал интересный подвох. Я обратили внимание на то, что параметр lpj, который отображается при загрузке ядра ОС Linux, несколько отличался от того, что следовало бы ожидать. Дело в том, что в нашем процессорном модуле в качестве источника опорной частоты использован кварцевый резонатор на частоту 27.456МГц, в точном соответствии с «Руководством» на микросхему СнК «СКИФ». Однако, в логе мы наблюдали следующее:

[root@altlinux ~]# dmesg | grep MIPS

[ 0.013755] Calibrating delay loop (skipped), value calculated using timer frequency.. 54.00 BogoMIPS (lpj=270000)Это сразу навело нас на мысль о том, что архитектурный таймер либо неверно настроен, либо ядру операционной системы сообщили неверную частоту этого таймера. А это может создавать ряд проблем, одна из которых — неправильное вычисление системного времени, а значит у нас будут проблемы с корректным измерением производительности системы, т.е. различные тесты (бенчмарки) просто будут неверны. Это предположение тут же подтвердилось простым замером времени по команде date и сравнению его с «настенными» часами — системные часы «спешили» примерно на 1 секунду за минуту (или на 1:01 минуту за час), что соответствует разнице в опорных частотах между нашим кварцевым резонатором (27.456MHz) и тем что ожидает система в качестве опорной частоты для arch_timer (27.000MHz).