Архитектуры процессоров и их свойства

❯ Введение

Любой человек хоть как то связанный с техникой вероятно имеет понимание о базовых принципах работы процессора (то что он состоит из транзисторов, о том что память хранит все в бинарной форме и т.п.)

Также я почти уверен что каждый где-то видел или слышал x86, ARM и подобные. Да и скорее всего у меня не у одного вставал вопрос "А почему игра/софтина не идет на ARM, а только на x86?"

❯ О том как работает x86 (CISC) процессор

Схема 6x86 32-битного процессора Cyrix 1995 года

На схеме вы можете увидеть схему архитектуры x86 процессора

На изображении представлена схема архитектуры процессора, включающая различные компоненты и их взаимодействие. Давайте разберем каждый элемент:

-

Блок управления шиной :

-

Блок отвечающий за управление передачей данных между различными компонентами системы через шины.

-

-

Кэш-память :

-

Включает две части:

-

256 байтовая кэш-память : Предназначена для хранения часто используемых данных или инструкций.

-

16 Кб унифицированная кэш-память : Более крупный объем памяти для хранения как данных, так и инструкций.

-

-

-

Integer Unit (Целочисленное ядро) :

-

Содержит две линии (X Pipe и Y Pipe), каждая из которых имеет несколько стадий:

-

IF (Instruction Fetch) : Загрузка инструкции.

-

ID (Instruction Decode) : Декодирование инструкции.

-

AC (Address Calculation) : Вычисление адреса.

-

EX (Execute) : Выполнение инструкции.

-

WB (Write Back) : Запись результата обратно в регистры или память.

-

-

Такая линейная структура позволяет параллельно обрабатывать несколько инструкций, что повышает производительность.

-

-

FPU (Floating Point Unit, Процессор чисел с плавающей точкой) :

-

Отвечает за выполнение операций с числами с плавающей точкой.

(Капитан очевидность) -

Включает очередь для обработки таких операций. (Очередь плавающей точки)

-

-

Блок управления памятью :

-

Обеспечивает доступ к основной памяти и координирует работу с кэш-памятью.

(Опять капитан очевидность)

-

Взаимодействие компонентов:

-

Блок управления шиной взаимодействует с кэш-памятью для передачи данных.

-

Кэш-память предоставляет данные и инструкции для Integer Unit и FPU .

-

Integer Unit выполняет целочисленные операции и взаимодействует с кэш-памятью и блоком управления памятью.

-

FPU выполняет операции с числами с плавающей точкой и также взаимодействует с кэш-памятью и блоком управления памятью.

-

Блок управления памятью координирует доступ к основной памяти и обеспечивает корректную работу всей системы.

CISC (англ. Complex Instruction Set Computer — «компьютер с полным набором команд») — тип процессорной архитектуры.

Для CISC характерны нефиксированная длина команд, кодирование арифметических действий в одной команде и небольшое число регистров, многие из которых выполняют строго определённую функцию.

RISC (от англ. reduced instruction set computer) переводится на русский язык как «сокращённое (ограниченное) число команд (инструкций)».

Это архитектура процессора, в которой быстродействие увеличивается за счёт упрощения инструкций: их декодирование становится более простым, а время выполнения — меньшим.

x86 процессоры используют стандартный CISC, а вот на примере CISC Intel x86 ASM я приведу примеры работы процессора

ENTER 16, 0 ; Выделяет 16 байт под локальные переменные.ENTER 16, 0 в ассемблере x86 используется для создания стековой рамки (stack frame) при входе в подпрограмму. Она выполняет следующие действия:

-

Уменьшает значение регистра

ESPна заданное количество байт (в данном случае на 16 байт), создавая пространство для локальных переменных. -

Сохраняет текущее значение регистра

EBPна стек . -

Загружает новое значение в регистр

EBP, указывающее на старое значениеEBPна стеке , что позволяет использоватьEBPдля доступа к параметрам и локальным переменным.

Ход выполнения

-

Изначально код загрузится из кэш памяти (или основной) и попадает в "конвейер" X pipe и Y pipe, на схеме этап IF (Instruction Fetch).

-

В этапе ID (indstruction decode) процессор декодирует скомпилированную ASM команду и определяет что она создает стековую рамку.

-

Далее мы переходим в AC (Address Calculation). Вычисляется адрес для обновления регистра

ESP. В данном случае, вычитается 16 байт из текущего значенияESP. -

Далее, в EX уже уменьшение регистра

ESP, что собственно мы и хотели сделать. -

И финальное, WB (Write back) - Новые значения регистров

ESPиEBPзаписываются обратно

То есть сам процессор и все действия (за исключением подгрузки в начале) происходят в числовом формате в Integer Unit. А когда они происходят в FPU?

Что логично FPU учавствует в работе реже IU так как в основном вычисления целочисленные, но вот пример в котором будет задействован он

FADD st(0), st(1) ; Сложение чисел с плавающей точкойВообще все действия с процессором происходят в таком формате как бы это не казалось нереальным.

❯ А теперь MIPS

MIPS (Microprocessor without Interlocked Pipeline Stages) — это архитектура процессоров которую по сути заменил ARM, первые процессоры PlayStation (PS1 MIPS R3000), телефонов, планшетов, бытовой технике, встраиваемых системах и других сферах. Не смотря на то что они используются в одних сегментах они не совсем одинаковы.

-

ARM:

-

ARM (Advanced RISC Machine) стал более популярным в мобильных устройствах, таких как смартфоны и планшеты, благодаря своей энергоэффективности и высокой производительности.

-

ARM также широко используется в встраиваемых системах, IoT-устройствах и даже в некоторых серверных решениях.

-

-

MIPS:

-

MIPS использовался в различных встраиваемых системах, сетевых устройствах и игровых консолях. Но его популярность крайне упала по сравнению с ARM в последние годы.

-

MIPS все еще применяется в некоторых "нишевых" областях, но все-таки ARM стал доминирующей архитектурой в мобильных и встраиваемых системах.

-

Таким образом, можно сказать, что ARM в значительной степени "заменил" MIPS, не смотря на их различия.

MIPS использует RISC команд - то есть использует упрощённый набор команд. Он не просто использует RISC, он один из его основоположников.

Следует уточнить что MIPS - не только микропроцессоры, есть и обычные такие как IDT RC32438, ATI Xilleon, Alchemy Au1000, 1100, 1200, Broadcom Sentry5 и др.

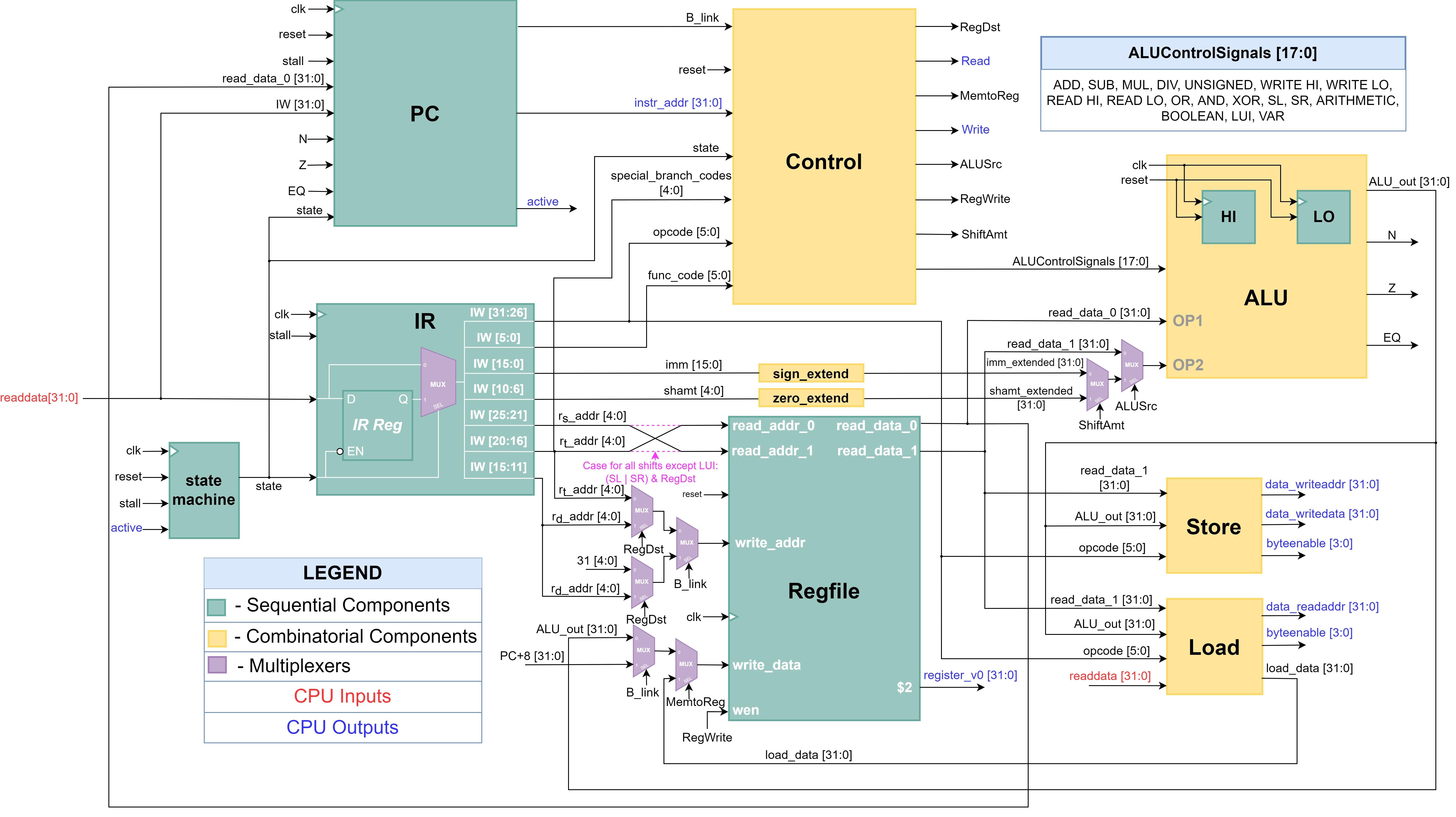

На схеме мы тоже видим обозначения, ее я перевести не взялся по этому опишу их тут.

Дальше описывал в формате

Заголовок

Определение с википедии

-

Тезисное объяснение

-

Тезис2

1. PC (Program Counter/Программный счетчик) :

Счётчик кома́нд (также PC = program counter, IP = instruction pointer, IAR = instruction address register, СчАК = счётчик адреса (машинных) команд) — регистр процессора, который указывает, какую команду нужно выполнять следующей[1].

В большинстве процессоров после выполнения команды, если она не нарушает последовательности команд (например, команда перехода), счётчик автоматически увеличивается (постинкремент). Понятие счётчика команд тесно связано с архитектурой фон Неймана, одним из принципов которой является выполнение команд друг за другом в определённой последовательности.

-

Содержит адрес текущей выполняемой инструкции.

-

Обновляется после каждой инструкции для перехода к следующей.

2. IR (Instruction Register/Регистр команд) :

Регистр команд — часть блока управления центрального процессора, который содержит инструкцию, выполняемую в настоящий момент или декодированную

-

Хранит текущую инструкцию, загруженную из памяти.

-

Разделяется на поля для различных частей инструкции (

opcode,rs,rt,rd,immediate).

3. Control Unit (Блок управления) :

Управляющий автомат, устройство управления процессором — блок, устройство, компонент аппаратного обеспечения компьютеров. Представляет собой конечный дискретный автомат. Структурно устройство управления состоит из: дешифратора команд (операций), регистра команд, узла формирования (вычисления) текущего исполнительного адреса, счётчика команд.

-

Генерирует сигналы управления для других компонентов в зависимости от opcode инструкции.

-

Определяет, какие операции должны быть выполнены (например,

ALU operation,memory access).

4. Regfile (Register File/Регистрационный файл) :

Регистровый файл — модуль микропроцессора, содержащий в себе реализацию регистров процессора. Современные регистровые файлы, используемые в СБИС, обычно реализованы как многопортовый массив быстрой статической памяти SRAM

-

Набор регистров, используемых для хранения данных.

-

Поддерживает чтение и запись данных по указанным адресам.

5. ALU (Arithmetic Logic Unit/Арифметическо-логическое устройство) :

Арифме́тико-логи́ческое устройство — блок процессора, который под управлением устройства управления служит для выполнения арифметических и логических преобразований (начиная от элементарных) над данными, называемыми в этом случае операндами. Разрядность операндов обычно называют размером или длиной машинного слова.

-

Выполняет арифметические и логические операции над данными.

-

Принимает два операнда (

OP1иOP2) и генерирует результат (ALU_out).

6. Load/Store Units (Единицы погрузки/хранения):

-

Обеспечивают доступ к памяти для загрузки и сохранения данных.

-

Load unit читает данные из памяти, Store unit записывает данные в память.

7. State Machine :

В вычислительной технике блок хранения нагрузки (LSU) представляет собой специализированный исполнительный блок, отвечающий за выполнение всех инструкций по нагрузке и хранению, генерацию виртуальных адресов операций с нагрузкой и хранением и загрузкой данных из памяти или хранением их обратно в память из регистров.

Блок нагрузочного магазина обычно включает в себя очередь, которая действует как зона ожидания для инструкций памяти, а само устройство работает независимо от других процессорных блоков.

Блоки Load-store также могут использоваться в векторной обработке, и в таких случаях может использоваться термин "вектор нагрузок-магазин"

-

Управляет состоянием процессора, обрабатывая различные события (например,

reset,stall).

А теперь пример RISC ассемблерной команды и ее выполнения.

ADD $t0, $t1, $t2 ;Сложение регистров t0, t1 в регистр t2-

В первом этапе IF (Instruction Fetch) PC загружает инструкцию из памяти в IR

-

Далее переходим в ID (Instruction Decode) где Control Unit декодирует инструкцию, определяя, что это команда

ADD -

В execute (EX) Regfile считывает значения из регистров

$t1и$t2, а после чегоALUвыполняет сложение этих значений. Результат сохраняется вALU_out -

MEM (Memory Access): Для команды ADD этот этап не требуется, так как она не взаимодействует с памятью.

-

Результат из

ALU_outзаписывается обратно в регистр$t0через Regfile. (Этап WB - Write back)

Разницу видно хреновенько, давайте еще раз только наглядно

В CISC архитектуре одна команда может выполнять несколько операций. Например, команда MOV для адресного смещения

MOV AX, [BX + SI + 8] ; Загрузить данные из памяти по адресу BX + SI + 8 в AX-

Что делает:

-

Вычисляет адрес (BX + SI + 8).

-

Загружает данные из памяти по этому адресу.

-

Записывает их в регистр AX.

-

В RISC архитектуре каждая команда выполняет только одну операцию. Например, загрузка данных из памяти разбивается на несколько простых команд

LW $t0, 8($t1) ; Загрузить слово из памяти по адресу t1 + 8 в t0|

Характеристика |

CISC |

RISC |

|

Длина команд |

Разная (например, 1–15 байт) |

Фиксированная (например, 32 бита) |

|

Количество операций |

Одна команда выполняет несколько |

Одна комманда -- одна операция |

|

Скорость выполнения |

Могут требовать несколько тактов |

Обычно за один такт |

|

Примеры архитектур |

x86 (Intel/AMD), Motorola 68000 |

MIPS, ARM, RISC-V, SPARC |

Так вот, все игры/софты как правило скомпилированы в исполняемый файл. А теперь не много в другое русло, все те кто качал iso образы операционных систем как правило видели множество вариаций ее сборки, как раз таки подо все архитектуры PowerPC, AMD64, i368, aarch64 и другие. Так вот все это нужно менять и рекомпилировать для того чтобы оно работало на ARM, который в настоящий момент достаточно новый сегмент для desktop сессий. То есть софта на него мало. Как правило компаниям это не принесет большого дохода, а следовательно зачем тогда парится и что-то оптимизировать за "бесценок"? Особенно кстати такое работает с играми. Так вот и не зачем проводить лишнюю работу.

Это так, если кто-то все-таки не догадался.

❯ Введение

Статья вроде вышла интересной, но помоему что-то не так, вот уже два дня не публиковал пытался понять что. Так и не понял, увы. Ну если что буду чинить. Спасибо за прочтение! Если заинтересовало прошу подписаться на мой телеграм канал. [2]

Автор: Namilsky

Источник [3]

Сайт-источник PVSM.RU: https://www.pvsm.ru

Путь до страницы источника: https://www.pvsm.ru/mips/413295

Ссылки в тексте:

[1] https://en.wikipedia.org/wiki/File%3ACyrix_6x86_arch.svg: https://en.wikipedia.org/wiki/File%3ACyrix_6x86_arch.svg

[2] телеграм канал.: https://t.me/ArcaneDevStudio

[3] Источник: https://habr.com/ru/articles/890030/?utm_campaign=890030&utm_source=habrahabr&utm_medium=rss

Нажмите здесь для печати.