В далеком 2011 году компания Xilinx представила свои первые микросхемы SoC (System On Chip) — Zynq-7000. SoC Zynq сочетает в себе программируемую логику, процессорный модуль и некоторую периферию. Статья не является максимально полным описанием SoC Zynq, а лишь отражает те или иные характеристики, с которыми пришлось столкнуться при разработке устройств на базе SoC Zynq.

Содержание

1 Общие сведения

2 Порты

2.1 MIO

2.2 EMIO

2.3 GP

2.4 HP

2.5 ACP

3 Периферия

3.1 Static Memory Controller

3.2 Quad-SPI Flash Controller

3.3 SD/SDIO Controller

3.4 General Purpose I/O (GPIO)

3.5 USB Host, Device, and OTG Controller

3.6 Gigabit Ethernet Controller

3.7 SPI Controller

3.8 CAN Controller

3.9 UART Controller

3.10 I2C Controller

3.11 XADC Interface

4 Процессорный модуль

5 Программируемая логика

6 Производительность

6.1 Теоретическая

6.2 Практическая

6.2.1 Обработка сетевых пакетов

6.2.2 Производительность порта HP

7 Передача данных между процессорным модулем и программируемой логикой

8 Загрузка SoC

9 Проблемы

10 Создание файла конфигурации

11 Заключение

12 Используемые источники

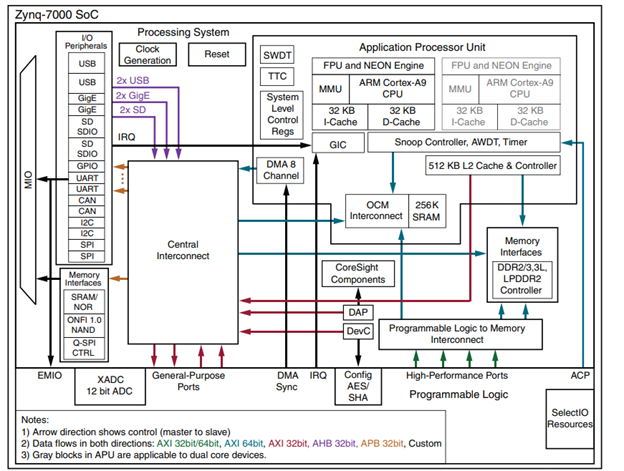

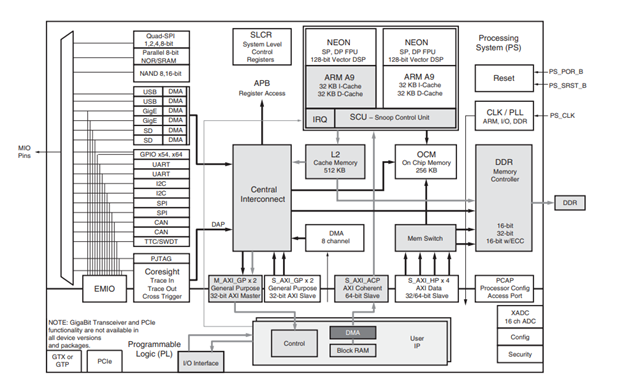

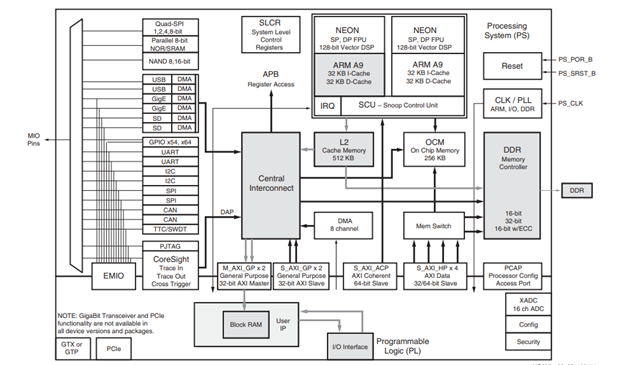

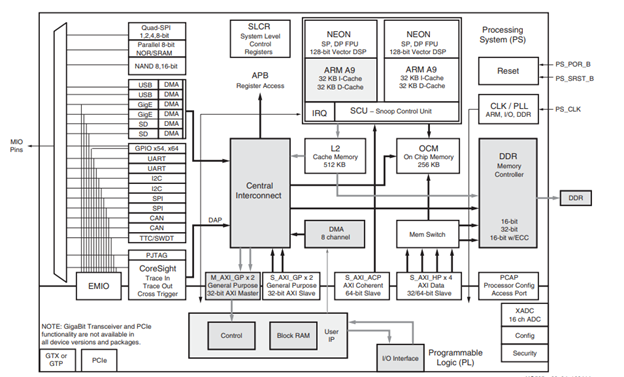

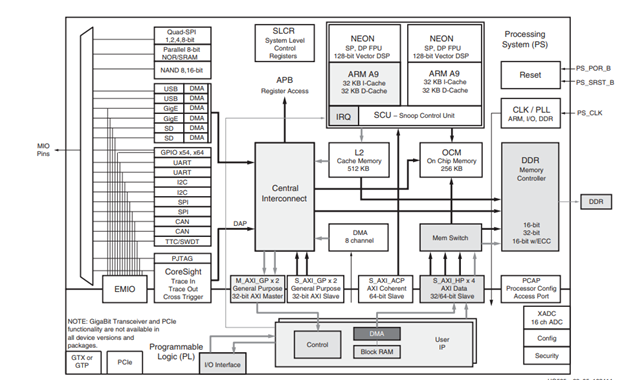

1 Общие сведения

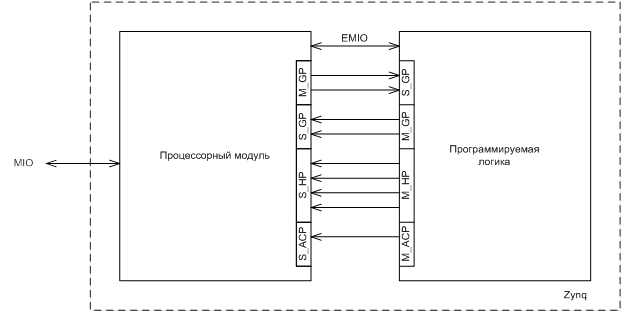

Каждый Zynq состоит из одного или двух ядер ARM Cortex-A9 (ARM v7), кэш L1 у каждого ядра свой, кэш L2 общий. Поддерживаемая оперативная память имеет стандарты DDR3, DDR3L, DDR2, LPDDR-2. Максимальный объем оперативной памяти равен 1 Гбайт (2 микросхемы по 4 Гбит). Максимальная тактовая частота оперативной памяти 525 МГц. Операционные системы: Standalone (bare-metal) и Petalinux. Процессорный модуль общается с внешним миром и программируемой логикой с помощью портов, объединенных в группы:

- MIO (multiplexed I/O);

- EMIO (extended multiplexed I/O);

- GP (General-Purpose Ports);

- HP (High-Performance Ports);

- ACP (Accelerator coherency port).

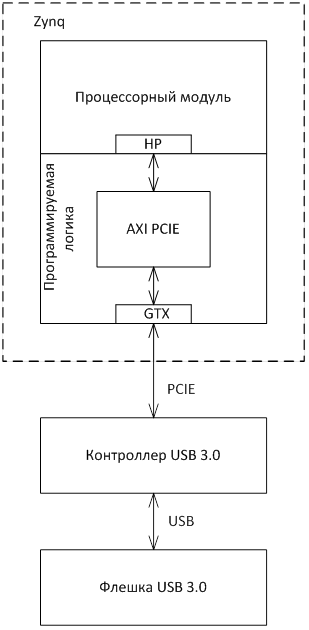

Схема интерфейсов Zynq.

Буквы S и M у порта обозначают соответственно Slave и Master.

Так как, в одном корпусе Zynq реализованы и процессорный модуль и программируемая логика, есть выводы, которые относятся к процессорному модулю и выводы, которые относятся к программируемой логике.

2 Порты

2.1 MIO

Порты MIO подключены к выводам процессора. С помощью MIO могут быть подключены следующие периферийные устройства процессорного модуля:

- USB-контроллер – 2 шт;

- Gigabit Ethernet контроллер – 2 шт;

- SD/SDIO контроллер – 2 шт;

- UART – 2 шт;

- CAN – 2 шт;

- I2C – 2 шт;

- SPI – 2 шт;

- GPIO. Все выводы можно использовать как выводы общего назначения.

Так же, к MIO могут быть подключены следующие устройства памяти процессорного модуля:

- QSPI контроллер;

- ONFI контроллер;

- SRAM/NOR контроллер.

Количество MIO портов равно 54 (за исключением некоторых микросхем в корпусе CLG225, там еще меньше). Поэтому все сразу включить не удастся. Для решения этой проблемы существует группа портов EMIO.

2.2 EMIO

EMIO представляет собой проброс периферийного устройства из процессорного модуля в программируемую логику и подключение периферийного устройства к выводам программируемой логики. Однако не все периферийные устройства можно перенести через EMIO, какие-то не переносятся совсем (USB), какие-то с изменением функциональности (Ethernet через EMIO имеет интерфейс GMII для подключения внешней микросхемы физического уровня). Между процессорным модулем и программируемой логикой по порту EMIO можно подключить 192 сигнала (64 входа и 128 выходов).

2.3 GP

Порты GP используют протокол Axi-Lite. Протокол подразумевает работу с данными шириной до 32 бит. За одну транзакцию осуществляется передача/прием данных, размером не больше 32 бит. Используется, как правило, для управления блоками в программируемой логике или при низкоскоростном обмене. Существует 2 порта Master и 2 порта Slave.

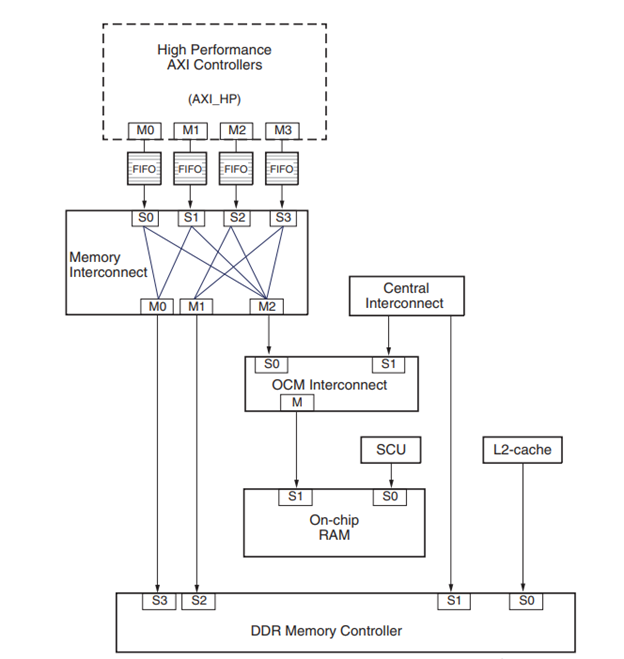

2.4 HP

Порты HP используют протокол AXI4. Протокол подразумевает работу с данными шириной 32 или 64 бита. Протокол поддерживает boost транзакции. За одну транзакцию осуществляется передача/прием произвольного размера данных. Используется, как правило, для организации высокоскоростного обмена данными между процессорным модулем и программируемой логикой. Существует 4 порта Slave.

Путь передачи данных с помощью порта HP

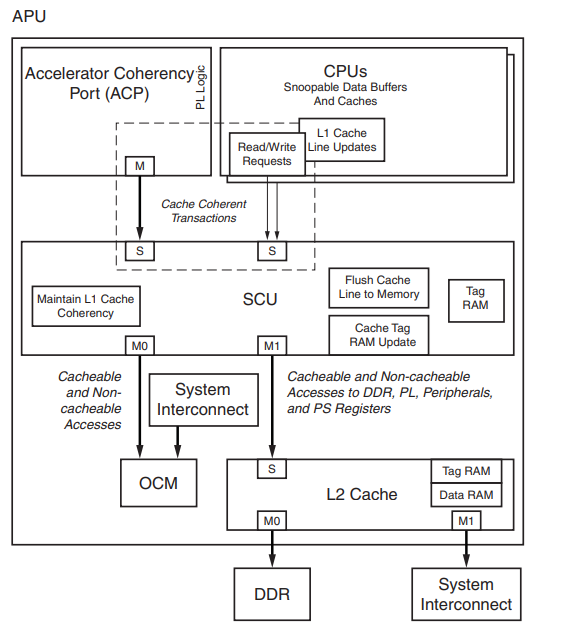

2.5 ACP

Порт ACP использует протокол AXI4. Протокол подразумевает работу с данными 64 бита. Протокол поддерживает boost транзакции. За одну транзакцию осуществляется передача/прием произвольного размера данных. Используется, как правило, для организации высокоскоростного обмена данными между процессорным модулем и программируемой логикой, причем данные дополнительно помещаются в L2 кэш. Существует один порт Slave.

Путь передачи данных с помощью порта ACP

3 Периферия

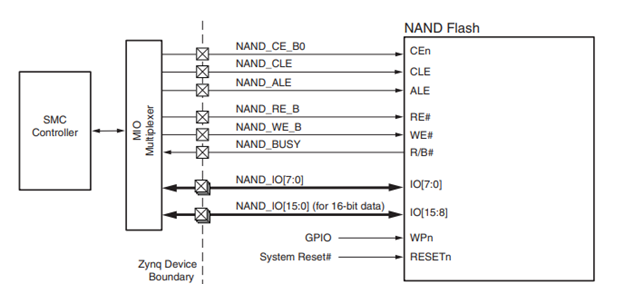

3.1 Static Memory Controller

SMC используется как контроллер памяти с технологией NAND или как контроллер памяти с параллельным интерфейсом. Поддерживает следующие типы памяти:

- NAND flash;

- NOR flash;

- асинхронная SRAM.

Контроллер памяти с технологией NAND характеризуется следующими пунктами:

- поддержка спецификации ONFI 1.0;

- поддержка микросхем памяти емкостью до 1 Гбайт;

- 1 бит ECC, считаемый аппаратно (используется в случае, если микросхема Flash-памяти не поддерживает ECC).

- 8 или 16 линий обмена данными и одна линия выбора микросхемы (Chip Select);

- асинхронный режим работы.

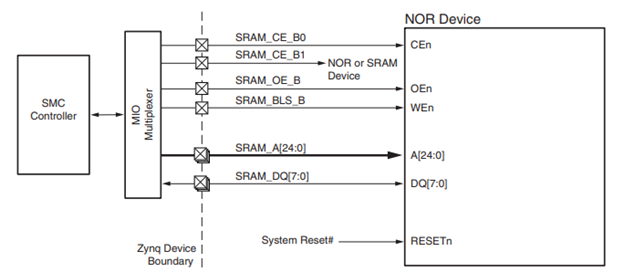

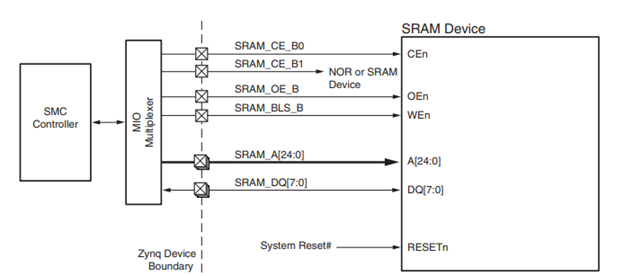

Контроллер памяти с параллельным интерфейсом характеризуется следующими пунктами:

- 8 линий обмена данными;

- 2 линии выбора микросхемы (Chip Select);

- 25 линий адреса;

- Асинхронный режим работы.

Подключение микросхемы NOR Flash с параллельным интерфейсом

Подключение микросхемы SRAM с параллельным интерфейсом

Подключение микросхемы NAND Flash

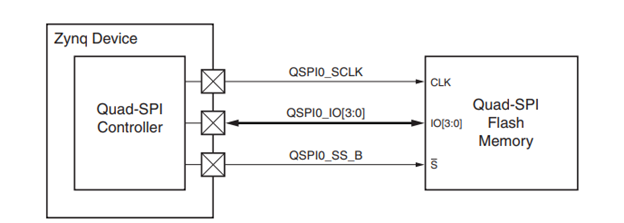

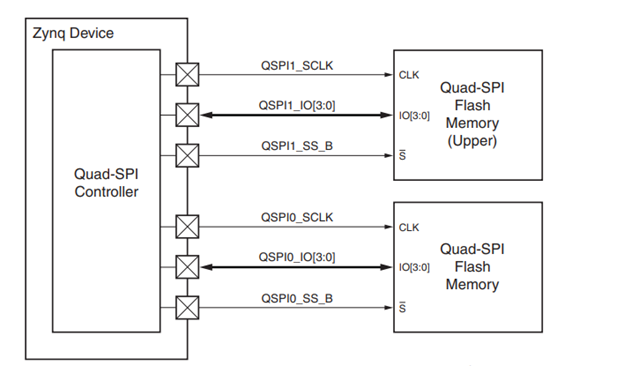

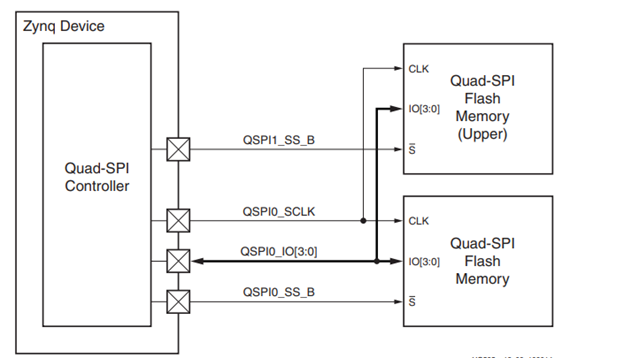

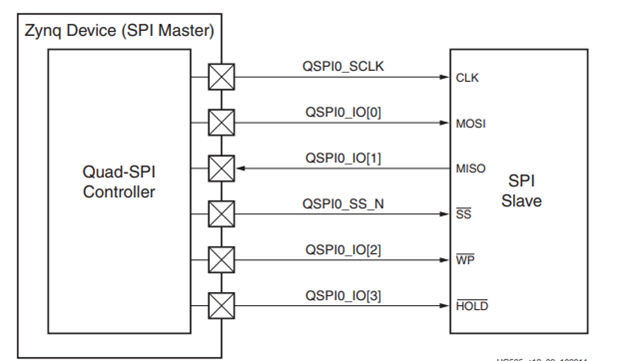

3.2 Quad-SPI Flash Controller

Реализует контроллер SPI для подключения внешних микросхем памяти по технологии NOR. Основные характеристики:

- поддержка Flash-памяти от Micron и Spansion;

- настраиваемая ширина шины (1x, 2x, 4x, 8x);

- тактовая частота до 100 МГц

Возможные режимы работы:

- один сигнал выбора микросхемы (Chip Select / Slave Select), 4 двунаправленных линии для данных;

- два сигнала выбора микросхемы (Chip Select / Slave Select), 8 двунаправленных линий для данных (параллельное включение);

- два сигнала выбора микросхемы (Chip Select / Slave Select), двунаправленных 4 линии для данных (общее включение);

- один сигнал выбора микросхемы (Chip Select / Slave Select), одна линия для передачи, одна линия для приема.

Одна микросхема, 4 двунаправленные линии для обмена данными

Две микросхемы, 8 двунаправленных линий обмена данными

Две микросхемы, 4 двунаправленные линии

Одна микросхема, каждая линия однонаправленная

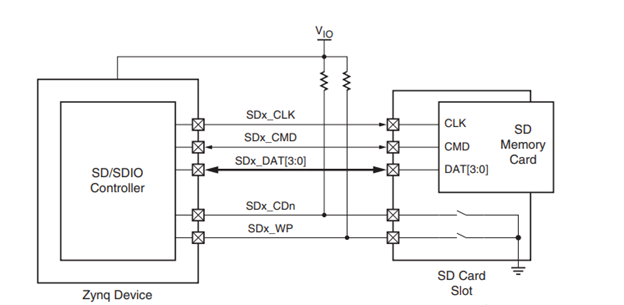

3.3 SD/SDIO Controller

Заявлена поддержка устройств eMMC, но без гарантии, что все будет работать корректно (The Zynq-7000 SoC is expected to work with eMMC devices because the protocol is the same as SD, but this has not been extensively verified). Основные характеристики:

- поддержка спецификации SD Host Controller 2.0;

- поддержка карт стандартов SDHS и SDHC;

- поддержка стандарта MMC3.31;

- режим только Host;

- максимальная тактовая частота 50 МГц;

- режим SPI не поддерживается.

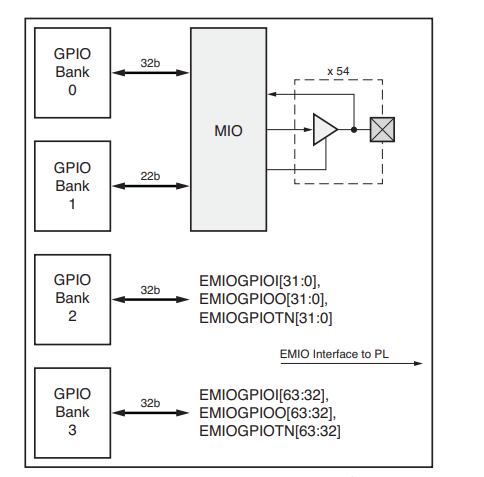

3.4 General Purpose I/O (GPIO)

Каждый из портов можно использовать в следующе режиме:

- вход;

- выход;

- выход с третьим состоянием;

- вход, изменение данных на котором, генерирует прерывание.

Каждый порт можно перенастроить отдельно от других.

Структура блока GPIO

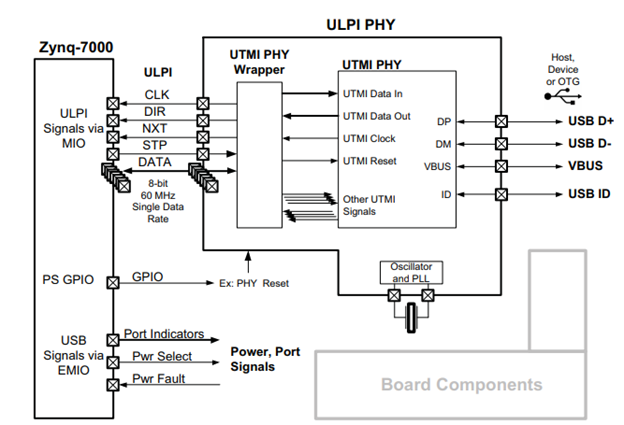

3.5 USB Host, Device, and OTG Controller

Требует внешнюю микросхему физического уровня с интерфейсом ULPI. Основные характеристики:

- поддержка интерфейса 2.0;

- до 12 конечных точек/ Endpoint (одна управляющая и 11 настраиваемых);

- OTG 1.3;

- все типы транзакций (Control, Bulk, Interrupt, Isochronous);

- поддерживаются режимы OTG, USB host, USB device.

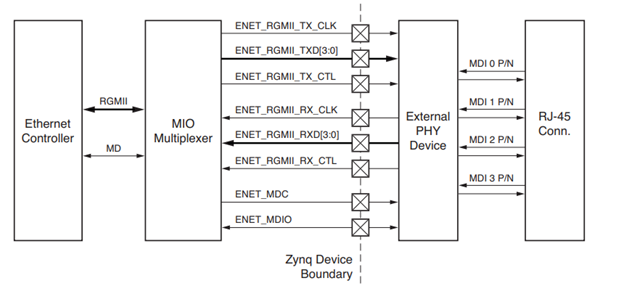

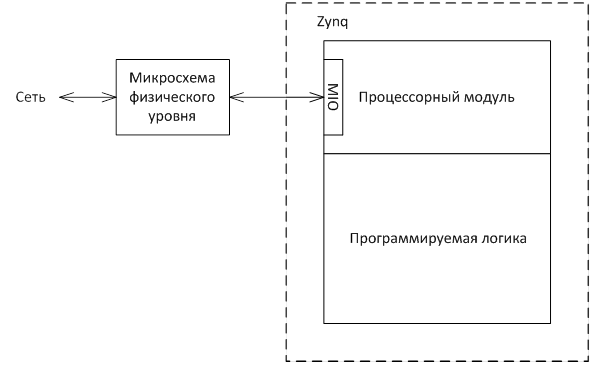

3.6 Gigabit Ethernet Controller

Требует внешнюю микросхему физического уровня с интерфейсом RGMII. Основные характеристики:

- поддержка работы со скоростями 10/100/1000 Мбит/с;

- поддержка режимов Full duplex и half duplex;

- подсчет контрольной суммы для IP, TCP, UDP в версиях протокола IPv4 и IPv6;

- Jumbo Frames не поддерживаются;

- Gigabit Half Duplex не поддерживается;

- поддержка VLAN;

- поддержка Wake-on-LAN.

У каждого контроллера есть свой интерфейс MDIO. Однако при использовании двух контроллеров нельзя использовать два MDIO интерфейса, поскольку они занимают одинаковые выводы MIO 52 и MIO 53. Возможно использование одного интерфейса, подключенного через MIO, а второго через EMIO.

Подключение сетевого контроллера.

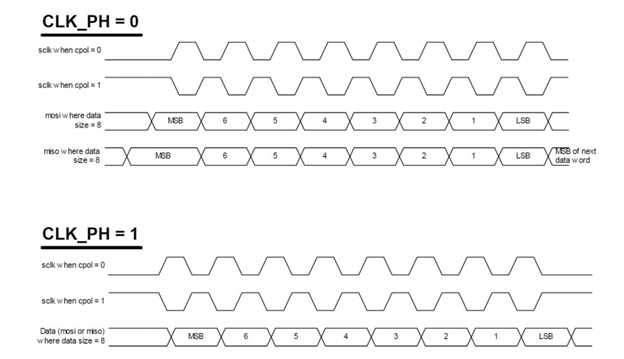

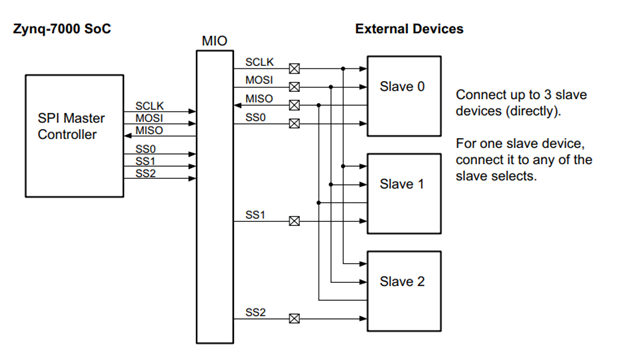

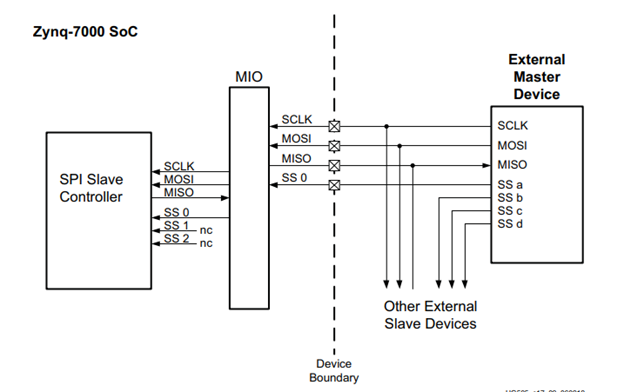

3.7 SPI Controller

Основные характеристики:

- работа в режиме Master, Slave, Multi-Master;

- поддержка работы с тремя устройствами в режиме Master, по 3 линии SS (Slave Select);

- поддержка одновременной передачи и приема;

- тактовый сигнал до 50МГц при использовании MIO, до 25МГц при использовании EMIO;

- настраиваемые режимы фазы тактового сигнала и его полярности (CPHA, CPOL).

Фазы тактового сигнала и полярность

Подключение контроллера SPI в режиме Master

Подключение контроллера SPI в режиме Slave

3.8 CAN Controller

Основные характеристики:

- поддержка стандартов CAN 2.0A, and CAN 2.0B;

- поддержка кадров с длиной идентификатора в 11 и 29 бит;

- скорость до 1 Мбит/с.

Требует внешней микросхемы физического уровня.

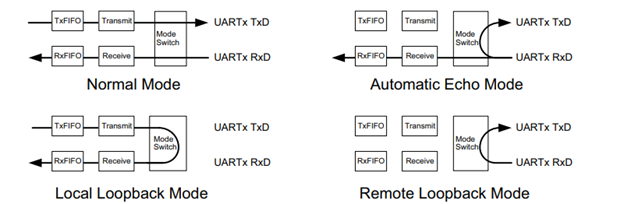

3.9 UART Controller

Основные характеристики:

- настраиваемая скорость передачи;

- настраиваемое количество бит данных – 6, 7, 8;

- настраиваемое количество стоп бит – 1, 1.5, 2;

- контроль четности;

- передача данных в режимах Normal, Automatic Echo, Local Loopback, Remote Loopback.

Режимы работы контроллера UART

3.10 I2C Controller

Основные характеристики:

- скорость обмена до 400 Кбит/с;

- поддержка спецификации версии 2;

- работа в режиме Master и Slave.

3.11 XADC Interface

The Xilinx analog mixed signal module. Аналого-цифровой преобразователь. Имеет в своем составе 2 двенадцатиразрядных АЦП с частотой дискретизации 1 MSPS, аналоговый мультиплексор (до 17 внешних аналоговых каналов), и встроенные датчики температуры и напряжения микросхемы Zynq. Аналоговые входы поддерживают полосу пропускания сигнала до 500кГц при частоте дискретизации в 1 MSPS.

4 Процессорный модуль

Каждый Zynq, как уже было сказано выше, содержит в своем составе одно или два процессорных ядра. Максимальная тактовая частота ядер зависит от класса скорости микросхемы (Speed Grade) [1]. Возможно 5 классов скорости: -1, -1L, -2, -2L, -3. Классы с индексом L характеризуются пониженным напряжением питания.

Количество ядер и зависимость максимальной частоты от класса скорости микросхемы

| Микросхема | Количество ядер | Максимальная тактовая частота, МГц | ||

|---|---|---|---|---|

| -1 | -2 | -3 | ||

| Z-7007S | 1 | 667 | 766 | - |

| Z-7012S | 1 | 667 | 766 | - |

| Z-7014SS | 1 | 667 | 766 | - |

| Z-7010 | 2 | 667 | 766 | 866 |

| Z-7015 | 2 | 667 | 766 | 866 |

| Z-7020 | 2 | 667 | 766 | 866 |

| Z-7030 | 2 | 667 | 800 | 1000 |

| Z-7035 | 2 | 667 | 800 | 1000 |

| Z-7045 | 2 | 667 | 800 | 1000 |

| Z-7100 | 2 | 667 | 800 | - |

5 Программируемая логика

Программируемая логика, используемая в Zynq основана на двух семействах FPGA: Artix-7 и Kintex-7. Artix позиционируется как менее производительное и с меньшим потреблением. Соответственно Kintex более производительно и с большим потреблением. На практике они различаются количеством доступных ресурсов и типом высокоскоростных приемопередатчиков (GTP со скоростью до 6,25 Гбит/с в Artix и GTX со скоростью до 12,5 Гбит/с в Kintex) [2].

Характеристики программируемой логики

| Микросхема | Семейство | Логические ячейки | LUT | Триггеры | BRAM | DSP | GTP/GTX |

|---|---|---|---|---|---|---|---|

| Z-7007S | Artix | 23K | 14400 | 28800 | 50 | 66 | - |

| Z-7012S | Artix | 55K | 34400 | 68800 | 72 | 120 | 4 |

| Z-7014S | Artix | 65K | 40600 | 81200 | 107 | 170 | - |

| Z-7010 | Artix | 28K | 17600 | 35200 | 60 | 80 | - |

| Z-7015 | Artix | 74K | 46200 | 92400 | 95 | 160 | 4 |

| Z-7020 | Artix | 85K | 53200 | 106400 | 140 | 220 | - |

| Z-7030 | Kintex | 125K | 78600 | 157200 | 265 | 400 | 4 |

| Z-7035 | Kintex | 275K | 171900 | 343800 | 500 | 900 | 16 |

| Z-7045 | Kintex | 350K | 218600 | 437200 | 545 | 900 | 16 |

| Z-7100 | Kintex | 444K | 277400 | 554800 | 755 | 2020 | 16 |

LUT (Look-Up Tables) – используются для реализации логических функций.

BRAM (Block RAM) -используются для хранения данных. Размер одного BRAM = 36Кбит.

Примечание. Количество доступных GTP/GTX так же зависит от используемого корпуса. В таблице указано максимальное значение.

6 Производительность

6.1 Теоретическая

В таблицу ниже сведена теоретическая пропуская способность между процессорным модулем и программируемой логикой, а так же пропускная способность памяти. Следует понимать, производительность получена умножением тактового сигнала на ширину интерфейса и не отражает реальную картину передачи данных.

Теоретическая пропускная способность между процессорным модулем и программируемой логикой

| Интерфейс | GP | GP | HP | ACP | DDR | OCM |

|---|---|---|---|---|---|---|

| Тип | PS Slave | PS Master | PS Slave | PS Slave | Внешняя память | Внутренняя память |

| Ширина шины, бит | 32 | 32 | 64 | 64 | 32 | 64 |

| Тактовый сигнал, МГц | 150 | 150 | 150 | 150 | 1066 | 222 |

| Чтение, Мбайт/с | 600 | 600 | 1200 | 1200 | 4264 | 1779 |

| Запись, Мбайт/с | 600 | 600 | 1200 | 1200 | 4264 | 1779 |

| Чтение + запись, Мбайт/с | 1200 | 1200 | 2400 | 2400 | 4264 | 3557 |

| Количество интерфейсов | 2 | 2 | 4 | 1 | 1 | 1 |

| Общая пропускная способность, Мбайт/с | 2400 | 2400 | 9600 | 2400 | 4264 | 3557 |

Теоретическая пропускная способность каналов DMA в процессорном модуле

| DMA | DMAC | Контроллер Ethernet | Контроллер USB | Контроллер SD |

|---|---|---|---|---|

| Тип | ARM PL310 | PS Master | PS Master | PS Master |

| Ширина шины, бит | 64 | 4 | 8 | 4 |

| Тактовый сигнал, МГц | 222 | 250 | 60 | 50 |

| Чтение, Мбайт/с | 1776 | 125 | 60 | 25 |

| Запись, Мбайт/с | 1776 | 125 | 60 | 25 |

| Чтение + запись, Мбайт/с | 3552 | 250 | 60 | 25 |

| Количество интерфейсов | 1 | 2 | 2 | 2 |

| Общая пропускная способность, Мбайт/с | 3552 | 500 | 120 | 50 |

Теоретическая пропускная способность интерконнектов в процессорном модуле

| Interconnect | Тактовый домен | Ширина, бит | Тактовый сигнал, МГц | Чтение, Мбайт/с | Запись, Мбайт/с | Чтение + запись, Мбайт/с |

|---|---|---|---|---|---|---|

| Central Interconnect | CPU_2x | 64 | 222 | 1776 | 1776 | 3552 |

| Masters | CPU_1x | 32 | 111 | 444 | 444 | 888 |

| Slaves | CPU_1x | 32 | 111 | 444 | 444 | 888 |

| Master Interconnect | CPU_2x | 32 | 222 | 888 | 888 | 1776 |

| Slave Interconnect | CPU_2x | 32 | 222 | 888 | 888 | 1776 |

| Memory Interconnect | DDR_2x | 64 | 355 | 2840 | 2840 | 5680 |

Из таблицы следует вывод: память DDR или OCM не может быть полностью загружена одним устройством, исключая случаи использования низкой тактовой частоты для DDR. Пропускная способность чтения DDR ограничена на скорости 2840 Мбайт/с из-за использования Memory Interconnect[3].

6.2 Практическая

Производительность на практике, конечно, оказывается ниже, чем теоретическая. При разработке устройств на базе Zynq нас интересовала производительность обработки сетевых пакетов и производительность порта HP.

6.2.1 Обработка сетевых пакетов

Производительность обработки сетевых пакетов

| Схема включения | Протокол | MTU | TX, Мбит/с | Загрузка процессора, % | RX, Мбит/с | Загрузка процессора, % |

|---|---|---|---|---|---|---|

| PL Ethernet | TCP | 1500 | 824 | 70.7 | 651 | 89.5 |

| TCP | 8192 | 988 | 45.8 | 818 | 55.3 | |

| UDP | 1500 | 583 | 54.4 | 565 | 66.2 | |

| UDP | 8192 | 737 | 33.6 | 876 | 85.8 | |

| PS EMIO | TCP | 1500 | 801 | - | 756 | - |

| PS MIO | TCP | 1500 | 678 | - | 691 | - |

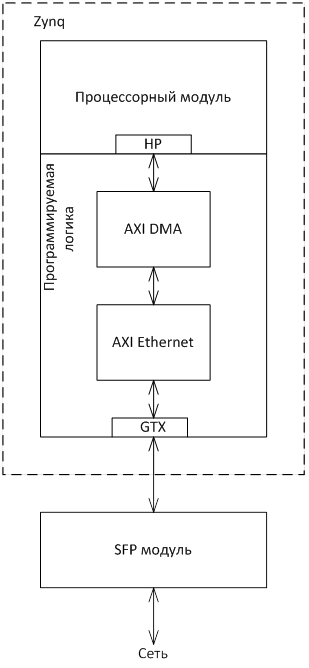

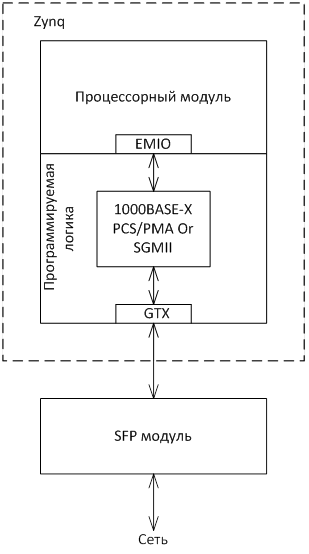

При использовании схемы включения PL Ethernet, используется контроллер, реализованный в программируемой логике. Подключение приведено на схеме ниже. Подсчет контрольных сумм для протоколов IP, TCP, UDP выполняется ядром Axi Ethernet. Процессор используется для генерации и обработки сетевых пакетов. Для теста использовалась операционная система Petalinux с версией ядра 4.19. Замер выполнялся на плате ZC706, на которой установлена микросхема Z-7045 с классом скорости -2. Согласно таблице выше, процессорный модуль содержит 2 ядра и работает на тактовой частоте до 800МГц [4].

При использовании схемы включения PS EMIO, используется контроллер Ethernet, реализованный в процессорном модуле. Подключение приведено на схеме ниже. Подсчет контрольных сумм для протоколов IP, TCP, UDP выполняется ядром в процессорном модуле. Программируемая логика используется с целью преобразования интерфейсов для подключения внешней микросхемы физического уровня. Для теста использовалась операционная система Petalinux с версией ядра 4.6. Замер выполнялся на плате ZC706, на которой установлена микросхема Z-7045 с классом скорости -2. Согласно таблице выше, процессорный модуль содержит 2 ядра и работает на тактовой частоте до 800МГц [5].

При использовании схемы включения PS MIO, используется контроллер Ethernet, реализованный в процессорном модуле. Подключение приведено на схеме ниже. Подсчет контрольных сумм для протоколов IP, TCP, UDP выполняется ядром в процессорном модуле. Подсчет контрольных сумм для протоколов IP, TCP, UDP выполняется ядром в процессорном модуле. Для теста использовалась операционная система Petalinux с версией ядра 4.0. Замер выполнялся на плате Zybo, на которой установлена микросхема Z-7010 с классом скорости -1. Согласно таблице выше, процессорный модуль содержит 2 ядра и работает на тактовой частоте до 667МГц.

Подключение PS MIO

Производительность сетевого контроллера в режиме Rx+Tx

| Схема включения | Протокол | MTU | TX, Мбит/с | RX, Мбит/с |

|---|---|---|---|---|

| PS EMIO | TCP | 1500 | 470 | 218 |

Для теста использовалась операционная система Petalinux с версией ядра 4.14. Замер выполнялся на плате ZC706, на которой установлена микросхема Z-7045 с классом скорости -2. Согласно таблице выше, процессорный модуль содержит 2 ядра и работает на тактовой частоте до 800МГц [6].

Итого: если необходимо обеспечить обработку сетевых пакетов со скоростью 1Гбит/с, то Zynq не подходит для этой задачи.

6.2.2 Производительность порта HP

Теоретическая пропускная способность порта HP составляет 9,6Гбит/с. Для проверки пропускной способности использовалась плата Mini-ITX, на которой установлена микросхема Z-7100 с классом скорости -2. Согласно таблице выше, процессорный модуль содержит 2 ядра и работает на тактовой частоте до 800МГц. Операционная система Petalinux с версией ядра 3.19. Подключение приведено на схеме ниже.

Схема подключения для оценки скорости порта HP

Root Complex PCI-Express был реализован в программируемой логике с помощью ядра Axi PCIE. Процессорный модуль используется для обработки полученных пакетов. При таком подключении скорость чтения данных с флешки составляла чуть больше 100Мбайт/с.

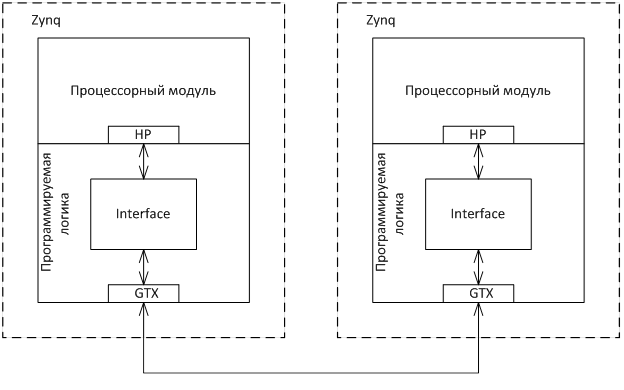

При использовании порта HP для соединения двух микросхем Zynq по схеме ниже, скорость передачи данных скорость передачи достигает 2,5Гбит/с (ограничение блока Interface).

Итого: порт HP позволяет организовать высокоскоростную передачу данных из процессорного модуля в программируемую логику и обратно.

7 Передача данных между процессорным модулем и программируемой логикой

Методы передачи данных

| Метод | Преимущества | Недостатки | Используется для | Расчетная пропускная способность |

|---|---|---|---|---|

| CPU Programmed I/O (GP) | Простое программное обеспечение. Небольшое использование ресурсов в PL. Простые устройства в PL | Низкая пропускная способность | Функций управления | <25Мбайт/с |

| PS DMAC | Небольшое использование ресурсов в PL. Средняя пропускная способность. Несколько каналов. Простые устройства в PL | Несколько сложное программирование DMA | Организации DMA при ограниченном количестве ресурсов в PL | 600 Мбайт/с |

| PL AXI_HP DMA | Высокая пропускная способность. Несколько интерфейсов | Доступ только к OCM/DDR. Более сложные устройства в PL. | Высокопроизводительного DMA для больших наборов данных. | 1200 Мбайт/с на каждый канал |

| PL AXI_ACP DMA | Высокая пропускная способность. Низкая задержка. Поддержка когерентности кэша. | Большой объем данных может переполнить кэш. Использует пропускную способность с CPU Interconnect. Более сложные устройства в PL | Высокопроизводительного DMA для небольших когерентных наборов данных. Уменьшения загрузки процессора. | 600 Мбайт/с |

| PL AXI_GP DMA | Средняя пропускная способность | Более сложные устройства в PL. | Функций управления из PL в PS.Доступ к I/O. | 600 Мбайт/с |

На диаграммах ниже серым цветом выделены блоки, которые участвуют в передаче данных.

Путь передачи данных через Master GP (CPU Programmed I/O)

Путь передачи данных через Master GP (PS DMAC)

Путь передачи данных через HP (PL AXI_HP DMA)

Путь передачи данных для ACP (PL AXI_ACP DMA)

Из всех возможных методов передачи данных между процессорным модулем и программируемой логикой, мы используем только 2: CPU Programmed I/O и PL AXI_HP DMA о которых будет рассказано в отдельной статье.

8 Загрузка SoC

После снятия сигнала сброса (PS_POR_B), процессорный модуль считывает со специальных входов режим загрузки и запускает на выполнение код BootROM. BootROM предназначен для начальной настройки системы, копирования следующего загрузчика в OCM (On Chip Memory) и передачи управления следующему загрузчику.

Возможные режимы загрузки:

- Quad-SPI;

- SD Memory Card;

- NAND;

- NOR;

- JTAG.

Хорошая статья от Xilinx, в которой перечислены виды загрузки и протестированные варианты www.xilinx.com/support/answers/50991.html

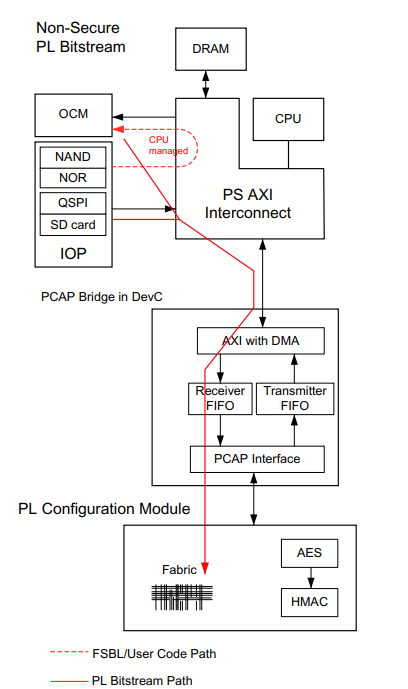

Если режим загрузки не JTAG, то BootROM ищет на устройстве загрузки следующий загрузчик – FSBL (First State Boot Loader). FSBL используется для дальнейшей настройки системы (инициализация DDR, инициализация MIO). Также, FSBL используется для загрузки файла конфигурации в программируемую логику, если это необходимо. Файл конфигурации считывается с устройства загрузки и через специальный интерфейс(PCAP) в режиме DMA передается в программируемую логику. После загрузки программируемой логики, FSBL ищет следующее приложение для передачи управления. Возможны несколько вариантов:

- следующего приложения нет, FSBL останавливается;

- следующее приложение — приложение пользователя (Bare Metal). Оно вычитывается в DDR, и ему передается управление;

- следующее приложение – U-BOOT. U-BOOT вычитывается в DDR и ему передается управление.

Таким образом, без процессорного модуля нельзя загрузить файл конфигурации в программируемую логику за исключением случая использования JTAG.

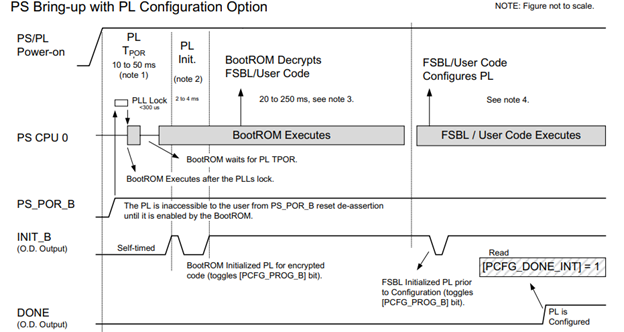

Временная шкала включения Zynq

Время выполнения BootROM сильно зависит от пропускной способности интерфейса устройства, на котором хранится файл конфигурации.

Сигнал INIT_B используется для указания, что начато конфигурирование программируемой логики (загрузка файла конфигурации).

Сигнал DONE используется для указания, что конфигурирование программируемой логики завершено.

Загрузка конфигурации в программируемую логику

9 Проблемы

При разработке устройств на базе Zynq столкнулись с несколькими проблемами. Возможно, в этом виновато плохое чтение документации.

- При работе с контроллером Ethernet, реализованном в процессорном модуле, напряжение питания банка должно быть +1,8В или +2,5В.

- При использовании Petalinux возможна загрузка только с использованием SD-карты.

- Не только Zynq, а вся седьмая серия от Xilinx (Artix, Kintex). Невозможно сформировать дифференциальный сигнал в банке с напряжением питания +3,3В.

10 Создание файла конфигурации

Как создать прошивку для Zynq? Для этого потребуется два инструмента от Xilinx: Vivado и Vitis. Так же добавим bare-metal приложение, которое передаст привет миру.

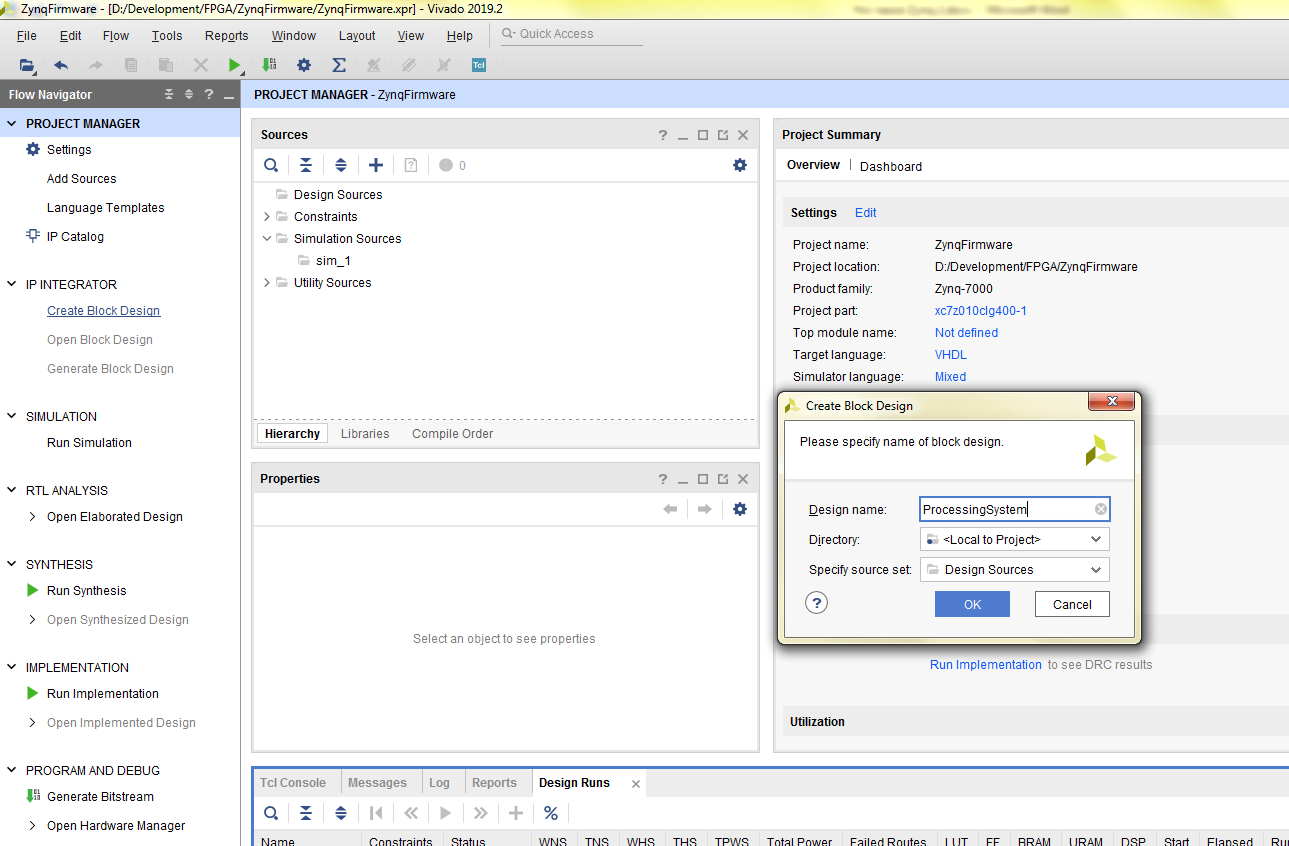

- Запустить Vivado. Создать проект для выбранной микросхемы. В примере будет использоваться плата Zybo, на которой установлена микросхема XC7Z010-1CLG400C.

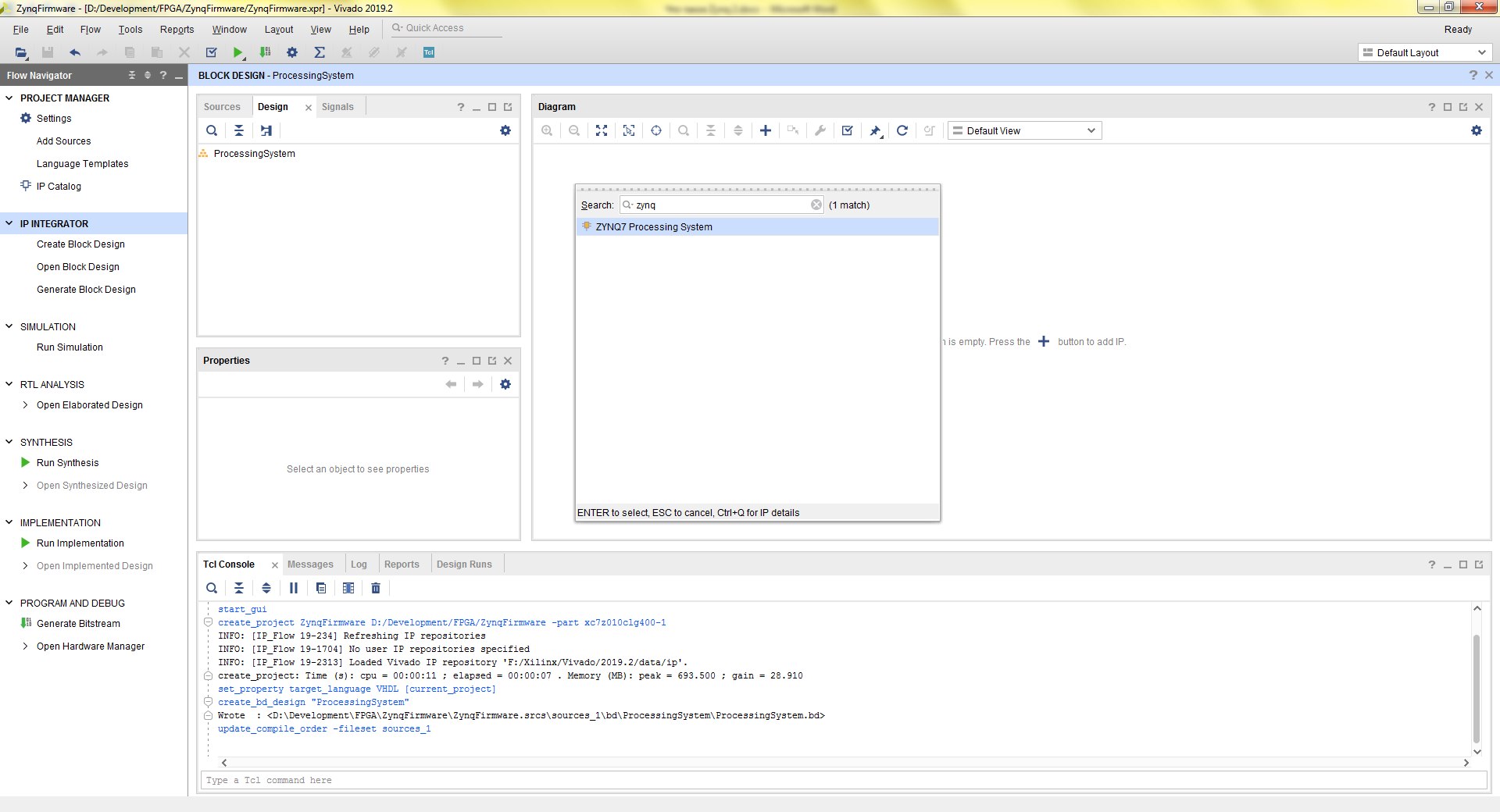

- В меню слева (если его нет, то включить можно в View => Show Flow Navigator) выбрать Create Block Design => ввести имя файла => OK.

- В открывшемся окне Diagram нажать на «+» или воспользоваться сочетанием клавиш Ctrl + I. В появившимся окне выбрать блок Zynq7 Processing System.

- Вверху окна нажать на «Run Block Automation», появившимся окне нажать OK.

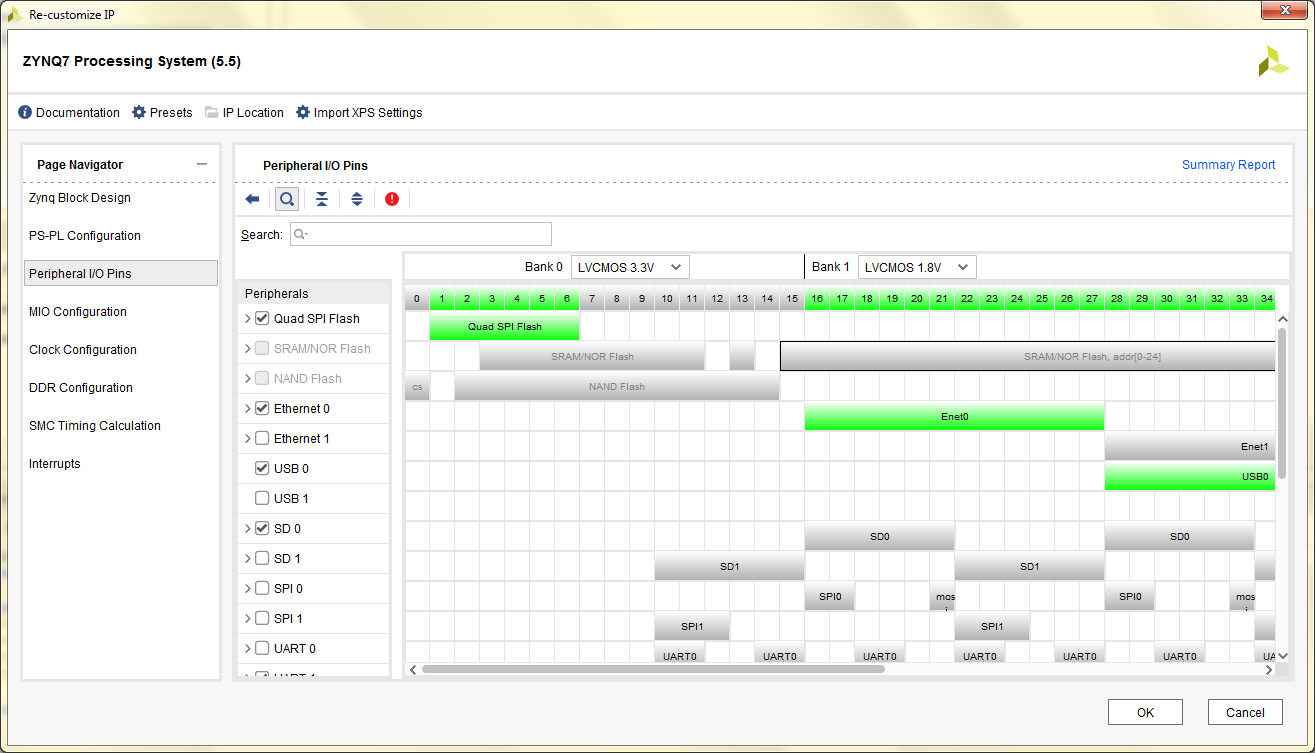

- Двойной клик на Zynq7 Processing System (или правой кнопкой и пункт Customize Block). Если создается прошивка для покупной платы, то в комплекте с ней есть xml или tcl файл с настройками процессорного модуля. Его можно загрузить через пункт Import XPS Settings и указав путь к файлу. Иначе, необходимо по принципиальной схеме на устройство выяснить, какие MIO используются и куда подключены, какой тип памяти DDR и выставить соответствующие настройки во вкладках Peripheral I/O Pins, MIO Configuration, Clock Configuration и DDR Configuration.

- В принципе, этого достаточно. Но если сейчас запустить синтез, Vivado выдаст критическую ошибку о неподключенном входе. Потому что по умолчанию включен вход GP0. Снова двойной клик на Zynq7 Processing System => PS-PL Configuration => Axi Non Secure Enablement => GP Master AXI Interface => снять галку с M AXI GP0 Interface => OK.

- File => Save Block Design. Вкладку можно закрыть.

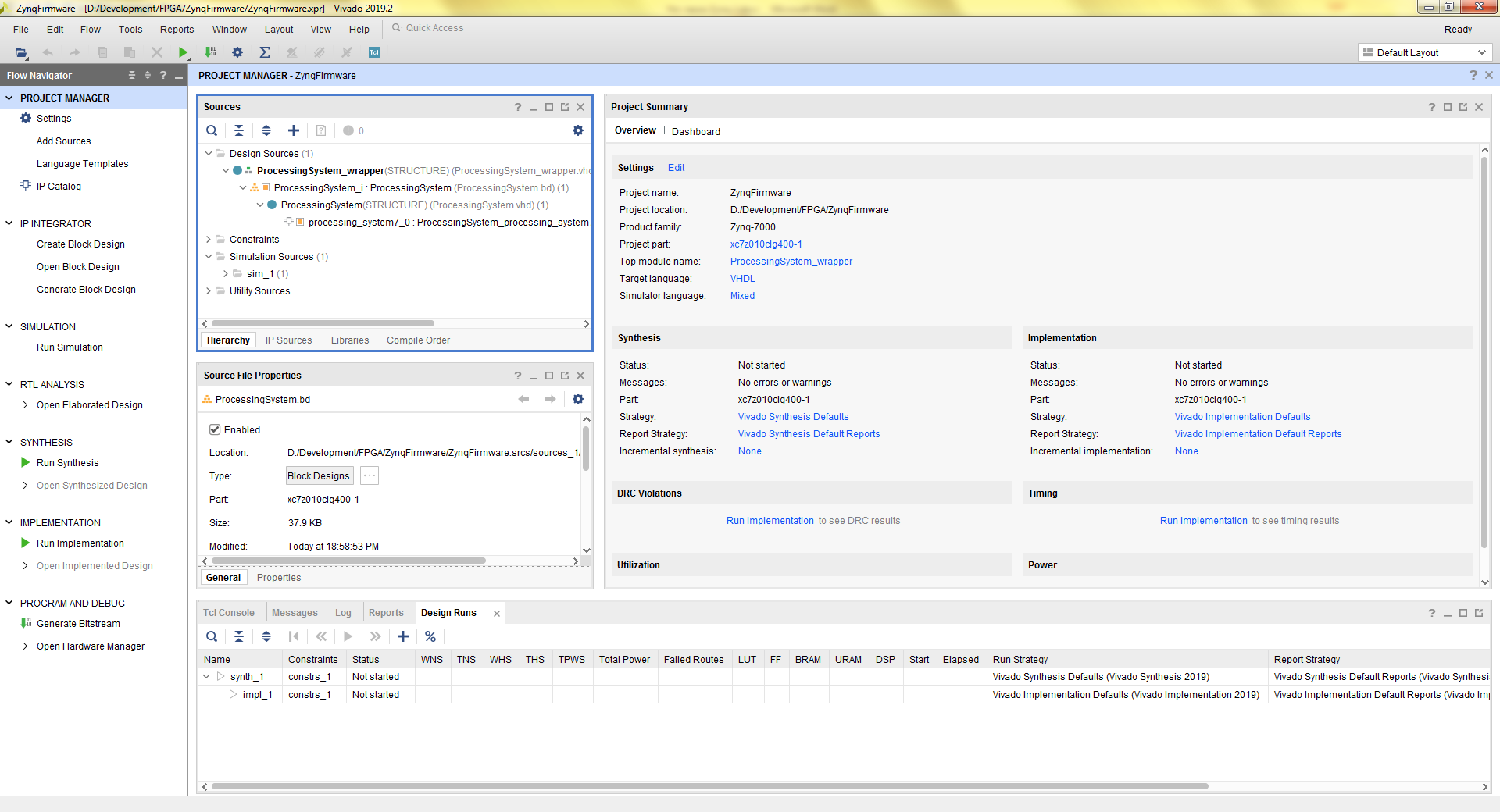

- В вкладке Sources выбрать созданный файл, правый клик, Create HDL Wrapper. В окне выбрать нужный пункт (включить автообновление файла или нет, неважно), OK.

- В меню слева выбрать Generate Bitstream => Yes => OK.

- После некоторого времени появится окно «Bitstream Generation Completed», которое нужно закрыть.

- Необходимо создать каталог, в котором будут храниться FSBL и bare-metal приложение. Можно хранить их в папке с проектом или в другом месте.

- В Vivado File => Export => Export Hardware. Указать путь к созданному каталогу, галку Include bitsteam ставить не обязательно. В созданном каталоге появится файл .xsa

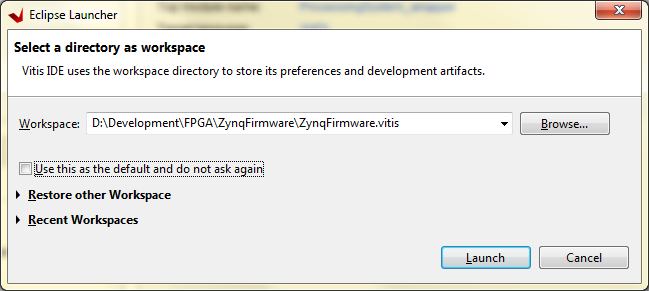

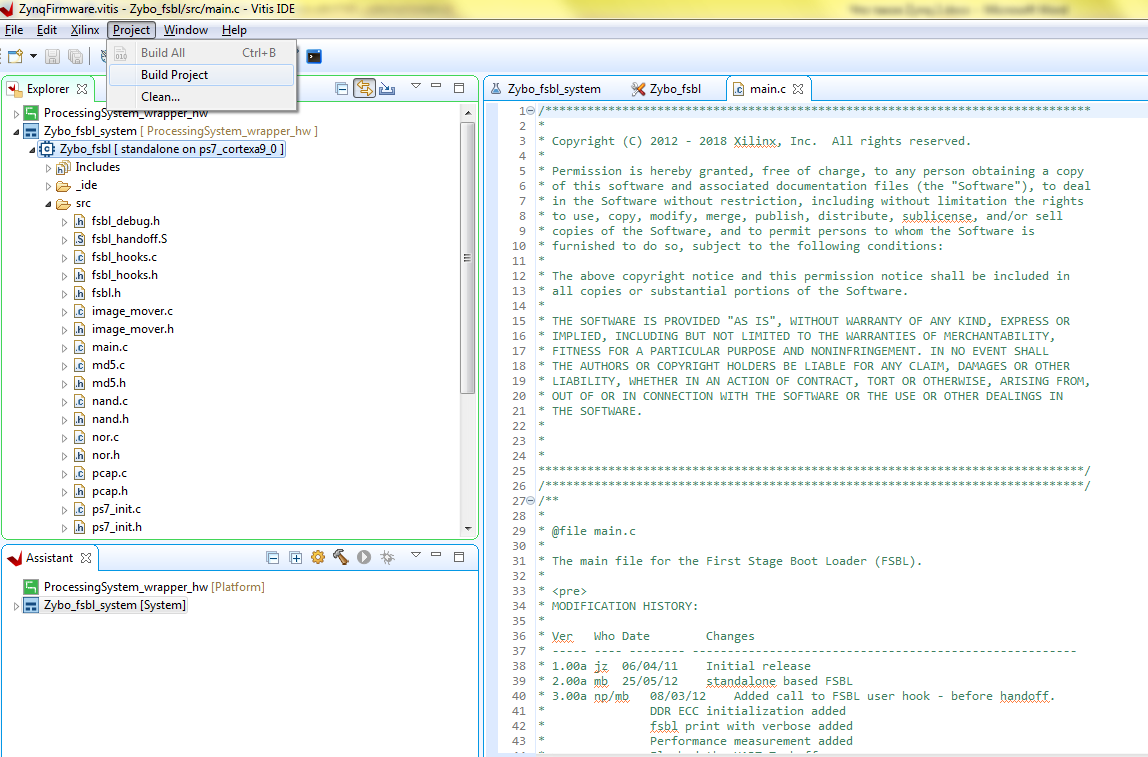

- Запустить Vitis (можно из Vivado => Tools => Launch Vitis), указать путь к каталогу с .xsa файлом.

- В Vitis File => New => Application Project. В поле Project Name задать, например, Zybo_fsbl, нажать Next, выбрать вкладку Create a new platform form hardware (XSA), нажать «+», указать путь к файлу .xsa, в поле Platform name ввести название, чтобы потом можно было отличить созданную платформу от платформ по-умолчанию, например ProcessingSystem_wrapper_hw, Next, снять галку Generate boot components => Next => в списке шаблонов выбрать Zynq FSBL => Finish.

- В окне слева (Explorer) развернуть каталог src, открыть файл main.c. Можно добавить define, чтобы видеть, что процессорный модуль запустился.

#define FSBL_DEBUG #include "fsbl.h" #include "qspi.h" - Выбрать файл Zybo_fsbl, меню Project => Build Project.

- FSBL создан. Теперь приложение. File => New => Application Project. В поле Project Name задать, например, Zybo_hello, Next, во вкладке Select a platform from repository выбрать созданную ранее платформу ProcessingSystem_wrapper_hw, Next, Next, в списке шаблонов выбрать Hello World, Finish.

- Выбрать файл Zybo_hello, меню Project => Build Project.

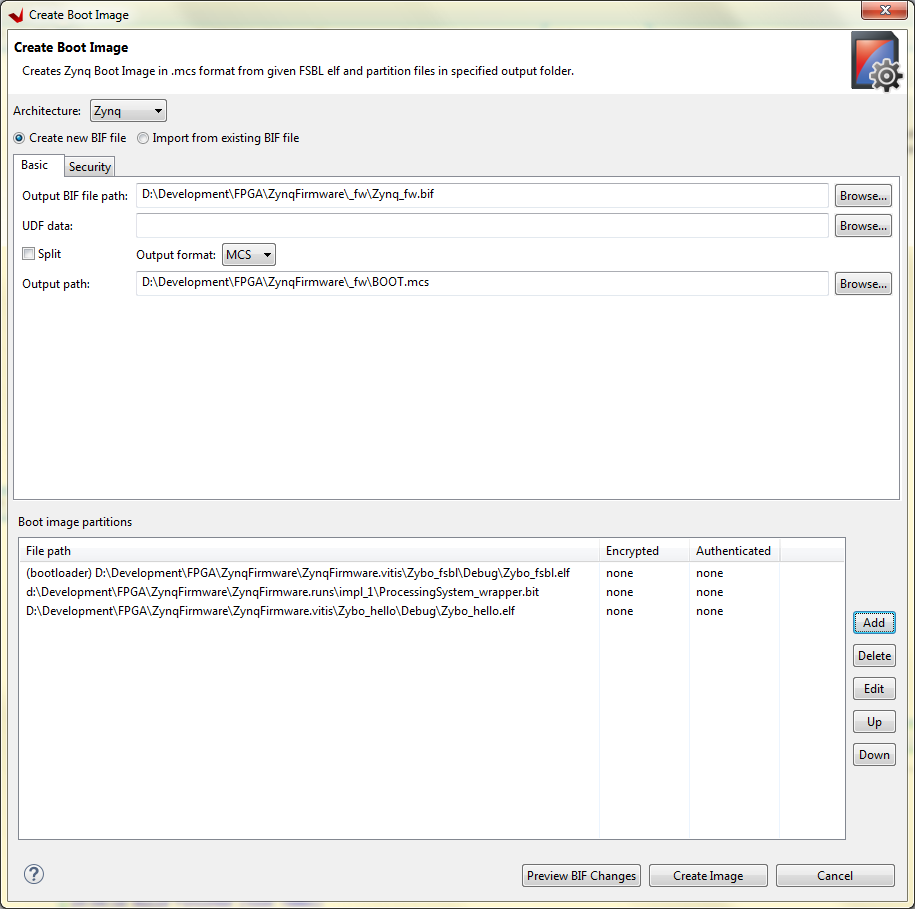

- Приложение создано. Теперь необходимо собрать итоговый файл. В Vitis выбрать меню Xilinx => Create Boot Image. Оставить переключатель в положении Create new BIF file. В поле Output BIF file path с помощью кнопки Browse указать место хранение файла и имя файла.

- Выбрать выходной формат файла, mcs или bin и путь для хранения файла

- Нажать кнопку Add и указать путь к файлу Zybo_fsbl.elf (исполняемый файл FSBL). Он расположен в папке с проектом Zybo_fsbl, каталог Debug, остальные поля оставить без изменений.

- Нажать кнопку Add и указать путь к файлу bit. Если была установлена галка Include bitsteam, то bit файл можно найти в каталоге с файлом .xsa, далее каталог с названием платформы, далее каталог bitstream. Если галки не было, то bit файл расположен в каталоге проекта, каталог .runs, каталог impl_1. Остальные поля оставить без изменений.

- Нажать кнопку Add и указать путь к файлу Zybo_hello.elf, который расположен по аналогии с FSBL в каталоге Debug. Остальные поля оставить без изменений.

- Нажать кнопку Create Image. Файл конфигурации создан.

Если полученный файл конфигурации прошить в плату, подключиться монитором com-порта к отладочном порту Zynq, то в мониторе com-порта можно увидеть следующее:

Xilinx First Stage Boot Loader

Release 2019.2 Jun 26 2020-09:16:22

Silicon Version 3.1

Boot mode is QSPI

SUCCESSFUL_HANDOFF

FSBL Status = 0x1

Hello World

11 Заключение

Вывод: SoC Zynq подходит для решения задач, которые не требуют высокой производительности от процессорного модуля. Идеальный случай, когда алгоритм обработки данных реализован в программируемой логике, а процессорный модуль используется для загрузки данных, или обработки исключительных ситуаций, реализация которых трудоемка в программируемой логике.

12 Используемые источники

- www.xilinx.com/support/documentation/data_sheets/ds190-Zynq-7000-Overview.pdf

- www.xilinx.com/support/documentation/selection-guides/zynq-7000-product-selection-guide.pdf

- www.xilinx.com/support/documentation/user_guides/ug585-Zynq-7000-TRM.pdf

- xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18842485/Linux+AXI+Ethernet+driver

- xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18841613/XAPP1082+2017.4+Performance

- www.xilinx.com/support/answers/73065.html

Автор: Павел