5 нм против 3 нм

Промежуточные техпроцессы, разные типы транзисторов, и множество других вариантов добавляют неопределённости в процесс производства электроники

Производители электроники готовятся к следующей волне передовых техпроцессов, но их клиенты столкнутся с кучей сбивающих с толку вариантов – разрабатывать ли чипы по техпроцессу 5 нм, подождать 3 нм, или выбрать нечто среднее.

Путь к 5 нм хорошо определён, в отличие от 3 нм. После этого ландшафт становится запутанным, поскольку фабрики добавляют промежуточные техпроцессы, типа 6 нм и 4 нм. Переход на любые из этих техпроцессов весьма дорог, а преимущества не всегда очевидны.

Ещё один повод для беспокойства – сжимающаяся производственная база. В случае самых передовых техпроцессов выбор производителей оказывается невелик. В индустрии раньше было несколько ведущих производителей, но со временем эта область сузилась из-за резко возросшей стоимости и сокращения пользовательской базы. В целом, чем меньше производителей, тем меньше вариантов по технологиям и ценнику.

Сегодня Samsung и TSMC – два единственных производителя [1], работающих с техпроцессами 7 нм и ниже, хотя это может поменяться. Intel и китайская компания SMIC разрабатывают передовые техпроцессы. Intel, не самый крупный игрок в области коммерческого производства, испытывает проблемы с разработкой техпроцесса в 10 нм. И неясно, получится ли у SMIC выдать 7 нм, поскольку эта тема пока находится в стадии исследований и разработок (то же самое происходит у Intel с техпроцессом 10 нм).

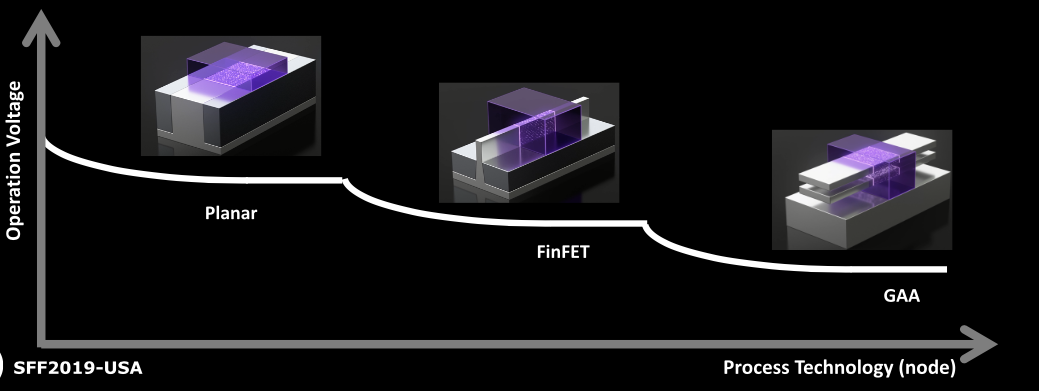

Что касается более передовых техпроцессов, Samsung и TSMC работают с 7 нм, используя транзисторы finFET, и оба производителя собираются продолжать это и на 5 нм. В отличие от традиционных планарных транзисторов, finFET – это трёхмерные структуры, с лучшей производительностью и меньшими утечками.

Затем на 3 нм Samsung перейдёт от finFET к новой архитектуре транзисторов, нанослойным FET [nanosheet FET], представляющим собой развитие технологии finFET. TSMC пока не раскрывает своих планов на 3 нм, оставляя многих клиентов в подвешенном состоянии. TSMC, по информации источников, взвешивают разные возможности, включая нанослои, нанопровода и форсированные finFET. Intel, TSMC и другие также работают над новыми формами передовой упаковки в качестве возможных вариантов уменьшения масштаба.

Тем не менее, на 3 нм размере транзисторные технологии могут пойти в разных направлениях. finFET пока ещё могут сыграть, но этой технологии требуется сделать некоторые прорывы. Судя по всему, индустрии придётся готовиться к переходу на новую архитектуру 3 нм техпроцесса, и следующего промежуточного техпроцесса на 2 нм, судя по планам развития одной организации, работающей в этой области.

«5 нм – это всё ещё finFET, — сказал Наото Хоригучи, программный директор в Imec. – Допустим, что на 3 нм мы вступим в переходный период от finFET к другим архитектурам. Мы считаем, что это будут нанослои».

Нанослойные FET относятся к архитектуре транзисторов с круговым затвором (gate-all-around, GAA). И это не единственный из возможных вариантов. «Индустрия весьма консервативная. Её участники попытаются выжать из finFET всё до предела, — сказал Хоригучи. – На техпроцессе 3 нм у нас есть возможность использовать finFET. Но нам потребуется совершить несколько инноваций finFET, улучшить его в общем и целом».

Останутся ли производители чипов на техпроцессе 7 нм, мигрируют до 5 нм, 3 нм или до промежуточного? 7 нм обеспечивает достаточно производительности практически для всех применений, поэтому этот техпроцесс будет жить ещё долго. За его пределами существует несколько высокопроизводительных вариантов, и все они стоят дороже. И мы ещё посмотрим, успеют ли эти технологии появиться вовремя.

Рабочее напряжение разных техпроцессов – планарные транзисторы, finFET и нанослойные FET.

Разорение производств

Чип состоит из множества транзисторов, играющих роль переключателей. Много десятилетий прогресс интегральных схем соответствовал закону Мура, по которому плотность транзисторов на устройстве удваивается в срок от 18 до 24 месяцев.

В подобном ритме производители вводили новые техпроцессы с большей плотностью транзисторов, что позволяло индустрии снижать стоимость чипов в пересчёте на количество транзисторов. На каждом техпроцессе производители масштабировали спецификации транзисторов в 0,7 раз, позволяя индустрии увеличивать производительность на 40% при том же энергопотреблении и при двукратном уменьшении площади.

Индустрия интегральных схем следовала этой формуле и процветала. С 1980-х годов она прокладывала путь к быстрым ПК по снижающимся ценам.

К 2001 году существовало уже не менее 18 производителей с фабриками, где они могли производить чипы на 130 нм, что в то время было передовым техпроцессом, согласно IBS. Также тогда появлялось ещё несколько новых производителей, делавших чипы на заказ на чужих фабриках. Кроме того, практиковалось производство чипов для лабораторий, их разрабатывавших, но не имевших собственного производства.

К концу десятилетия стоимость производства и техпроцессы рванули ввысь. Не справившись с ростом цен, многие производители чипов перешли на модель fab lite. Они производили некоторые чипы у себя, а остальные отдавали на аутсорс.

Со временем всё меньше производителей чипов делали передовые устройства на собственных мощностях. Некоторые полностью избавились от производств или вышли из этого бизнеса.

Тем не менее, в 2000-х появилась бизнес-модель кремниевых мастерских. Мастерские отставали от Intel и других компаний по технологиям, но давали проектным компаниям доступ к различным процессам.

Следующее крупное изменение случилось на этапе в 20 нм, когда традиционные планарные транзисторы упёрлись в стенку и столкнулись с эффектом короткого канала [2]. В ответ Intel в 2011 году перешла на транзисторную технологию следующего поколения, finFET, на 22 нм. Мастерские перешли на finFET на 16/14 нм.

У finFET есть несколько преимуществ по сравнению с планарными транзисторами. «В этой схеме весь транзистор вытягивается по вертикали так, что канал возвышается над подложкой, и вентиль обёртывается вокруг трёх сторон плавника. Увеличенная площадь контакта вентиля позволяет лучше контролировать ток утечки», — пишут Мэтт Когорно и Тошихико Мияшита из Applied Materials. Когорно – директор глобального менеджмента продукта, а Мияшита – главный технолог.

FinFET ещё и более сложные устройства, их сложнее производить и масштабировать на каждый следующий техпроцесс. В итоге, стоимость R&D выросли до небес. Так что теперь ритм полноценной смены техпроцесса вырос с 18 месяцев до 2,5 лет и более.

Цены на интегральные схемы также продолжают расти. Стоимость разработки планарного устройства на 28 нм разнится от $10 млн до $35 млн, как пишет Gartner. Для сравнения, стоимость проектирования однокристальной системы (SoC) на 7 нм разнится от $120 млн до $420 млн.

«Стоимость разработки сильно зависит от сложности SoC,- сказал Сэмюел Вэн, аналитик из Gartner. – Две трети уходят на разработку чипа. Остальное – разработка ПЛ, стоимость масок и улучшение выхода. Со временем стоимость проектирования тоже падает».

Тем не менее, тенденции цен изменили ландшафт мира интегральных микросхем. Со временем всё меньше компаний могут позволить себе оплачивать проектирование чипов для самых передовых техпроцессов. Многие из них полагаются в вопросах производства на мастерские.

Уменьшение количества клиентов вместе с ростом стоимости производства повлияли на ландшафт мастерских, производящих передовые чипы. К примеру, на рынке 16/14 нм осталось пять производителей/мастерских: GlobalFoundries, Intel, Samsung, TSMC и UMC. SMIC также работает с finFET на техпроцессе 14 нм.

А на 7 нм случился другой переход. Техпроцессы и стоимость производства продолжали расти, а прибыль на инвестиции была уже под вопросом. В итоге GlobalFoundries и UMC в прошлом году прекратили попытки разработать техпроцесс на 7 нм. Обе компании продолжают работать на рынке 16/14 нм.

Пытаясь развиваться дальше, Samsung и TSMC на полной скорости мчатся к рубежу 7 нм и за его пределы. После нескольких задержек, Intel планирует запустить производство на 10 нм в середине 2019 года, а на 7 гм – к 2021-му. SMIC тем временем не обещает никаких сроков.

Но не всем клиентам мастерских требуются передовые техпроцессы. Существует процветающий рынок для чипов на 28 нм. «Всё зависит от характеристик продукта, — сказал Вэн из Gartner. – Некоторым продуктам требуется максимальное быстродействие. Разработчики всё ещё могут использовать устаревшие техпроцессы. А чипы для применений, не требующих высокой производительности, могут жить и на техпроцессах N-1 и N-2».

Ему вторят другие. «Сколько компаний могут позволить себе новейший кремний сегодня с экономической точки зрения? Их количество уменьшается. На рынках, требующих чрезвычайно высокого быстродействия такая потребность будет всегда. Но в цепочке поставок, с точки зрения объёмов, в середине образуется разлом. Самым требовательным клиентам требуются техпроцессы на 7, 5, а возможно, когда-нибудь и 3 нм. Но все остальные немного притормозили», — сказал Уолтер Ын, вице-президент по бизнес-управлению в UMC.

Но в определённых случаях существует необходимость в самых передовых чипах – это серверы и смартфоны. Также появляется море новых стартапов, связанных с ИИ-чипами. Многие компании проектируют чипы для машинного обучения и глубокого обучения.

«Никто не спорит, что потребность считать что-либо в 10 раз быстрее, чем сегодня, всегда будет коммерчески полезной и конкурентоспособной, даже на не технических рынках. Тому свидетельством являются все эти уникальные достижения технологии глубокого обучения. Запросам на всё большую компьютерную мощность буквально не видно конца», — сказал Аки Фуджимура, директор D2S.

«Запросы на вычислительные мощности испытывали несколько крупных сдвигов – сначала это были GPU, а позднее – глубокое обучение, — сказал Фуджимура. – Глубокое обучение – это массивная технология поиска подходящих закономерностей, а обучение нейросетей – это задача последовательной оптимизации. Сейчас, когда мир придумал механизм обработки огромного количества данных и превращения их в полезную информацию в виде программы, способной к логическим умозаключениям, количество необходимых вычислений растёт вместе с количеством доступных данных. А поскольку количество данных во всех областях растёт в геометрической прогрессии, требования к вычислительным мощностям гарантированно значительно вырастут как минимум в области глубокого обучения».

Требуют ли чипы ИИ техпроцессов в 5 нм и дальше, остаётся неясным, но требования к увеличению вычислительных мощностей определённо существуют. Но миграция на эти техпроцессы не становится более лёгким или дешёвым процессом.

5 нм против 3 нм

Тем временем в начале 2018 TSMC достигла очередной вехи, став первым в мире производителем, задействовавшим техпроцесс на 7 нм. Позднее в гонку 7 нм включилась Samsung. Процесс изготовления чипов на 7 нм в основном базируется на finFET, и состоит из изготовления чипов с шагом затвора от 56 до 57 нм и минимальный шаг размещения металлических проводников [metal pitch] на 40 нм, согласно информации IC Knowledge and TEL.

В первой версии 7 нм TSMC использовала иммерсионную литографию [3] на 193 мм и мультипаттеринг [multiple patterning]. В этом году TSMC обещает выпустить новую версию 7 нм с использованием экстремальной ультрафиолетовой литографии (EUV). EUV упрощает шаги техпроцесса, но это дорогая технология и у неё есть свой набор трудностей.

TSMC готовит свой новый техпроцесс на 5 нм к выходу в первой половине 2020 года. Новая технология от TSMC на 5 нм будет на 15% быстрее, чем 7 нм, и потреблять на 30% меньше энергии. Вторая версия техпроцесса 5 нм, выходящая в следующем году, будет на 7% быстрее. Обе версии будут использовать EUV.

TSMC уже набирает заказов на 5 нм. «Ожидается поступление крупных заказов от Apple, HiSilicon и Qualcomm, — сказал Хэндел Джонс, директор IBS. – Объёмы подложек составят 40 000 – 60 000 в месяц к четвёртому кварталу 2020».

Скорость перехода на 5 нм у TSMC оказывается меньше, чем на 7 нм. Во-первых, 5 нм – полностью новый процесс, с обновлёнными инструментами EDA и патентами. Кроме того, он дороже. В среднем стоимость разработки устройства на 5 нм варьируется от $210 млн до $680 млн, согласно Gartner.

Некоторые производители чипов хотят уйти от 7 нм, не тратя столько денег, сколько стоит 5 нм. Поэтому TSMC недавно представила новый промежуточный техпроцесс 6 нм, стоящий дешевле, но имеющий несколько компромиссов.

«Кажется, что числа N6 и N5 не отличаются, но на самом деле разрыв большой, — сказал С. С. Вей, директор TSMC на последнем совещании. – У N5, по сравнению с N7, логическая плотность увеличена на 80%. У N6 по сравнению с N7 всего на 18%. Как видно, существует большая разница между логической плотностью и эффективностью транзисторов. В итоге общее энергопотребление у чипа N5 ниже. У перехода на N5 есть много преимуществ. Но N5 – полноценный техпроцесс, и на разработку новых продуктов под него у клиентов уходит время. Прелесть N6 в том, что если у них уже есть проект под N7, то придётся потратить совсем мало усилий. Они могут перейти на N6 и получить определённые преимущества. И в зависимости от характеристик продукта и рынка, клиенты решат, что им делать».

Тем временем Samsung выкатила 5 нм, который появится в первой половине 2020. По сравнению с 7 нм, новый техпроцесс 5 нм от Samsung на finFET даёт до 25% уплотнения логики и на 20% меньше энергопотребления, или на 10% больше скорости работы.

Также Samsung представила новый промежуточный техпроцесс 6 нм, давая клиентам ещё один вариант. «У 6 нм есть преимущество масштабируемости с 7 нм и повторного использования интеллектуальной собственности», сказал Райан Ли, вице-президент по маркетингу мастерских Samsung. А в планах Samsung есть уже разработка техпроцесса finFET на 4 нм. Пока что по этой технологии практически нет открытой информации.

После 5 нм в ряду полноценных техпроцессов стоит 3 нм. Но 3 нм не для слабаков. Стоимость разработки устройства по техпроцессу 3 нм варьируется от $500 млн до $1,5 млрд, согласно IBS. Стоимость процесса разработки варьируется от $4 млрд до $5 млрд, а производства – от $15 до $20. «Стоимость 3 нм транзисторов должна быть на 20-25% больше, чем у 5 нм того же уровня готовности, — сказал Джонс из IBS. – Можно ожидать повышения эффективности на 15% и уменьшения энергопотребления на 25% по сравнению с 5 нм finFET».

Samsung – единственная компания, объявившая о планах по разработке техпроцесса 3 нм. Для этого мастерская перейдёт на архитектуру транзисторов с круговым затвором, нанослои. TSMC пока не раскрывает планов, из-за чего некоторые полагают, что компания отстаёт. «На 3 нм у Samsung высокая вероятность выйти на объёмное производство в 2021 году, — сказал Джонс. – TSMC ускоряет разработку, пытаясь угнаться за Samsung».

На 3 нм TSMC изучает нанослойные FET, нанопроводные FET и даже finFET. Один из способов расширения технологии finFET – использование в каналах материалов с высокой подвижностью, а именно германия. Сегодняшние finFET устройства используют кремний или кремний-германий (SiGe) в каналах. Увеличивая примесь германия, можно увеличить подвижность канала – то есть, скорость прохода электронов по устройству. И тут проблемой является контроль дефектов.

Расширение технологии finFET имеет смысл. finFET на 3 нм обеспечивает путь перехода от 5 нм. Однако тут есть свои проблемы. Теоретически технология finFET упирается в тупик, когда ширина плавника достигает 5 нм, что близко к текущему состоянию. «Сегодня мы используем по два плавника для NMOS и по три для PMOS в стандартной ячейке, — сказал Хоригучи из Imec. – Один из важных аспектов 3 нм в том, что нам нужно перейти на архитектуру с одним плавником для стандартных схем ячеек. Единственный плавник должен достаточно хорошо работать. Чтобы расширить технологию finFET до N3, нужна особая технология улучшения мощности единственного плавника и уменьшения фоновых паразитных явлений».

Кроме высокой мобильности finFET, следующий вариант – это GAA. В 2017 Samsung представила Multi Bridge Channel FET (MBCFET) для 3 нм. MBCFET – нанослойный FET. Пробная партия MBCFET от Samsung появится в 2020.

У нанослойных чипов есть преимущества перед finFET. У finFET затвор загибается вокруг плавника с трёх сторон. В нанослоях затвор находится с четырёх сторон плавника, что даёт больше контроля над током.

По сравнению с 5 нм, нанослойные FET от Samsung обеспечивают увеличение эффективности логической области до 45% и уменьшение энергопотребления на 50% или увеличение быстродействия на 35%. «У структуры finFET есть свои ограничения по масштабируемости, поскольку напряжение питания нельзя опускать ниже 0,75 В. Наша инновация с использованием нанослоёв позволяет уменьшить напряжение до значений менее 0,7 В», — сказал Ли из Samsung.

Технологий GAA бывает несколько видов, включая нанослойные FET и нанопроводные FET. Сам по себе GAA – следующий шаг после finFET. В этой системе finFET располагается на боку, а потом разделяется на горизонтальные кусочки. Кусочки формируют каналы. Материал затвора оборачивается вокруг каждого слоя.

По сравнению с нанопроводным FET, у такой схемы каналы шире, то есть, выше производительность и ток возбуждения. «У нанослоёв больше эффективная ширина, — сказал Хоригучи из Imec. – Нанопровода гораздо лучше справляются с электростатикой. Но их поперечное сечение очень мало. Это не даст преимуществ в вопросе эффективной ширины канала».

У архитектур GAA есть несколько проблем. Обычно они дают крайне небольшой прирост по сравнению с finFET на 5 нм. Производить чипы по этой технологии довольно тяжело.

«Следующее поколение GAA на 3 нм и ниже добавляет очередной порядок сложности в производство, — сказал Ричард Готшо, вице-президент и технический директор Lam Research [4]. – На первый взгляд, она выглядит, как модификация finFET. Однако требования усиливаются, и сложность этой архитектуры GAA значительно выше, чем у finFET».

В процессе производства нанослойных чипов первый шаг – размещение тонких чередующихся слоёв SiGe и кремния на подложке. «У нас получается стопка кремний, кремний-германий, кремний. Мы называем это сверхрешёткой», — сказал в недавнем интервью Намсун Ким, главный директор инженерного управления Applied Materials. «Имея германиевое содержимое, необходимо обеспечить ему хороший слой изоляции».

Как минимум, пачка должна состоять из трёх слоёв SiGe и трёх кремния. Затем на пачку наносятся крохотные листовые структуры. После этого формируется изоляция с канавками, а потом – внутренние разделители.

Затем слои SiGe удаляются из сверхрешётки, оставляя кремниевые слои с пустым пространством между ними. Каждый кремниевый слой формирует основание листа или канала в устройстве. Затем необходимо нанести материал с высокой диэлектрической проницаемостью для создания затвора. «Между нанопроводами минимальное расстояние. Очень маленькое. Проблема в том, чтобы поместить туда металл рабочей толщины», — сказал Ким.

Индустрия годами работала над созданием технологии GAA, однако всё ещё остаются определённые проблемы. «Одна из главных – паразитная ёмкость, — сказал Ким. – Если вы спросите меня, каковы главные проблемы технологии GAA, то их две. Внутренние разделители и изоляция подложки».

Что дальше?

Насколько хватит технологии GAA или нанослоёв? «Нанослои проживут два-три следующих техпроцесса. Мастерские могут изготовить нанослои на N3. Следующее поколение так уж точно. А после этого, возможно, придётся изменить интеграцию нанослоёв или архитектуру. Но это всё равно будет архитектура нанослоёв», — сказал Хоригучи из Imec.

Индустрия исследует способы улучшения технологий GAA и finFET на передовых техпроцессах. В данный момент устройства с GAA дают небольшое преимущество по сравнению с finFET. К примеру, у предыдущего нанослойного чипа от Imec шаг затвора составлял 42 нм, а минимальный шаг размещения металлических проводников – 21 нм. Для сравнения, у finFET на 5 нм может быть шаг затвора в 48 нм и минимальный шаг размещения металлических проводников в 28 нм.

В лаборатории Imec продемонстрировала масштабируемость устройства на полупроводниках p-типа с двойной стопкой GAA и германием в канале. Используя схему без расширений, Imec разработала нанопровод с длиной затвора порядка 25 нм. Его можно приспособить и для нанослоёв. Как и у предыдущей версии, размер проводов составляет 9 нм.

Германий может сыграть роль в продолжении использования finFET за пределами техпроцесса в 5 нм. Imec продемонстрировала Ge nFinFET с рекордно высокими показателями Gmsat/SSsat и PBTI. Они были достигнуты благодаря улучшению замены материала с высокой диэлектрической проницаемостью.

Мы ещё увидим, удастся ли расширить технологию finFET до 3 нм. Также непонятно, появятся ли нанослойные чипы вовремя. В этом меняющемся ландшафте множество неизвестных и неопределённостей, и не существует графика прояснения ситуации.

Автор: Вячеслав Голованов

Источник [5]

Сайт-источник PVSM.RU: https://www.pvsm.ru

Путь до страницы источника: https://www.pvsm.ru/samsung/325634

Ссылки в тексте:

[1] два единственных производителя: https://habr.com/ru/post/458280/

[2] эффектом короткого канала: https://www.kit-e.ru/articles/device/2009_12_157.php

[3] иммерсионную литографию: https://ru.wikipedia.org/wiki/%D0%98%D0%BC%D0%BC%D0%B5%D1%80%D1%81%D0%B8%D0%BE%D0%BD%D0%BD%D0%B0%D1%8F_%D0%BB%D0%B8%D1%82%D0%BE%D0%B3%D1%80%D0%B0%D1%84%D0%B8%D1%8F

[4] Lam Research: https://semiengineering.com/entities/lam-research/

[5] Источник: https://habr.com/ru/post/461875/?utm_source=habrahabr&utm_medium=rss&utm_campaign=461875

Нажмите здесь для печати.