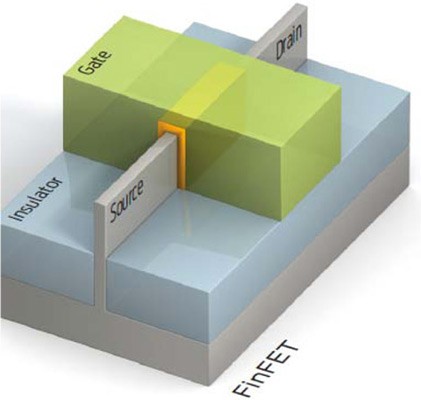

Samsung Electronics объявила, что достигла новой вехи в развитии 14-нанометрового тех. процесса для FinFET-полупроводников, успешно запустив «tape out» дизайна нескольких тестовых чипов. «Tape out» — это пакет цифровых данных (базы), на основе которого на заводе изготавливается фотошаблон для последующего литографического производства чипов. Раньше подобные проекты передавались на завод в виде бумажных распечаток, но затем были заменены на бобины с магнитной пленкой (tape). Само собой, в эпоху Интернета такими олд-скул средствами для передачи информации никто не пользуется, но термин прижился. В реальности же это означает, что проектная группа свою часть работы выполнила, и дело теперь за наладкой производства.

В рамках разработки 14-нм «вертикальных» FinFET-транзисторов компания Samsung совместно с партнерами по экосистеме: компанией ARM и разработчиками программных инструментов Cadence, Mentor и Synopsys, подготовили к выпуску несколько тестовых чипов, включая вычислительные ядра поколения ARM Cortex-A7 (в виде элементов архитектуры ARM big.little); чип со сверхнизким энергопотреблением и логическими элементами, основанными на базе SRAM и множество аналоговых блоков.

Тестовый чип процессора Cortex-A7 был разработан Cadence в сотрудничестве с ARM и Samsung. Компания Cadence предоставила полное описание работы синхронной цифровой схемы (RTL), опираясь на набор инструментов, требующий двойного формирования структур, который был тщательно протестирован на 20-нм тех. процессе. ARM, в свою очередь, использовали инструменты Cadence для разработки 14-нм библиотеки FinFET. Также эти инструменты были использованы для составления полного описания работы синхронной цифровой схемы ядра процессора на базе 14-нм тех. процесса FinFET от Samsung и прохождения этапов интеграции и верификации на уровне чипа.

Помимо этого, Samsung также расширяет сферу сотрудничества с компанией Mentor Graphics, с целью запуска законченного решения на базе 14-нанометрового FinFET, что избавит будущих клиентов от проблем в процессе разработки дизайна, тестирования, совместной оптимизации и пост-дизайна на этапе производства. Совместными усилиями компании планируют решить основные задачи, связанные с трудностями многослойной трехмерной литографии, особенностями FinFET-транзисторов и более комплексными требованиями к надежности указанных решений.

Набор средств, необходимый для процесса разработки новых чипов (PDK) доступен уже сегодня: клиенты могут начинать проектирование на основе тестовых моделей, руководства проектных норм и технологических гайдлайнов, которые уже были составлены и проверены в R&D лабораториях Samsung. Это PDK включает в себя проектирование потоков, маршрутизаторов и других возможностей для поддержки структур новых устройств, локальных соединений, а также расширенные правила маршрутизации. Предоставляя своим клиентам быстрый доступ ко всем элементам дизайна инфраструктуры новых чипов, Samsung, таким образом, инвестирует в разработку и скорейшую реализацию всей экосистемы FinFET.

Автор: flyant