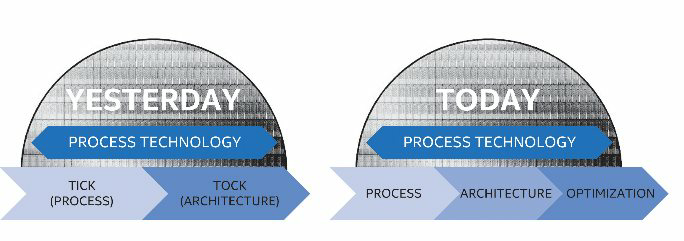

Теперь процессоры будут делать по циклу «процесс-архитектура-оптимизация»

Как публичная компания с более 10 млн $ в активах, акциями которой владеют более 500 акционеров, Intel предоставила Комиссии по ценным бумагам и биржам США ежегодный отчёт по форме 10-K. Особенный интерес в 150-страничном документе представляет страница 14, на которой Intel признаёт, что отказывается от стратегии «тик-так» в пользу новой концепции «процесс-архитектура-оптимизация».

Tick-Tock — модель развития микропроцессоров, которой Intel пользуется с 2007 года. В определённые промежутки времени технологии позволяют уменьшить размер элементов на плате, что позволяет снизить энергопотребление и уместить большее количество транзисторов на кристалле того же размера. Если можно уместить больше элементов, то возможна новая микроархитектура: добавляются новые команды, улучшается логика работы, увеличивается количество разных элементов.

Стратегия «тик-так» разделяет два процесса. За «тик» транзисторы становятся меньше. Изменения микроархитектуры есть, но они незначительны. «Так» означает создание новой микроархитектуры, то есть большие, иногда фундаментальные изменения в целях достижения больших приростов производительности.

Такими шажками Intel двигается уже почти 10 лет. Каждый из них занимает от года до полутора лет. Но в последнее время уменьшать техпроцесс становится всё сложнее. При переходе с 22 до 14 нанометров появились задержки в 6—9 месяцев. В это время приходилось повышать процент выхода работоспособных чипов с пластин до допустимого по себестоимости уровня. Закон Мура, который описывает удваивание количества транзисторов на кристалле каждые 24 месяца, приходится корректировать.

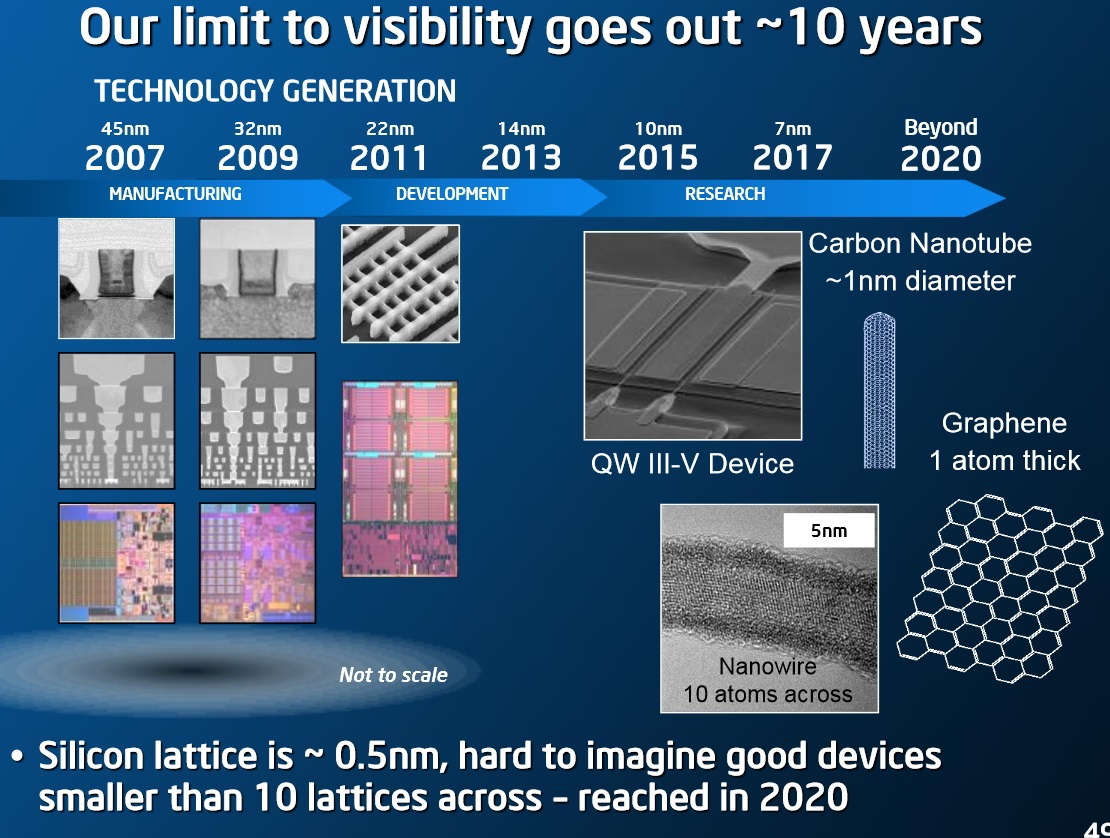

В дальнейшем планируется переход до 10, а затем и 7 и 5 нанометров. Достижение новых рубежей означает возможное использование литографии в глубоком ультрафиолете, Self-Aligned Quadruple Patterning (SAQP), отказ от кремния в пользу III-V полупроводников, карбоновых нанотрубок и графена.

Слайд из презентации год назад.

Документ для Комиссии по ценным бумагам и биржам затрагивает общий курс разработок Intel. Компания объясняет, что будет увеличено общее время использования продуктов на текущем техпроцессе в 14 нанометров и будущем в 10 нм. Но будет сохраняться рыночный темп выпуска новых продуктов. Как это будет достигнуто? Intel даёт изображение, которое в этом посте размещено до ката. В нём «тик-так» называется вчерашней технологией, а текущей реальностью объявлен цикл из трёх шагов «процесс-архитектура-оптимизация» (PAO).

14 нанометров помог отработать «тик» Broadwell, последователь 22-нм Haswell. Текущая микроархитектура Intel — это Skylake, шестое поколение Core, «так» 14-нанометрового техпроцесса. Его последователь, Kaby Lake, тоже будет 14-нанометровым, но будет предоставлять «значительные улучшения производительности по сравнению с семейством процессоров шестого поколения Core».

Достичь 10 нанометров может помочь упоминаемое в документе сотрудничество с ASML по исследованию фотолитографии в глубоком ультрафиолете, в том числе применимой к пластинам диаметров в 300 и 450 миллиметров. Intel пока что сохраняет лидерство: 14 нм были представлены в августе 2014 года, Samsung и TSMC подтянулись позже.

Ожидается, что 14-нанометровый Kaby Lake будет выпущен в этом году. Согласно текущим планам, продукты на 10-нанометровой микроархитектуре Cannonlake должны появиться в 2017 году. В трёхступенчатом цикле легко увидеть очевидные плюсы для конечного пользователя: одна и та же материнская плата может подойти для продуктов двух или более поколений.

Автор: atomlib