Компания Toshiba Electronics Europe (TEE) объявила о доступности для европейских заказчиков технологии Structured Array. Эта технология позволяет использовать специализированные микросхемы (ASIC) в качестве альтернативы программируемым пользователем вентильным матрицам (FPGA). При этом обеспечивается свойственный ASIC выигрыш в стоимости и энергопотреблении, но затраты времени на получение конечного изделия существенно меньше, чем в случае с обычными ASIC.

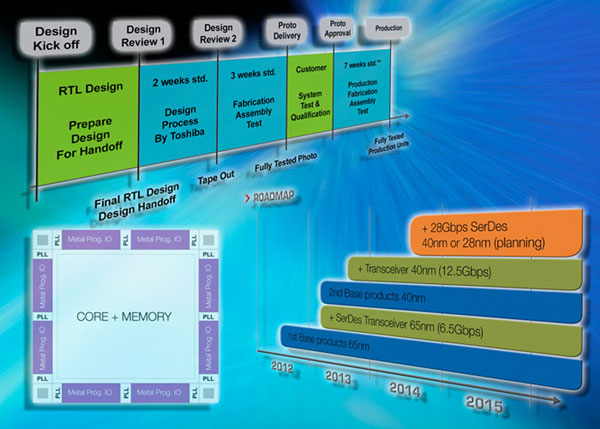

В основе Structured Array лежит технология, лицензированная у BaySand. Секрет ускорения разработки кроется в использовании чипов с заранее сформированными блоками, которые конфигурируются минимальными усилиями с помощью заказных масок для слоев металлизации. В частности, среди блоков есть оптимизированные массивы вентилей и память. Сокращение до минимума числа слоев металлизации, которые необходимо разработать для получения специализированной микросхемы, по словам производителя, позволило сократить время получения инженерных образцов до пяти недель.

Как утверждается, однокристальные системы, построенные на базе «структурированных» ASIC, стоят дешевле, чем FPGA, имеют меньшее энергопотребление и могут быть рассчитаны на более высокие частоты. В то же время, при их разработке можно использовать данные, накопленные при проектировании FPGA. Обеспечивается совместимость с FPGA на уровне архитектуры памяти и средств ввода-вывода, а также на уровне корпусов и выводов, что позволяет использовать новые ASIC в качестве прямой замены FPGA.

Сейчас TEE предлагает решения, рассчитанные на выпуск по 65-нанометровой технологии, включающие до 30 млн. вентилей, 20 Мбит SRAM и до 1200 линий ввода-вывода. Заказчики могут интегрировать интерфейсы LVDS и DDR. Приемопередатчики с пропускной способностью до 6,5 Гбит/с находятся в процессе разработки. Кроме того, производитель планирует разработку приемопередатчиков с пропускной способностью до 12,5 Гбит/с и освоение норм 40 нм.

Источник: TEE