* ПНЯ — Периферия Независимая от Ядра в микроконтроллерах Microchip, известная так же как CIP — Core Independent Peripheral.

Часть 4

Предыдущие статьи [1], [2] и [3] были посвящены Периферии Независимой от Ядра (ПНЯ) микроконтроллеров Microchip: конфигурируемым логическим ячейкам, портам ввода/вывода с функцией ограничения тока и АЦП с вычислителем, были показаны некоторые возможности такой периферии. Напомню, что независимость подразумевается не от типа ядра PIC микроконтроллеров (BaseLine, Mid-Range, Enhanced Mid-Range, PIC18, 16-, 32-bit), а от работы ядра, т.е. независимое выполнение возложенной на периферию задач от состояния ЦПУ. Такая периферия, а в особенности возможность её конфигурирования на совместную работу и синтез аппаратных функций, призвана разгрузить программную часть, снизить энергопотребление.

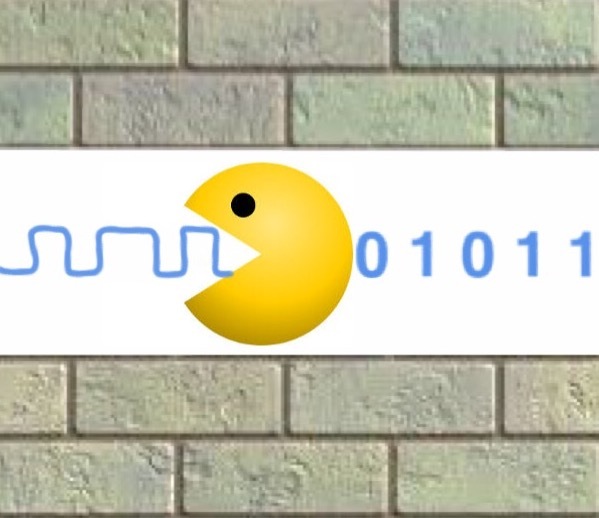

В этой небольшой статье хочу показать примеры реализации приема «кастомных», нестандартных интерфейсов связи с помощью Периферии Независимой от Ядра.

Читать полностью »