Всех приветствую.

По следам предыдущих статей по логическим анализаторам на Хабре решил таки закончить свой "фундаментальный" труд.

Начну немного издалека.

Все началось в в начале 10-х годов, когда я впервые узнал про Saleae Logic (далее под Saleae я подразумеваю 8 канальный анализатор без плисины) на каком-то радиолюбительском форуме.

Принял к сведению. Но уже в 13 в процессе реализации очередного проекта столкнулся с тем, что очень мне понадобился логический анализатор с большим буфером. Доступные в тот момент осциллограф и hanteck la-5034 не позволяли решить проблему.

Главная особенность Saleae и его клонов это отсутствие встроенного буфера — весь поток сразу гонится в ПК и там сохраняется. После чего его можно анализировать, декодировать и экспортировать. С одной стороны мы практически не ограничены в глубине просмотра (можно часами сохраняться данные), с другой стороны максимальная частота семплирования 24МГц. В большинстве случаев хватает, правда из-за программного характера семплирования, у отсчетов есть заметный "джиттер".

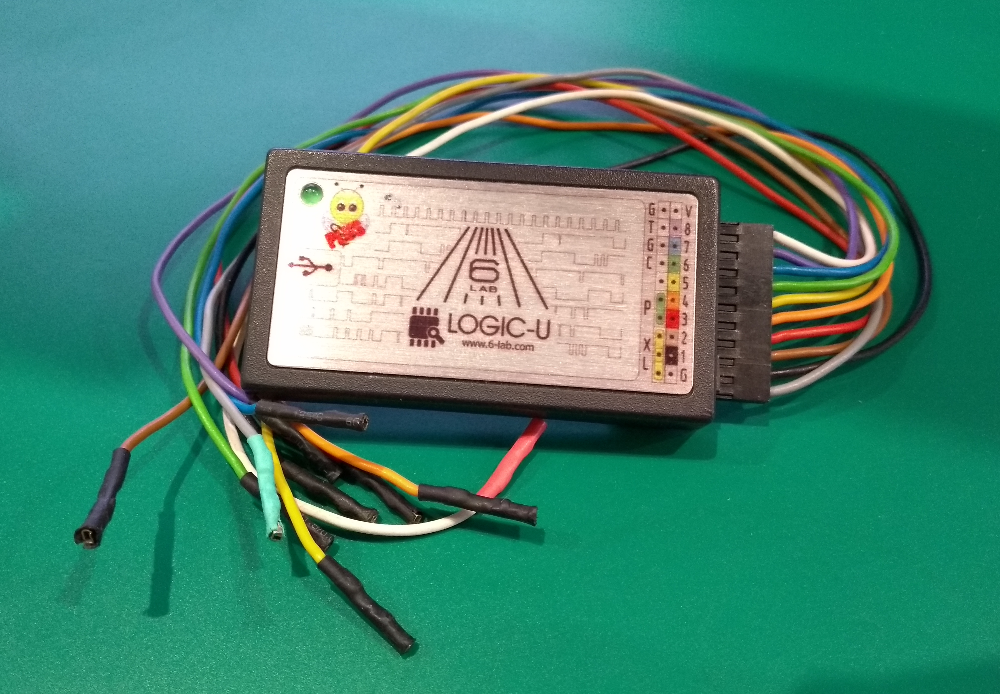

В итоге, очень быстро, примерно за сутки, из Харькова, из 6-lab (ныне почившей) мне через проводников доставили их клон saleae с уже встроенными двумя eeprom для переключения типов saleae и xbee (аппаратная часть у этих устройств одинаковая отличаются только vid:pid которые прошиты в eeprom).

Соответственно можно пользоваться ПО от обоих производителей.

Вот тогда я и заинтересовался такой штукой как СY7C68013A, ну или короче FX2 (хотя правильней FX2LP).

Это 8051-совместимый микроконтроллер с аппаратным USB2.0 портом и честными 480Мб/с.

В число особенностей входит: 16KB оперативной памяти и возможность загрузить прошивку как из подключенной I2C EEPROM, так и через USB (встроенной flash там нет).

А еще этот МК может прикидываться любым устройством на USB-шине (в смысле откликаться на любой VID:PID).

Немного подробностей из даташита по процедуре загрузки

Рассмотрим случай когда к МК подключена I2C EEPROM.

В таком случае из нее анализируются 8 первых байт:

| EEPROM Address | Contents |

|---|---|

| 0 | 0xC0 |

| 1 | Vendor ID (VID) L |

| 2 | Vendor ID (VID) H |

| 3 | Product ID (PID) L |

| 4 | Product ID (PID) H |

| 5 | Device ID(DID) L |

| 6 | Device ID(DID) H |

| 7 | Configuration Byte |

Если первый байт 0xC0 (как в прошивке клонов Saleae), то МК конфигурирует USB-порт с указанными в 1-4 байтах VID:PID и ждет загрузки прошивки через USB. В зависимости от прошитых VID:PID МК может "быть" разным устройством, хоть Saleae хоть Xbee хоть кем. Очень удобно. Можно стопкой припаять EEPROM-ки и джампером выбирать.

А вот если первый байт 0xC2, то начиная с 9 байта в EEPROM должна хранится прошивка для MK, которую он загрузит в RAM и начнет исполнять.

Формат хранения похож на HEX от Intel:

| 8 | Length H |

| 9 | Length L |

| 10 | Start Address H |

| 11 | Start Address L |

| – | Data Block |

| – | Length H |

| – | Length L |

| – | Start Address H |

| – | Start Address L |

| – | Data Block |

| – | 0x80 |

| – | 0x01 |

| – | 0XE6 |

| – | 0x00 |

| Last | 00000000 |

То есть, прошивка разбивается на блоки которые по отдельности грузятся в разные участки памяти. И соответственно, нет смысла хранить пустые участки.

И вот мы плавно подходим к главному герою нашей статьи DreamSourseLab.

Не буду пересказывать всю историю (я ее толком не знаю и глубоко погружаться смысла не вижу). Это три инженера которые через краудфандинг запилили проект логического анализатора мечты (ну почти).

Что они сделали.

Добавили к FX2 дешевую плисину — Spartan 6 (возможно подсмотрели у Saleae).

А это сразу 16 каналов, это четкие моменты семплирования, это возможность упаковки отдельных бит (две линии можно семплировать в 4 раза чаще чем 8, главное в полосу пропускания USB уложиться). Это возможность сохранять в буфер на высокой частоте (400МГц/4 канала, 200МГц/8 каналов, 100МГц/16каналов), а потом медленно отдавать в ПК. А если к этому прикрутить sigrok с его мощнейшей базой декодируемых протоколов. В общем, проект выстрелил — все довольны. А с учетом того, что авторы сохранили поточный режим (без сохранения во внутренний буфер), то получился логический анализатор мечты (ну почти, потому как сразу захотелось 32 канала и FX3).

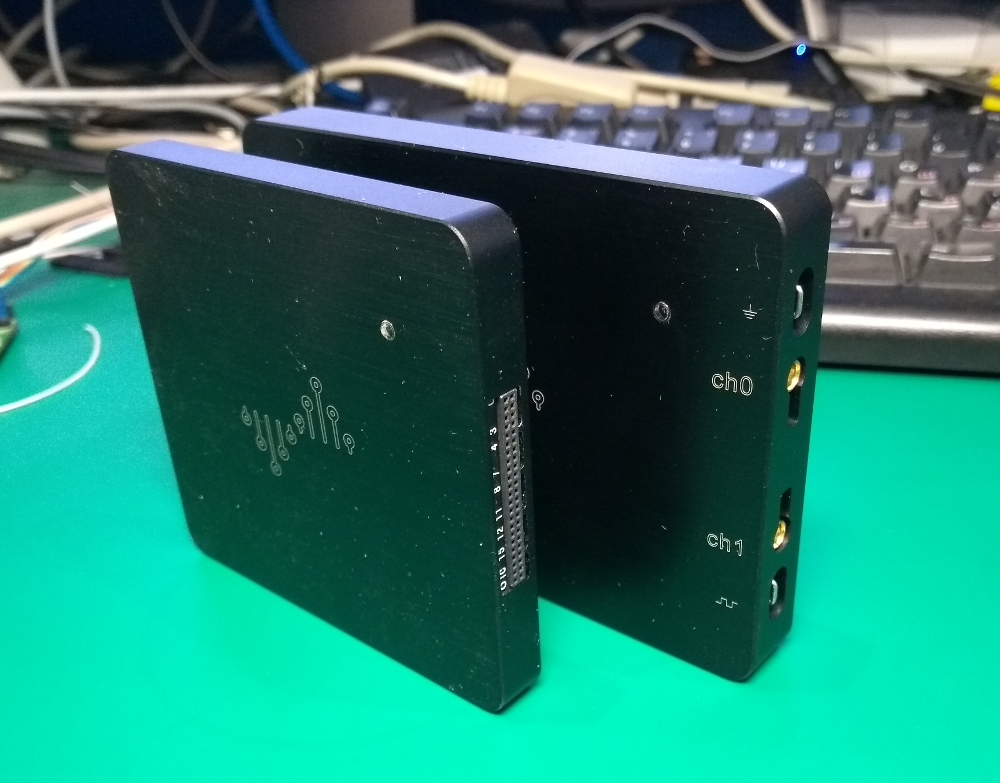

Таким образом появился DSLogicPro. Строгая черная коробочка из алюминия с USB-C разъемом.

А дальше инженеры ударились в бизнес. И выпустили коробочки с названием DSLogicBase и DSLogicPlus (как я понял для завоевания мира через китайские сайты), а также DSCope (вешаем парочку 8-разрядных AЦП и вот у нас получился двухканальный осциллограф).

Ну, а чтобы этот процесс шел под строгим контролем немного поменяли разводку плат. То есть электрически и функционально DSLogicPlus и DSLogicPro идентичны, но SRAM висит на плисине на других выводах (это хорошо видно по рисунку дорожек). Подозреваю, что и в других местах сделаны доработки.

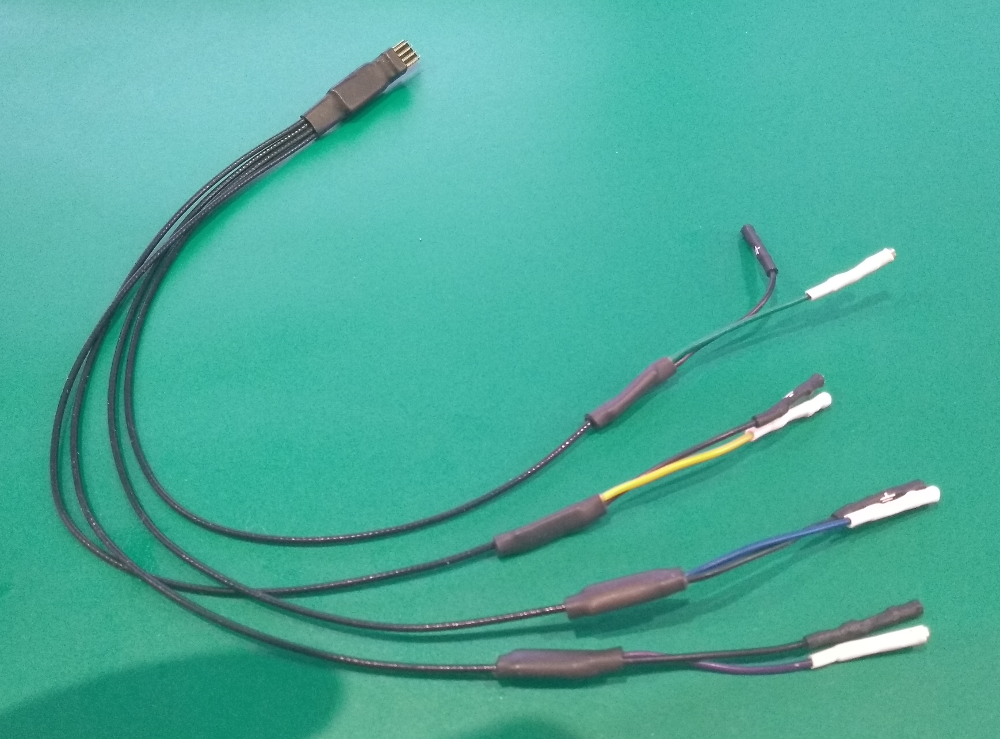

Кстати, была сделана очень ценная доработка в плане кабеля подключения исследуемых сигналов. Если в Pro все 16 линий подключаются сразу одним широким разъемом, то в Plus, все кабели разделили на группы по 4 канала который можно подключать отдельно. Ну и сами кабели короткие, коаксиальные и в месте разделки (где коаксиал раздваивается на отдельный сигнальный и общий проводы) стоит маленькая платка с фильтром.

И вот, весной 17 года я в Китае заказал себе DSLogicBase (к сожалению я тогда не знал всего-того о чем тут написал). Мне все прислали, но предвкушая буфер на 64 мегасемпла я раскрутил плату и увидел пустое место. Быстро подняв бучу вернул 50% стоимости. А потом занялся изучением вопроса по превращению моего Base в Plus. Именно в этом и заключается отличие Base от Plus — наличием отдельного буфера. В Base используется память встроенная в FPGA.

Летом 17 года по дороге на работу и обратно по полчаса в электричке МЦК я изучал этот вопрос. И довольно быстро стало ясно, что отличия только в запаянной SRAM и паре байт прошивки EEPROM.

Немного про то, что лежит в каталоге DSView/res

Там у нас комплект файлов с раcширениями bin и fw.

bin — это прошивки для плисины. Они загружаются в момент старта программы через fx2.

fw — это бинарные файлы прошивки для FX2.

Если сравнить все файлы fw от окажется, что все они отличаются только байтом PID-а по адресу ближе к концу.

То есть отличия у всех устройств только этим ну и прошивкой плисины (которая как я уже сказал грузится в момент инициализации).

Сравнение fw с тем, что записано в EEPROM (я конечно сразу слил дамп с своего анализатора) показало, что здесь именно развернутая прошивка.

Если прошивку из EEPROM развернуть, то (насколько я помню) они совпадут (для версии ПО 0.96).

Таким образом, как уже писали на хабре, нужно всего лишь припаять память и в прошивке поменять 2 байта (в заголовке и потом далее в прошивке).

Аналогичным образом дорабатывается DSCope, допаиваем память и меняем PID в EEPROM.

Есть еще один нюанс.

По мере выпуска новых версий ПО (0.96-0.99) происходило добавление поддерживаемых моделей оборудования и изменение PID этих моделей.

Вот у меня получилась такая табличка:

| FW | Size buf | 0.96 | 0.97 | 0.98 | 0.99 | 0.98: 0x20 | 0.99: 0x20 |

|---|---|---|---|---|---|---|---|

| DSLogic | 256MB | 01 | 01 | 01 | 01 | ||

| DSLogicPro | 256MB | 1002 | 03 | 03 | 03 | 5 | 5 |

| DSMso | 05 | 05 | 05 | - | |||

| DSLogicBasic | 256KB | 21 | 21 | 21 | 21 | 6 | 6 |

| DSLogicPlus | 256MB | 20 | 20 | 20 | 20 | 6 | 6 |

| DSCope | 256MB | 02 | 02 | 02 | 02 | ||

| DSCope20 | 256MB | 04 | 04 | 04 | 04 | ||

| DSCope B20 | 256MB | — | — | 22 | 22 | ||

| DSCope C20 | 256MB | — | — | — | 23 | ||

| DSCope C20B | 256MB | — | — | — | 24 | ||

| DSCope C20P | 256KB | — | — | — | 25 |

Кроме этого, в прошивках появился какой-то признак по адресу 0x20 у версии Pro там 5, у Base и Plus там 6. Скорей всего это как раз версия печатной платы.

Кстати, есть еще один способ доработки. Не требующий перепрограммирования EEPROM. Достаточно только запаять SRAM, а потом при компилировании libsigrok4DSL в файл libsigrok4DSL/hardware/DSL/dsl.h внести исправление:

В структуре описывающей оборудование static const struct DSL_profile supported_DSLogic[],

в месте где описывается DSLogic PLus и Base поля PID поменять местами, чтобы программы думала, что у Base PID 20, а у Plus PID 21.

319 {0x2A0E, 0x0020, "DreamSourceLab", "DSLogic PLus", NULL,

320 "DSLogicPlus.fw",

321 "DSLogicPlus.bin",

322 "DSLogicPlus.bin",

323 {CAPS_MODE_LOGIC,

324 CAPS_FEATURE_VTH | CAPS_FEATURE_BUF,

325 (1 << DSL_STREAM20x16) | (1 << DSL_STREAM25x12) | (1 << DSL_STREAM50x6) | (1 << DSL_STREAM100x3) |

326 (1 << DSL_BUFFER100x16) | (1 << DSL_BUFFER200x8) | (1 << DSL_BUFFER400x4),

327 SR_MB(256),

328 0,

329 DSL_BUFFER100x16,

330 0,

331 0,

332 DSL_STREAM20x16,

333 SR_MHZ(1),

334 SR_Mn(1),

335 0,

336 0}

337 },

338

339 {0x2A0E, 0x0021, "DreamSourceLab", "DSLogic Basic", NULL,

340 "DSLogicBasic.fw",

341 "DSLogicBasic.bin",

342 "DSLogicBasic.bin",

343 {CAPS_MODE_LOGIC,

344 CAPS_FEATURE_VTH,

345 (1 << DSL_STREAM20x16) | (1 << DSL_STREAM25x12) | (1 << DSL_STREAM50x6) | (1 << DSL_STREAM100x3) |

346 (1 << DSL_BUFFER100x16) | (1 << DSL_BUFFER200x8) | (1 << DSL_BUFFER400x4),

347 SR_KB(256),

348 0,

349 DSL_STREAM20x16,

350 0,

351 0,

352 DSL_STREAM20x16,

353 SR_MHZ(1),

354 SR_Mn(1),

355 0,

356 0}

357 },И ваша версия анализатора с этой версией DSView будет работать как будто у вас настоящий Plus.

А я пока помечтаю о связке Spartan6+FX3+DSView.

Автор: andi123