На прошлой неделе было объявлено о приобретении Intel компании eASIC, которая занимается созданием FPGA-образных средств разработки «структурных ASIC». Структурные ASIC представляют собой нечто среднее между обычными FPGA и обычными ASIC; они позволяют уменьшить время вывода продукта на рынок и уменьшить его стоимость. Технологии eASIC используются Intel с 2015 года в кастомных версиях процессоров Xeon; теперь команда eASIC (120 человек) войдет в подразделение Intel Programmable Solutions Group (PSG).

Даже те, кто давно и взаимно «внес в друзья» FPGA и ASIC, не откажутся от пояснений, что же такое «структурные ASIC». Вычислительные мощности компьютера не ограничиваются CPU или GPU, существуют и другие классы процессоров, такие, например, как FPGA — их разработкой занимается приобретенная Intel компания Altera. В FPGA миллионы логических элементов могут быть гибко запрограммированы так, чтобы реализовать необходимый функционал. На деле большинство CPU и GPU изначально симулируются на FPGA для проверки работоспособности. FPGA — это простой путь для моделирования взаимодействующих цепей, и область их применения широка. FPGA также могут содержать готовые аппаратные блоки, например, ARM ядра или трансиверы для внешних коммуникаций.

Еще один пример — ASIC (Application Specific Integrated Circuit), чип, созданный для выполнения строго определенного ряда задач. ASIC максимально оптимизирован под свои задачи, и логика его работы не может быть изменена. Часто CPU и GPU относят к классу ASIC в том смысле, что их микроархитектура тоже фиксирована, но они предназначены для решения разнообразных задач и универсальны, в то время как ASIC создается для четко определенных видов вычислений. Особенности ASIC: они быстры, экономичны, но относительно дороги и сложны в изготовлении.

«Структурные ASIC» компании eASIC можно назвать половинчатым решением. Инженеры создают прототип с использованием FPGA, но не тратят время на оптимизацию его схемотехники, а изготовляют на его основе чип с фиксированной архитектурой. Благодаря этому он работает быстрее, чем образец с настраиваемыми блоками, хотя и лишается преимущества энергоэффективности. Однако время на его разработку сравнимо с FPGA, а не ASIC — экономится до 6 месяцев. Вклад eASIC состоит в том, что используется однотрафаретная оптимизация слоя для замены SRAM-маршрутизации на сквозную, что существенно уменьшает стоимость производства. eASIC также предоставляет фиксированные библиотеки для ячеек, также однослойные, что еще больше уменьшает потребление, размер кристалла и срок выхода на рынок. Также дизайнеры могут пропустить стандартные при создании ASIC процедуры, такие как балансировка синхронизации, анализ целостности сигналов, тест ослабления питания и другие. Таким образом, «структурные ASIC» можно охарактеризовать как FPGA, которые далее нельзя программировать, обладающие лучшими качествами как FPGA, так и ASIC.

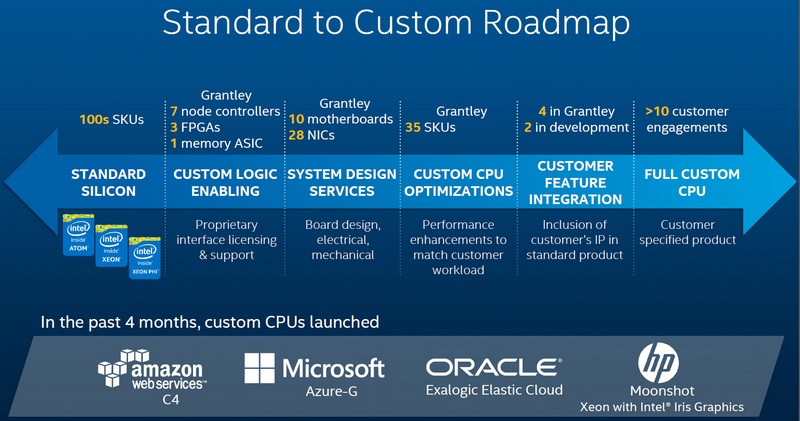

График показывает текущее состояние дел и перспективы в области кастомных процессоров Intel Xeon

Технологии eASIC нужны Intel для интеграции программируемой логики в процессоры Xeon для улучшения производительности, энергопотребления и цены. Наряду со стандартными Xeon, Intel уже сейчас выпускает кастомные варианты для своих крупнейших клиентов. Как мы видим из схемы, глубина кастомизации будет увеличиваться. С приобретением eASIC данный процесс ускорится и расширится. Думается, что подход «CPU как ASIC» может принести нам много интересного.

Автор: saul