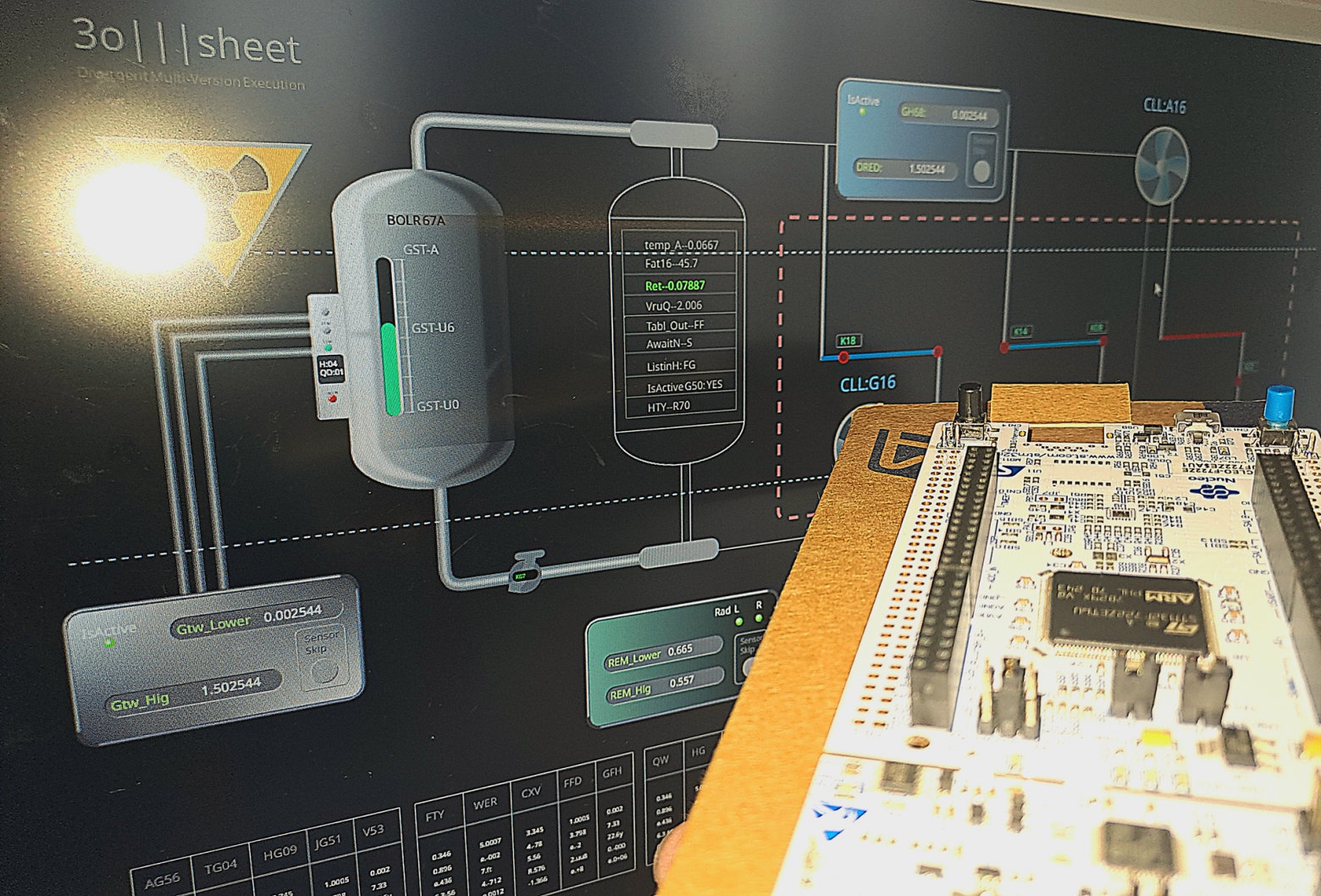

В этой статье я хочу рассказать о том, как я запускал собственную базовую станцию мобильной связи (4G и 2G) при помощи относительно дешевого SDR‑трансивера.

Введение

Тема создания собственной базовой станции поднималась на Хабре не раз. В первую очередь, стоит отметить отличные статьи @MaFrance351: