Автор: Cyberflex (по мотивам реальной разработки "MixFighter")

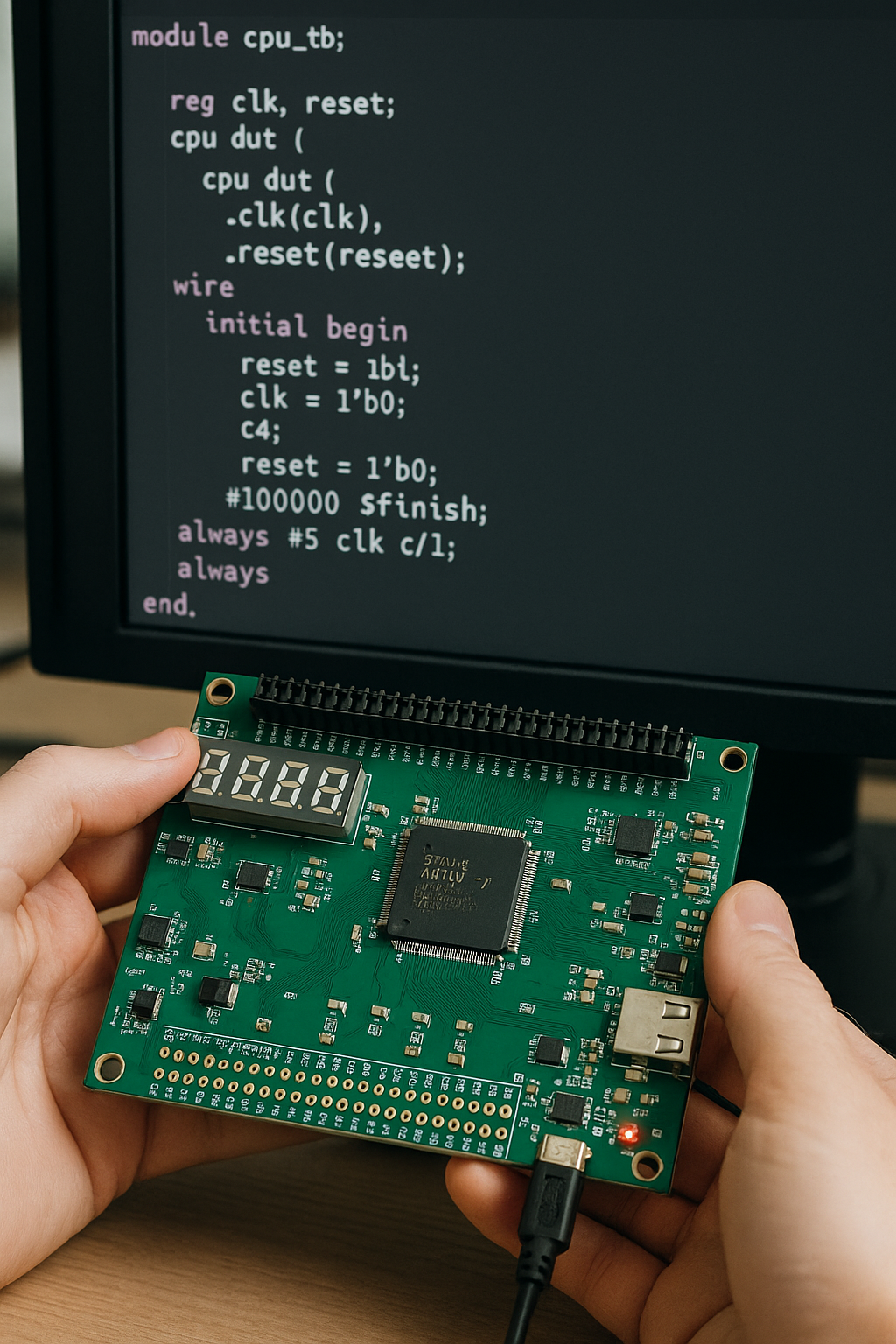

Как мы сделали мост между Icarus Verilog и NGSpice: две разных реализации архитектуры, их недостатки и почему идеальное решения пока не достигнуто

Что такое событийная и непрерывная симуляция?

В мире симуляции электронных систем существуют два принципиально разных подхода.

Событийная симуляция (event‑driven)Читать полностью »