Рубрика «xilinx»

Образовательные технологии опробованные в России — работают и в США

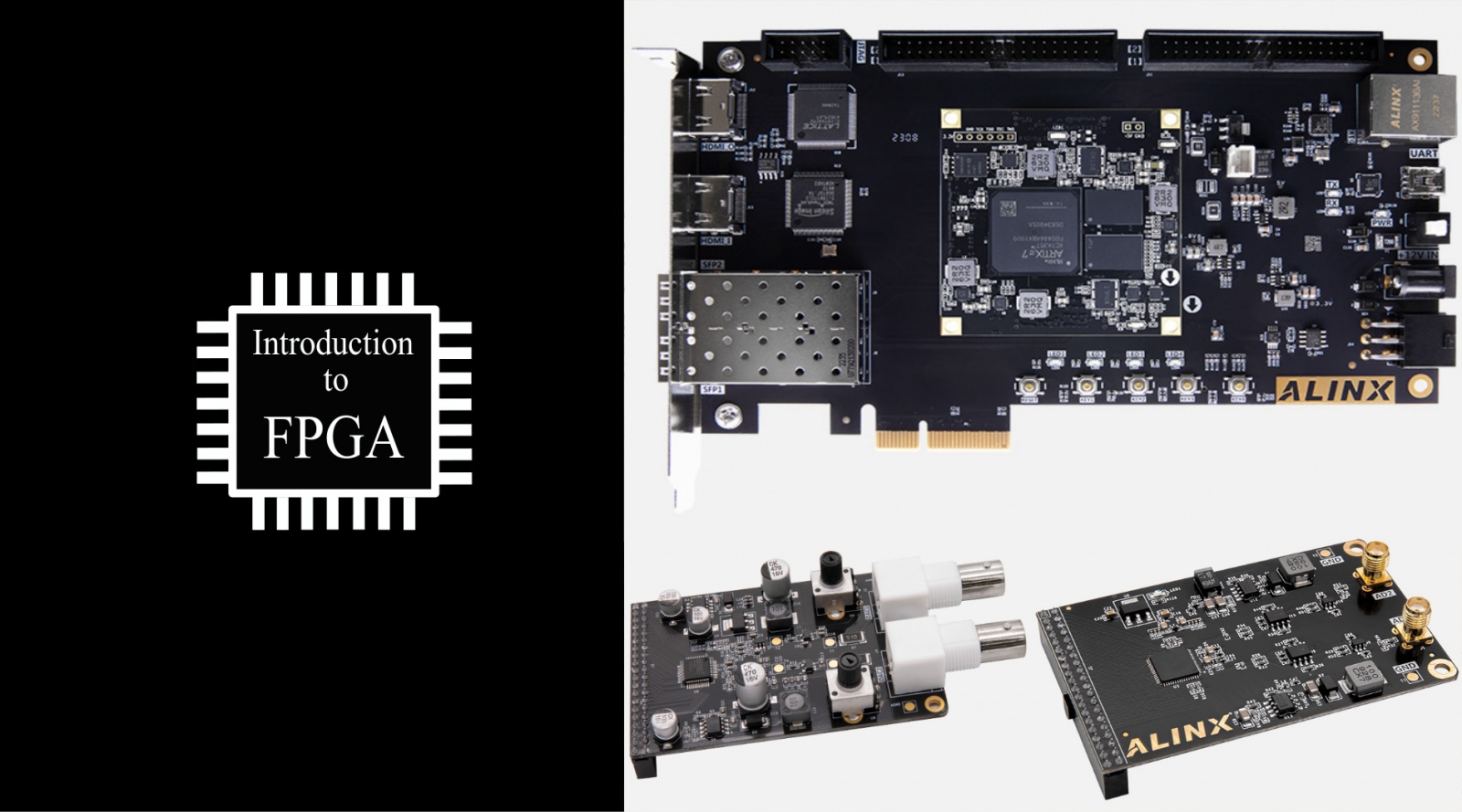

2025-10-29 в 16:01, admin, рубрики: Altera, asic, Cal Poly, fpga, Gowin, SystemVerilog, TinyTapeout, Verilog, vlsi, xilinxВведение в ПЛИС: Материальное обеспечение курса

2024-11-06 в 6:15, admin, рубрики: Alinx, AntMiner, fpga, xilinx, ПЛИСВ рамках подготовки курса "Введение в ПЛИС" были отобраны несколько относительно недорогих, но функционально разносторонних плат. Здесь я бы хотел рассмотреть возможности, которые они дают в плане обучения студентов.

Отладочная плата с жирной ПЛИС за 500р или что делать со старым антмайнером — как я делаю собственную платформу

2024-09-13 в 0:26, admin, рубрики: DIY devboard, FPGA+SoC, xilinx, дешевая отладочная плата, одноплатникС незапамятных времён, когда ещё существовали браузеры под ДОС, я взял себе ник Astra.

Первое занятие Школы Синтеза и удар в спину от Ubuntu

2023-09-25 в 4:24, admin, рубрики: bash, fpga, Gowin, Intel FPGA, linux, SystemVerilog, Ubuntu, xilinx, Школа Синтеза

В субботу прошло первое занятие Школы Синтеза Цифровых СхемЧитать полностью »

Made at Intel. Acquisitions -3

2023-03-19 в 11:39, admin, рубрики: Altera, amd, intel, mcafee, xilinx, Читальный залСегодня у нас на очереди третья заключительная часть повествования о приобретениях Интел. (начало – здесь и здесь). Я сразу оговаривался о том, что вряд ли смогу осветить всю M&A активность, поэтому сфокусируюсь на наиболее знаковых и памятных событиях за 22 года моей работы в компании. Начнем,пожалуй, с Альтеры.

Altera

Zynq 7000. Плата Zynq Mini c XC7Z020

2023-03-08 в 15:04, admin, рубрики: Development Tools, fpga, xilinx, zynq, zynq-7000Как прошла ПЛИСовая конференция в Питере?

2022-01-17 в 15:49, admin, рубрики: Altera, community, developers, fpga, Intel FPGA, xilinx, высокая производительность, конференции, ПЛИС, Производство и разработка электроникиПрошло всё отлично, 35 человек собралось, 7 докладов выслушано, 12 человек осталось на афтерпати.

Следующее мероприятие пройдет в Москве, Минске, Томске и Санкт-Петербурге в апреле-мае, подробности тут.

Все материалы собраны в отдельные плейлисты - встреча в Москве // слёт в Санкт-Петербурге, под каждым из видео ссылка на презентацию докладчика.

Как разработать микросхему, от идеи до результата. Часть 2. Установка программного обеспечения

2021-12-08 в 9:00, admin, рубрики: Altera, arduino, avr, c++, fpga, ic design, intel, IoT, mips, MIPSfpga, ruvds_статьи, stm32, SystemVerilog, Verilog, vhdl, vlsi design, xilinx, Блог компании RUVDS.com, микроконтроллеры, микросхемы, ПЛИС, программирование микроконтроллеров, Производство и разработка электроникиНапоминаю, что я продолжаю идти к цели — сделать свой собственный Отечественный Процессор (TM). Продолжение процесса разработки можно посмотреть под катом.

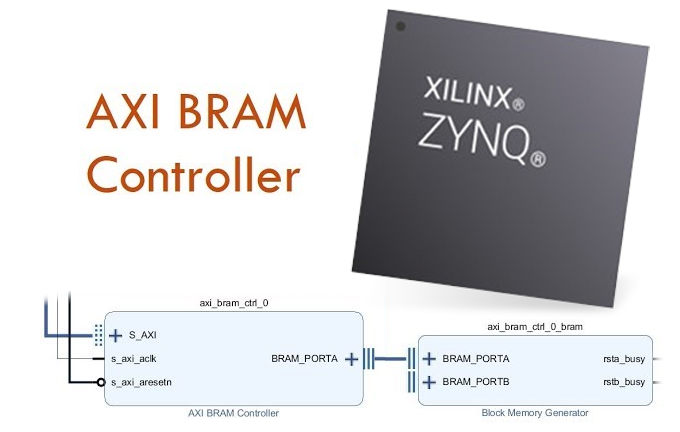

Zynq 7000. Обмен информацией между PS и PL

2021-08-15 в 20:28, admin, рубрики: AXI, bram, diy или сделай сам, fpga, howto, linux, qmtech, SDK, vivado, xilinx, zynq, Процессоры, Электроника для начинающихПродолжаю повествование о том, как проходит мое изучение возможностей отладочной платы с SoC Zynq 7000 на базе отладочной платы QMTech. В этой статье я опишу то, как я решал задачу примитивного обмена данными между PS и PL с использованием baremetal application и при использовании Linux. Всем интересующимся добро пожаловать под кат!