В 2010 году я участвовал в интервьировании на позицию по моделированию и верификации процессорных ядер. Один из кандидатов был благообразный седой американец, который до этого работал в IBM.

В 2010 году я участвовал в интервьировании на позицию по моделированию и верификации процессорных ядер. Один из кандидатов был благообразный седой американец, который до этого работал в IBM.

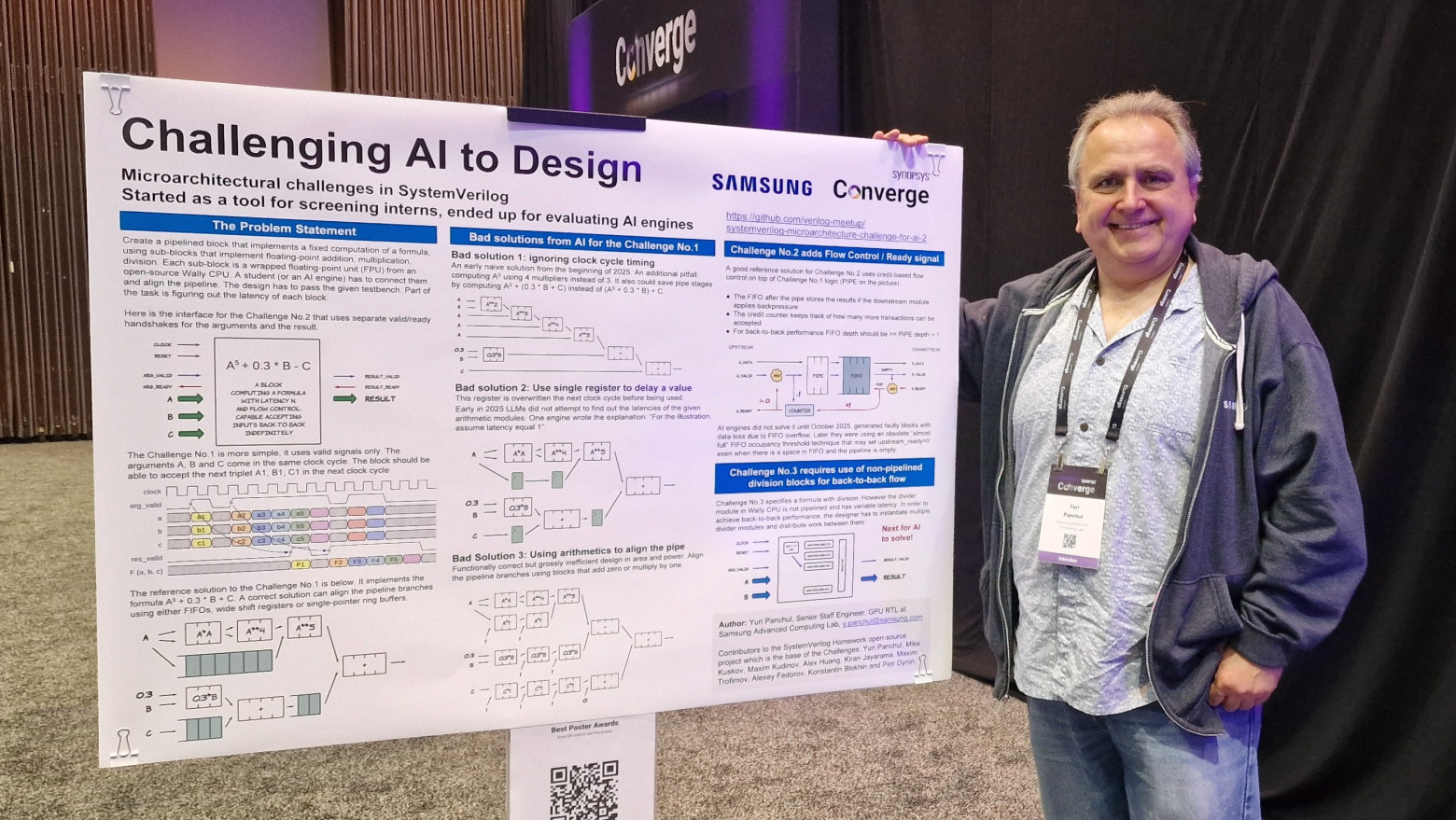

AI - не микроархитектор, не проектировщик и не верификатор. Это все-лишь гламурный поисковик уже решенных и опубликованных задач. Именно такой вывод следовал из предоставленных мною на конференции SNUG Silicon Valley 2026 Читать полностью »

Сдвиговый регистр – это одна из наиболее часто применяемых конструкций в проектах на ПЛИС. Сегодня мы уделим внимание тому, как можно и нужно писать VHDL и Verilog код для сдвиговых регистров, но при этом, чтобы синтезатор понял, что мы хотим реализовать сдвиговый регистр из нескольких триггеров или же задействовать для его реализации специальные ресурсы, такие как SRL регистры.

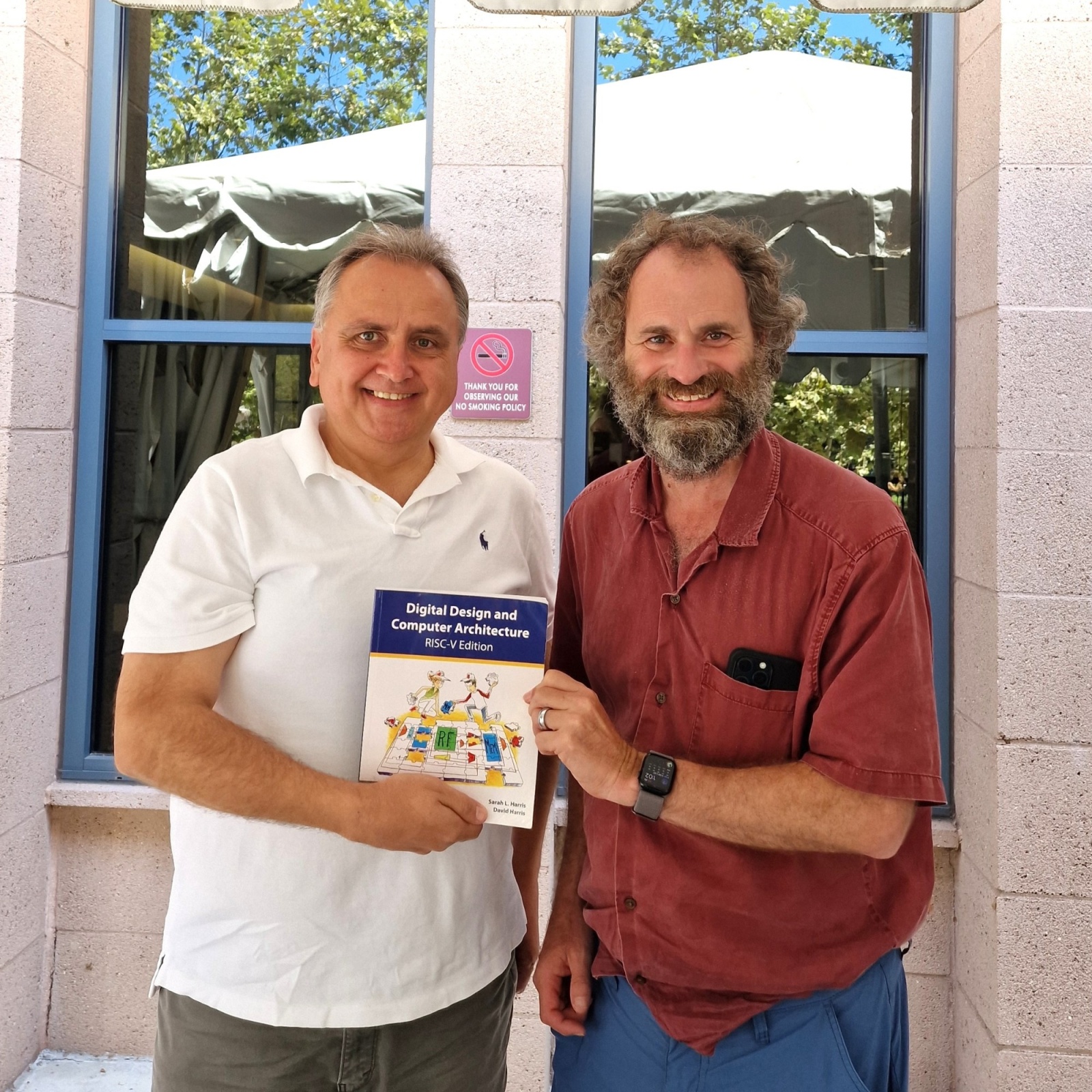

Встретился на ланч с Дэвидом Харрисом, автором (вместе с Сарой Харрис) популярного учебника Читать полностью »

Детей недостаточно учить только питону и ардуине. Нужно еще и цифровой схемотехнике, причем не на симуляторе, так как он для ребенка неубедителен, а на микросхемах малой степени интеграции, лучше которых для иллюстрации функции D-триггера никто с 1968 года ничего не придумал.

ПЛИС-культ привет, FPGA хабрунити.

На днях состоялся анонс уже второго номера народного FPGA журнала

FPGA-Systems Magazine :: № BETA (state_1). В нем 200+ страниц и 20+ статей и небольших заметок по направлениям FPGA / RTL / Verification (ПЛИС сегодня это не только про знание HDL и Vivado c Quartus'ом). Журнал бесплатный и распространяется в виде pdf-ки.

Зачем? Есть же хабр!

Внутри каждого современного телефона несколько микросхем ASIС. Ими наполнены автомобили, стойки в центрах обработки данных, датчики «умного дома», и вообще все электронные устройства. Без чипов ASIC был бы невозможен быстрый интернет, трехмерные игры и ускорители машинного обучения.