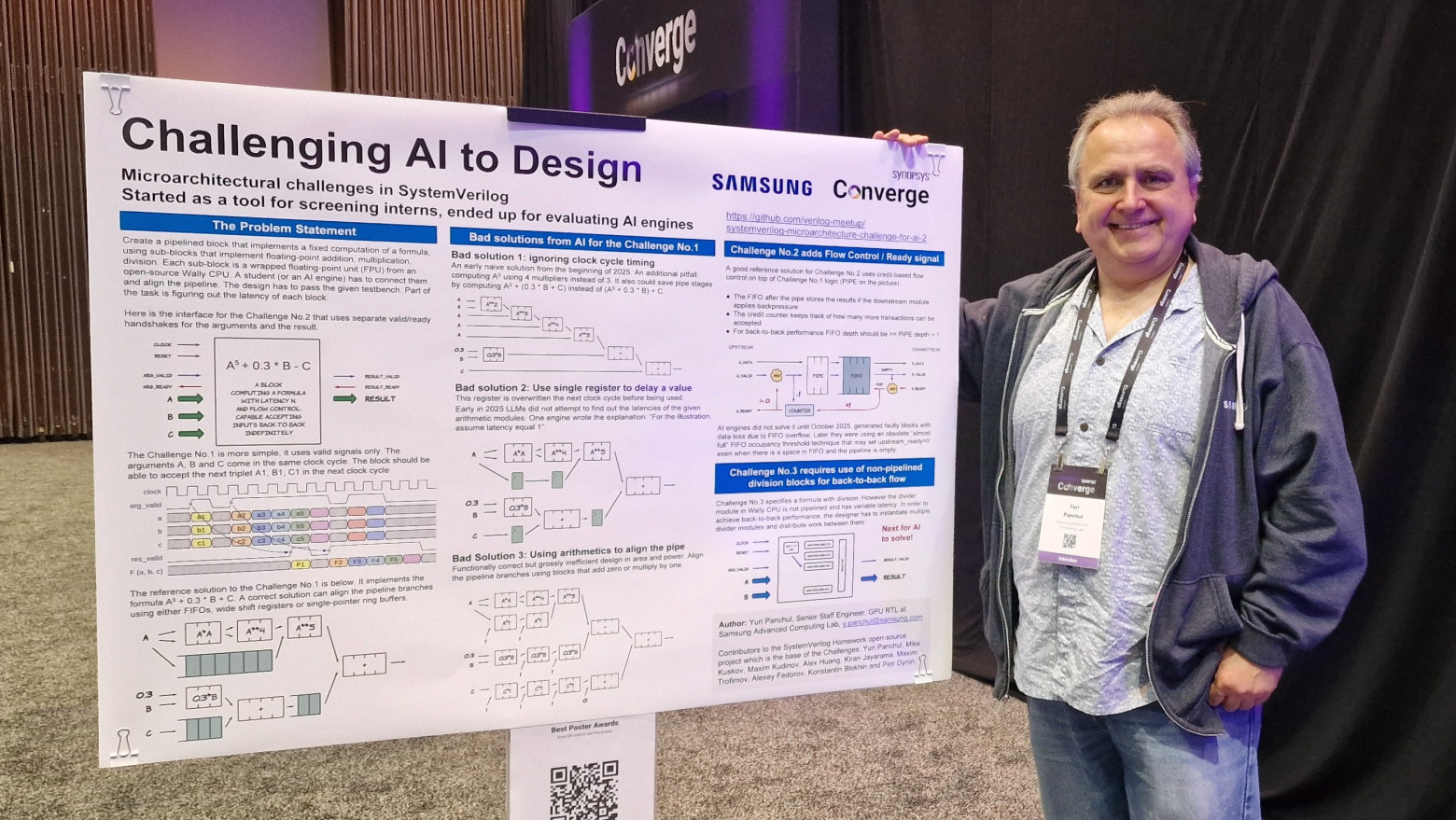

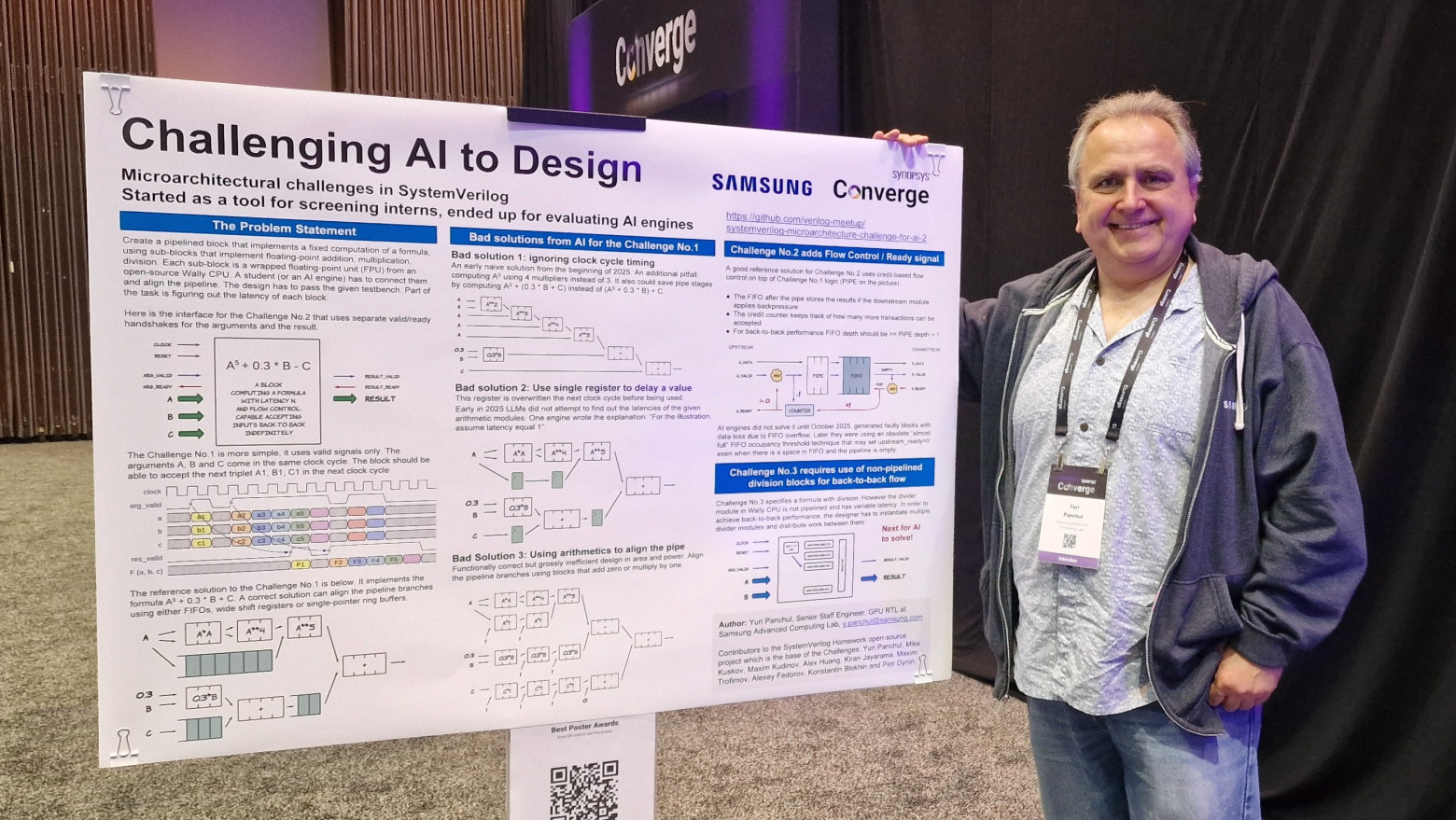

AI - не микроархитектор, не проектировщик и не верификатор. Это все-лишь гламурный поисковик уже решенных и опубликованных задач. Именно такой вывод следовал из предоставленных мною на конференции SNUG Silicon Valley 2026 Читать полностью »

AI - не микроархитектор, не проектировщик и не верификатор. Это все-лишь гламурный поисковик уже решенных и опубликованных задач. Именно такой вывод следовал из предоставленных мною на конференции SNUG Silicon Valley 2026 Читать полностью »

Привет! Меня зовут Михаил, я руковожу отделом верификации в YADRO. В этом посте я поделюсь нашим опытом верификации и рассмотрю организацию этой работы на разных уровнях. Останавливаться на всех технических подробностях не планирую, но постараюсь осветить все важные моменты, чтобы по итогам поста у вас сложилась цельная картина.

Многие современные вычислительные задачи, в частности повсеместная обработка изображений и звука или работа с матрицами для ИИ, хорошо поддаются параллелизации на уровне данных. Входные данные таких задач представлены в виде большого вектора данных, элементы которого можно обрабатывать независимо. Чтобы ускорить вычисления с векторами, производители процессоров добавили в архитектуры специальные Single Instruction, Multiple Data инструкции, которые позволяют работать за одну инструкцию сразу с несколькими элементами.