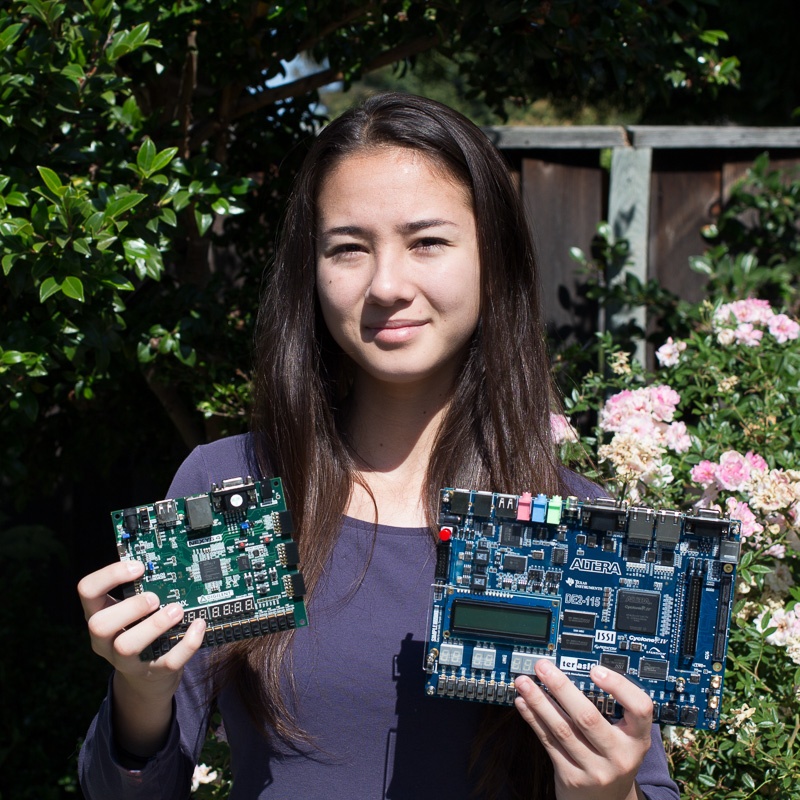

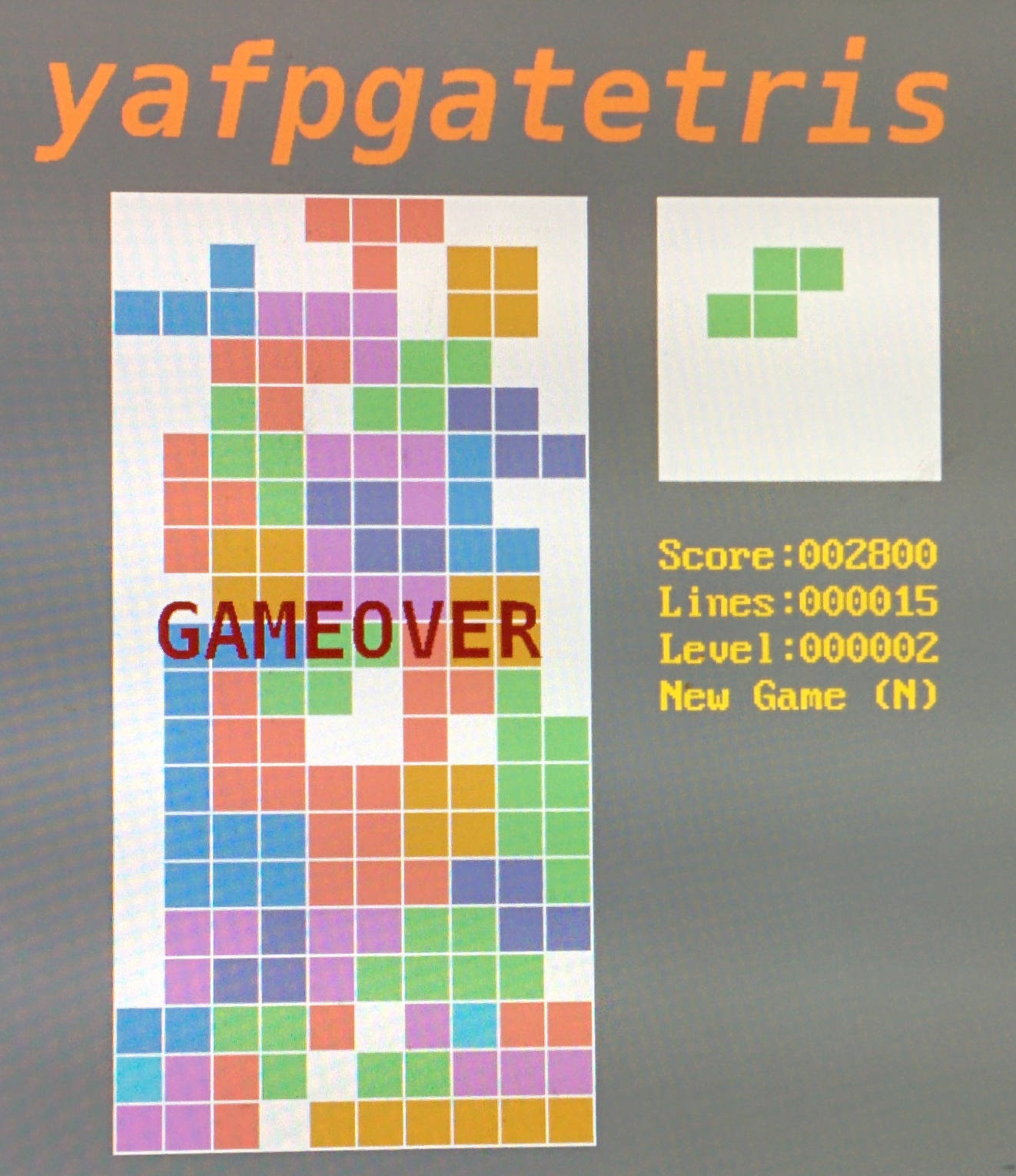

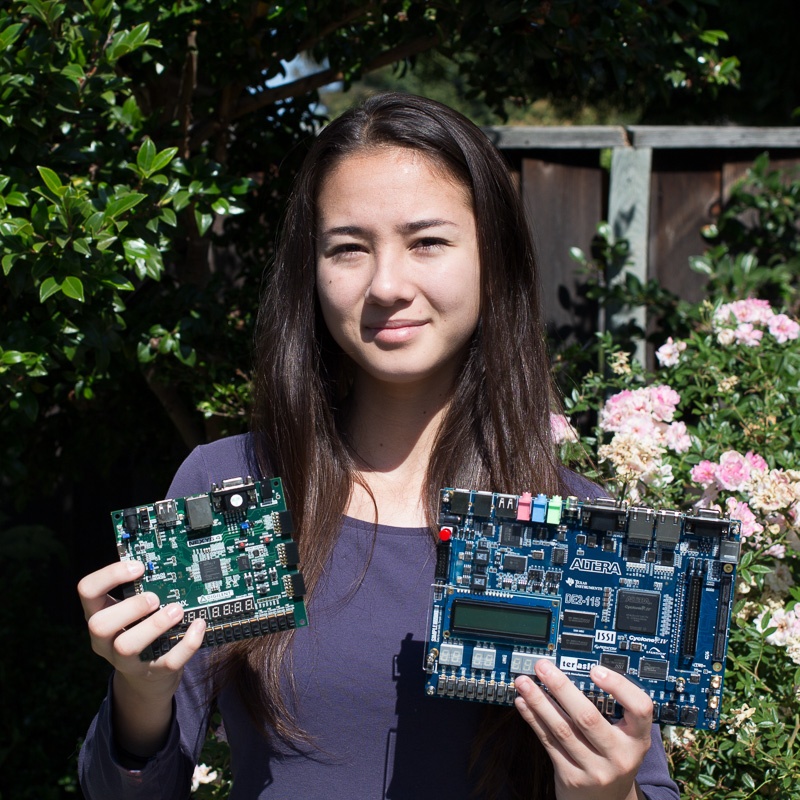

Господа! Мы с Тимуром Палташевым из AMD в Саннивейл, Калифорния, а также с несколькими соратниками из России, Украины и Казахстана решили спланировать несколько семинаров разных форматов, которые покрывают темы на стыке хардвера и софтвера: цифровая логика, Verilog, правила RTL (Register Transfer Level), введение в микроахитектуру (строение конвейера) процессоров, низкоуровневое программирование на ассемблере, использование микроконтроллеров, особенности чипов для интернета вещей, введение в RTOS-ы, лабы на ПЛИС-ах / FPGA, а также (для части аудитории, которая интересуется производством чипов) физические аспекты проектирования и производства на фабрике (для последнего мы решили привлечь материалы от преподавателя курса в Университете Калифорнии Санта Круз, отделение в Silicon Valley).

Цель этого поста — обсудить кому что нравится на основе детального плана первого из таких семинаров, который будет в Казахстане. Идея данного семинара в том, чтобы пригласить некоторое преподавателей казахстанских вузов и сделать для них обзор, чтобы помочь им сориентироваться, в каких местах можно повысить качество их программ в программировании встроенных систем, электронике, а также затронуть связанные области типа интернета вещей и роботики.

Читать полностью »