Вечером в пятницу коллега, назовем его Мститель, спросил, не сталкивался ли я с проблемой, что route возвращает 400... но «если сменить название на сильно другое», то всё ок. Я сперва не обратил внимание на слово «сильно». Может быть, где-то дублируется регистрация этого рута? Или мститель перепутал GET и POST. Или какой-то баг в общем на создание хэндлеров?

Мистическая буква «М»

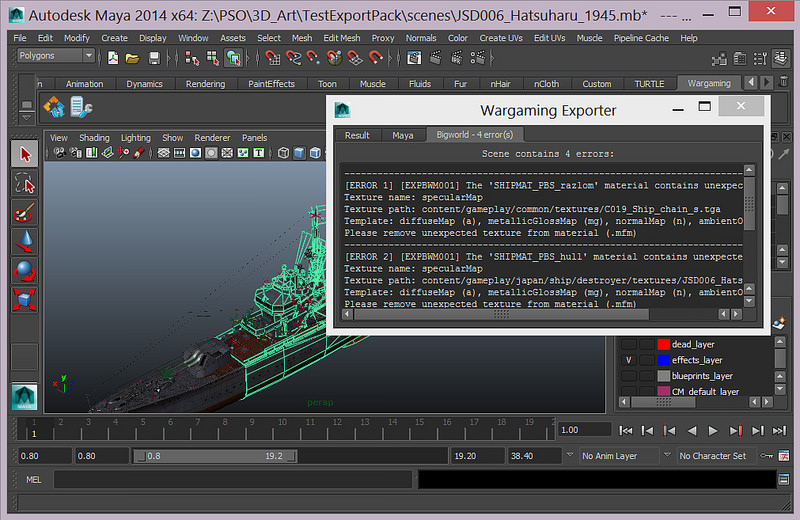

Утро понедельника началось с хождения по мукам. Убийства gradle-демонов. Обновление JDK. Чистый билд. Удаление кода авторизации. Возня с call logging. Дебаггер. Тщетно — нигде никаких логов об ошибке.