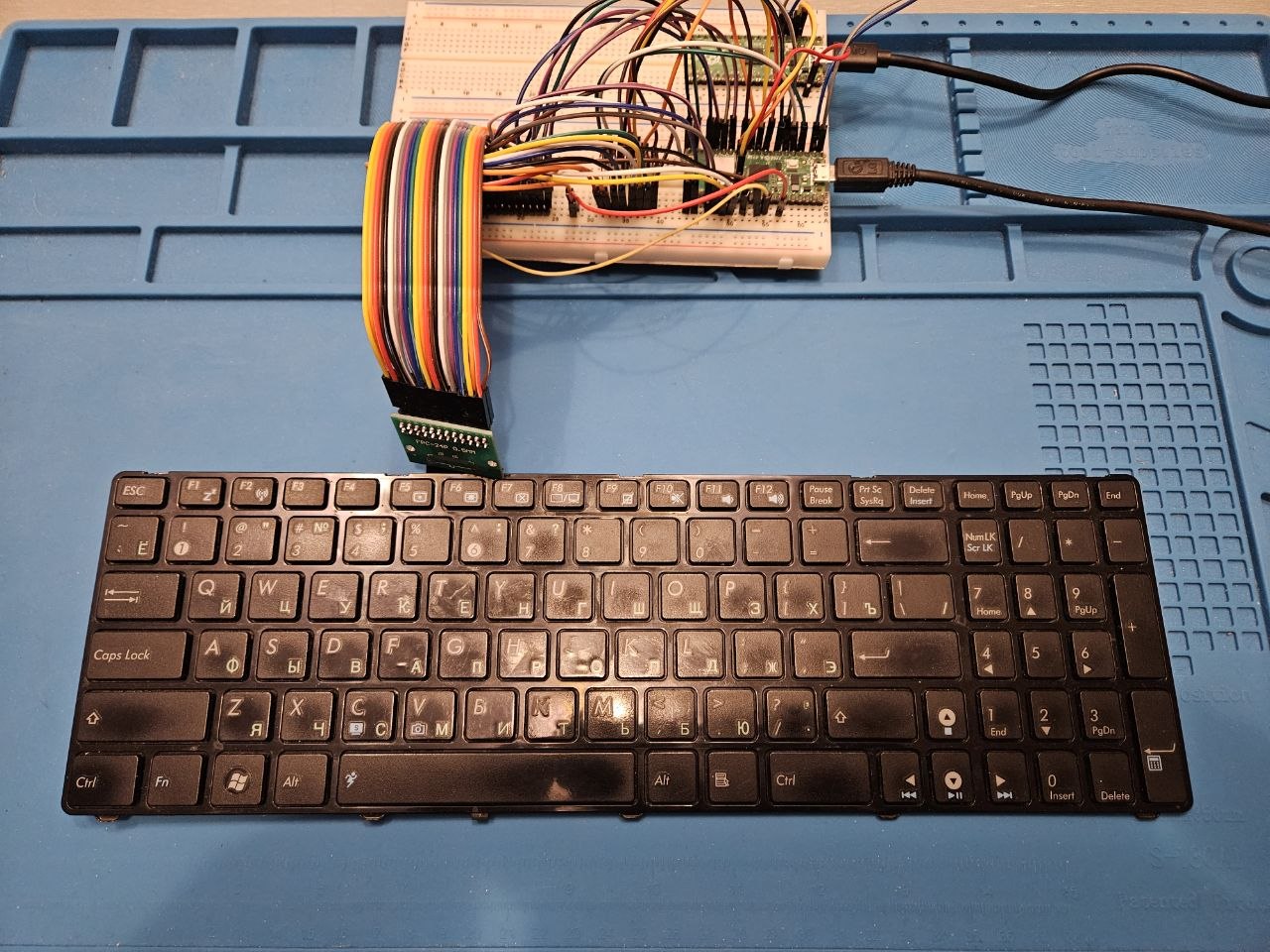

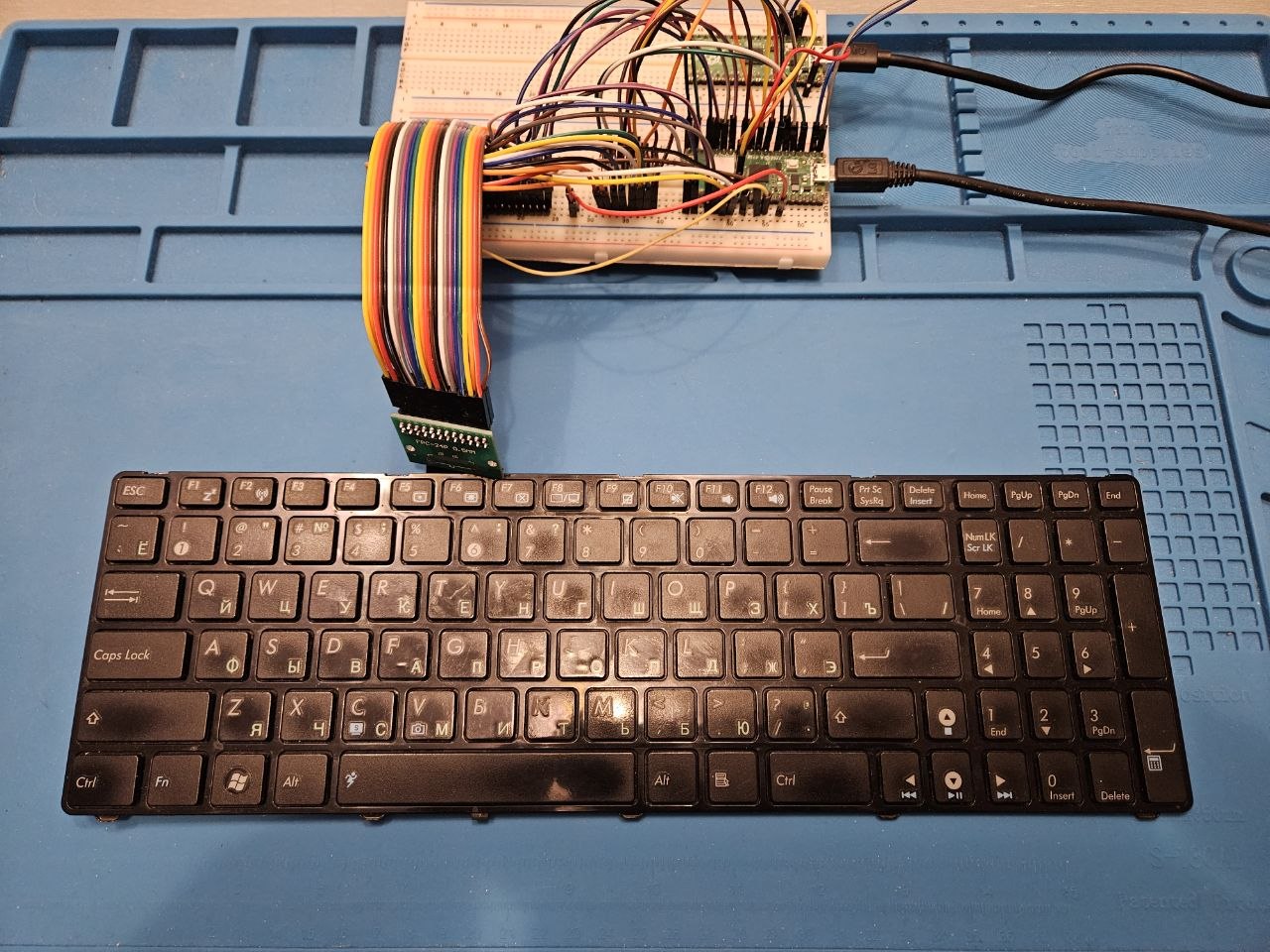

По созданию клавиатур на Хабре написано много статей, но, как правило, они подразумевают кастомизацию прошивки QMK или использование уже готовой.

По созданию клавиатур на Хабре написано много статей, но, как правило, они подразумевают кастомизацию прошивки QMK или использование уже готовой.

В общем случае с помощью shell команды можно получить любую метрику, без написания кода и интеграций. А значит в консоли должен быть простой и удобный инструмент для визуализации.

Наблюдение за изменением состояния в базе данных, мониторинг размера очередей, телеметрия с удаленных серверов, запуск деплой скриптов и получение нотификации по завершению — конфигурируется за минуту простым YAML файлом.

Код доступен на гитхабе. Инструкции по установке — для Linux, macOS и (экспериментально) Windows.

Привет! Представляю вашему вниманию перевод статьи «Ditch MVPs, Adopt Minimum Viable Prototypes (MVPr)» автора Alexandru Giuseppe Ispas.

Стремление к совершенству — это тонкая ловушка, которая часто приводит дизайнеров в бесконечный цикл итераций и доработок. Это особенно справедливо в мире цифровых продуктов, где каждое взаимодействие и графический элемент могут стать объектом дизайнерской одержимости.

Но если абстрагироваться и посмотреть на междисциплинарный характер дизайна цифрового продукта, легко понять, как дизайнеры попадают в идеальную ловушку.

Читать полностью »

Дизайн – это решение проблемы. Продукты, которые мы создаем, хороши ровно настолько, насколько хорошо мы изначально определили и поняли проблемы, которые хотим решить. Когда компания хочет изменить продукт и сделать это быстро, у дизайн команды не так много времени на поиск и предоставление заказчику жизнеспособного решения.

На встрече 26 октября в питерском офисе Wrike в рамках WrikeTechClub мы поговорим о том, как построить эффективную работу над юзабилити, как провести необходимые исследования и извлечь из них правильные выводы, как выявить фатальные ошибки и суметь их исправить в кратчайшие сроки, рассмотрим новые методологии и разберем с экспертами конкретные кейсы. На митапе выступит CEO и основатель компании Wrike Андрей Филев, который расскажет о последних изменениях облика Wrike в связи с современными тенденциями работы над IT-продуктом.

Читать полностью »

Как создать свою игру? Сколько на этом можно заработать? Какая нужна команда? Каковы ключевые этапы разработки и что нужно делать команде на каждом этапе? Ответ на эти вопросы – в открытой лекции по геймдизайну в рамках программы «Менеджмент игровых интернет-проектов», которую разместили наши партнеры — открытая система электронного образования Универсариум. Вот здесь можно посмотреть открытую лекцию:

А под катом вы найдете краткое текстовое описание.

23 апреля прошла конференция ProfsoUX. Пятый год подряд на этом мероприятии собираются вместе UX-профи и другие специалисты со всей страны, люди, которых объединяет желание проектировать удобные, эргономичные и эффективные интерфейсы. Здесь царит особая атмосфера вдохновения и творчества, и это заслуга не только организаторов, но и участников.

Я расскажу о том, что представляла собой конференция, с точки зрения начинающего проектировщика: чего ожидали участники, и в какой мере оправдались эти ожидания.

Читать полностью »

В моей прошлой статье я рассказала про то, как начать с работу с Framer, создавать красивые прототипы с помощью импорта слоев из Sketch, а также показала, как создать симпатичный loading с процентами.

После того, как статью опубликовали на habrahabr — вот здесь, я решила продолжить свои эксперименты с Framer, просто потому что уже не вижу своих дизайнерских будней без этой увлекательной штуковины.

Целью нового прототипа стал опять же loading, но уже другого формата, созданный без импорта слоев из чего бы то ни было. Прототип служит для иллюстрации возможностей Framer и для описания моих экспериментов с кодом.

Итак, вот что мы создадим в этот туториале:

Читать полностью »

Некоторое время были у меня в руках предметы, интересные в первую разработчикам интерфейсов сайтов/программ, а именно трафарет и блокнот для iOS-интерфейсов. Когда-то в комментариях упоминали об этой продукции компании «UI Stencils», но информации было мало и решено было взять на пробу.

Ниже мое субъективное мнение, которое может не совпадать с вашим.

Читать полностью »

Так сложилось, что вот уже год как я проживаю в холодной Финляндии. Изначально приехал сюда учиться, но последние несколько месяцев активно подыскиваю себе работу: занимался массовой рассылкой своего резюме, посетил многие ивенты/конференции, побывал в нескольких офисах разных финских геймдев-контор. Коих, к слову, тут довольно много: благо, местная International Game Developers Association (в отличии от родной, украинской) живет, здравствует и собирает народ на халявное пиво раз в месяц. Так вот, я заметил, очень многие компании (вместительностью 10-20 человек) или переходят, или уже перешли на Unity3D.

Изначально статья планировалась как философское размышление на тему баланса что_прогер_пишет/что_игрок_видит, с примесями полезных сниппетов/хинтов по работе с Unity. На самом деле, во время выполнения тестового задания в одну из компаний, ко мне внезапно нагрянула муза написать подобную статью, посему я пока не знаю, что из этого выйдет.