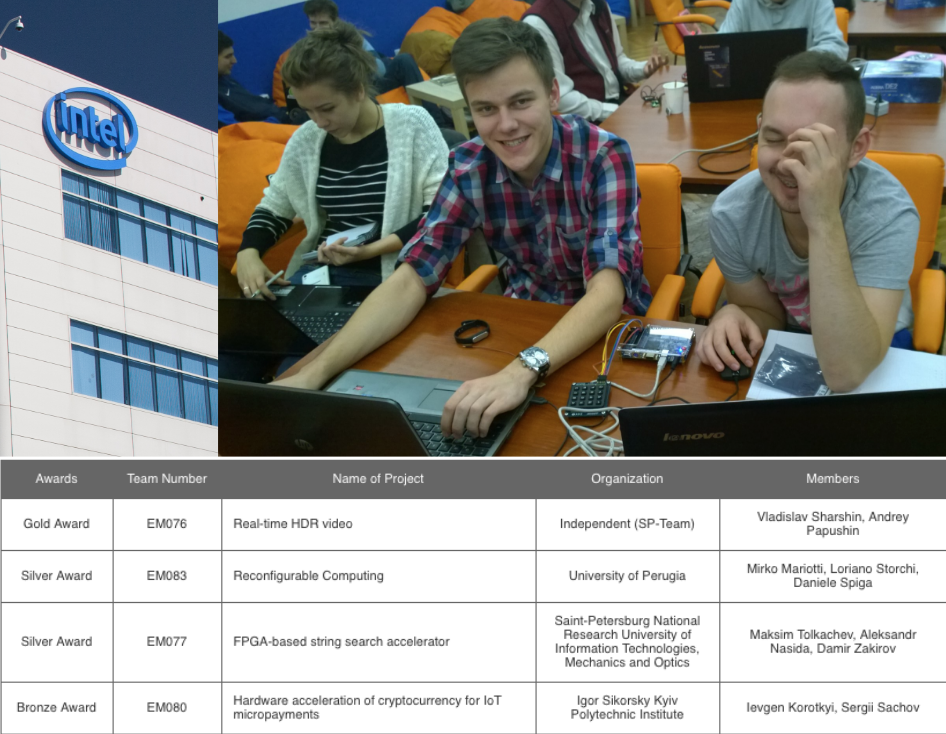

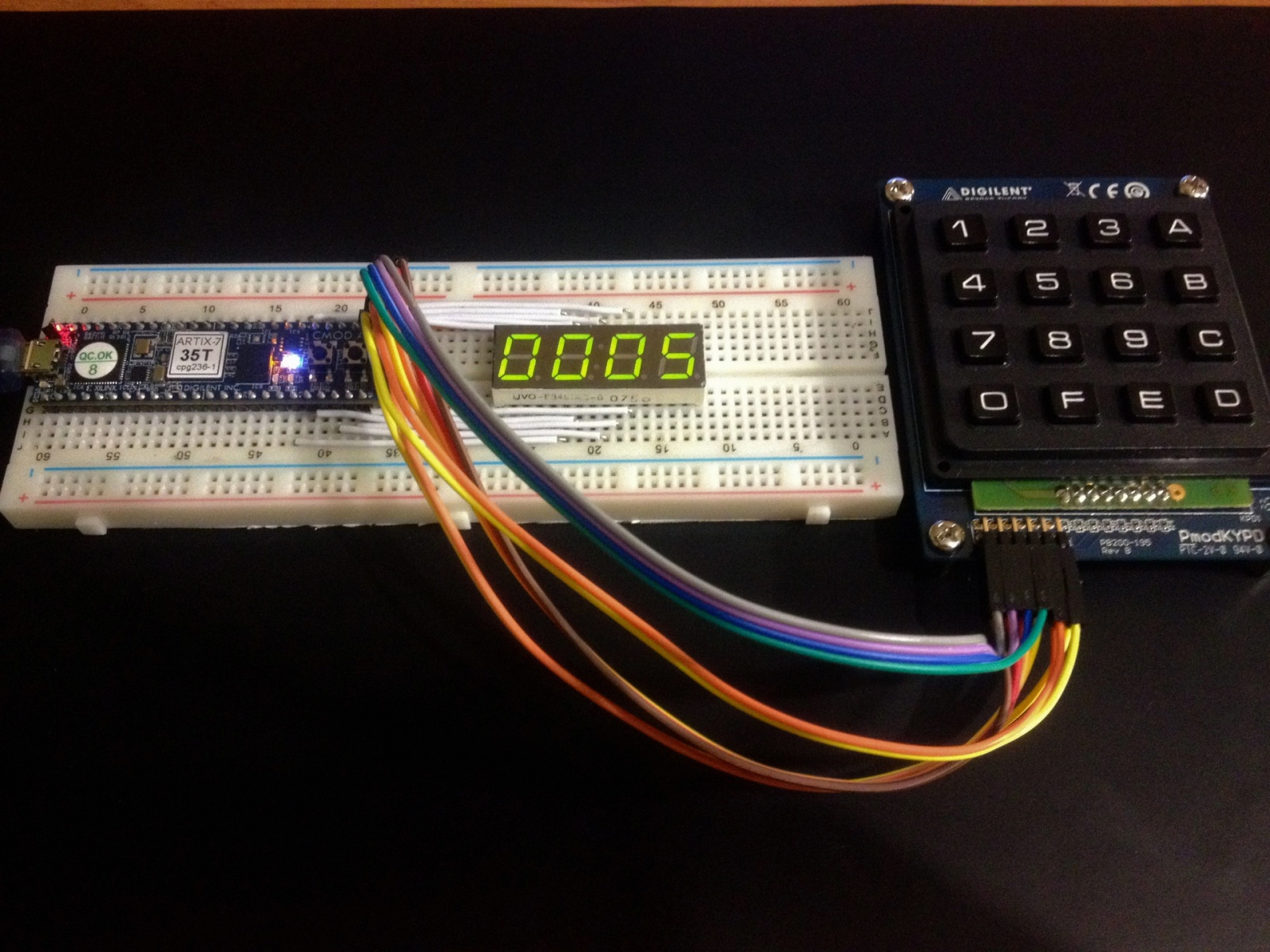

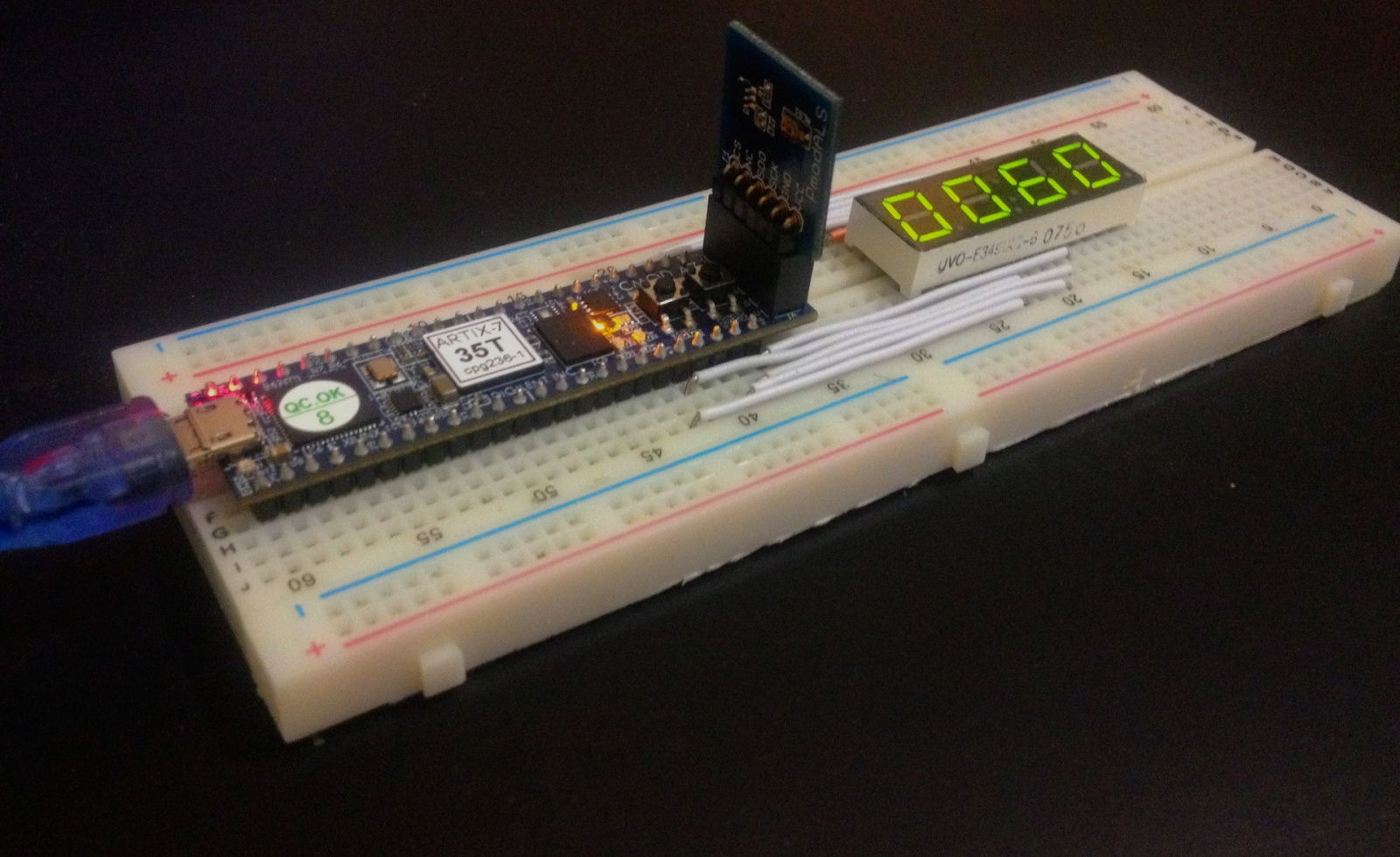

Золото досталось России, серебро разделила Россия и Италия, бронза досталась Украине. Таковы результаты европейского финала престижного соревнования InnovateFPGA под эгидой Интела. Победители поедут в Калифорнию, где встретятся с финалистами из Америки и Азии. Надеюсь, теперь не нужно будет объяснять на Хабре, почему Verilog и ПЛИС/FPGA стратегически важны, несмотря на то, что «вакансий на джаву больше».

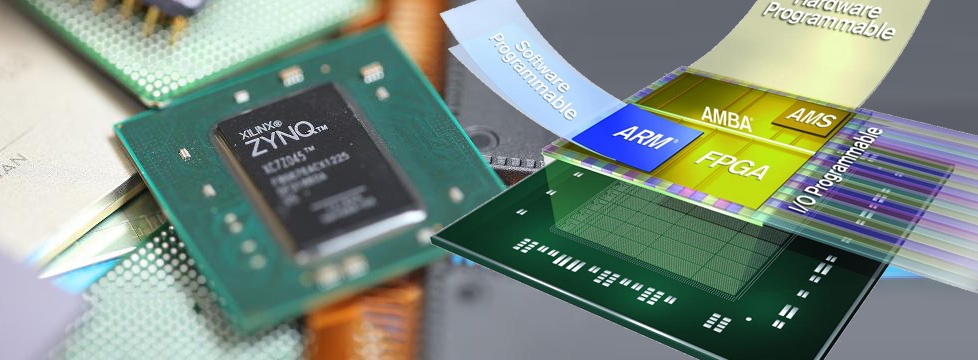

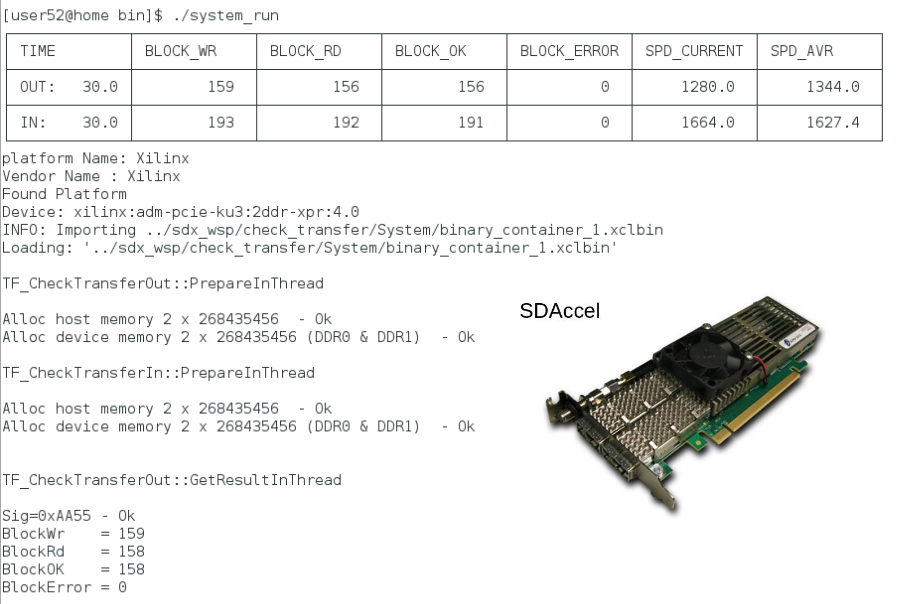

Студенты, которые сейчас делают проекты на ПЛИСах, через несколько лет будут делать массовые микросхемы для самоуправляемых автомобилей, ускорителей нейронных сетей, дополненной реальности и других приложений, в который обычный процессор не справляется. Именно поэтому Intel потратил 16.7 миллиардов долларов на покупку Altera и вход в рынок ПЛИС. А на днях Интел купил еще и компанию eASIC для дешевой конверсии дизайнов из ПЛИС в ASIC (в eASIC есть достаточно многочисленная российская команда).

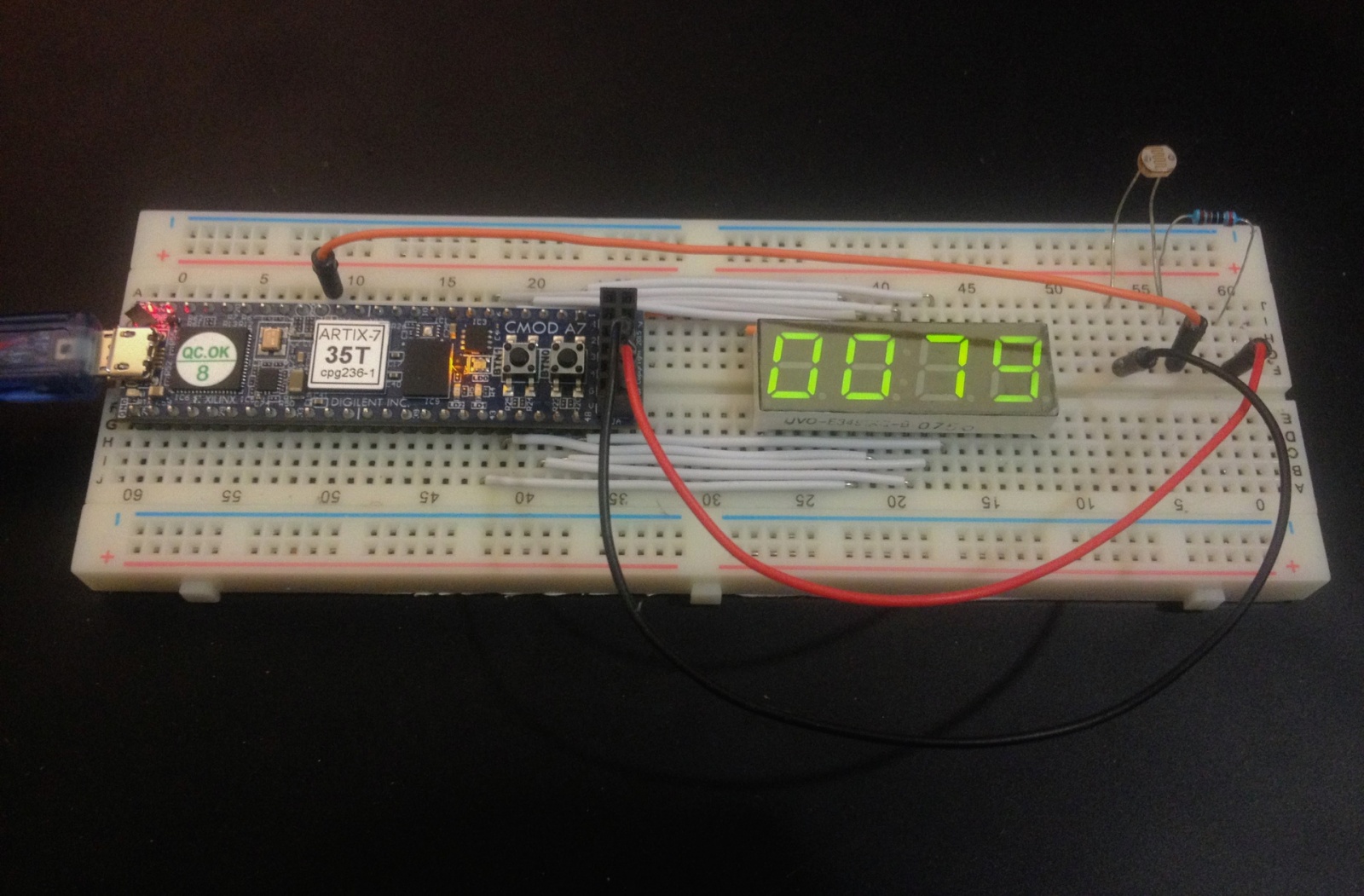

Победа российских и украинских команд в интеловском конкурсе InnovateFPGA возникла не на пустом месте, а в результате работы конкретных людей в ЛЭТИ, ИТМО, КПИ и других местах, о которых уже были статьи на Хабре. Если продолжить эти начинания и расширить преподавание ПЛИС и языков описания аппаратуры во все технические вузы от Калининграда до Якутии, от Львова до Тбилиси и Астаны — то через пару десятилетий это может изменить расстановку сил в мировой электронной промышленности примерно так же, как работы Курчатова и Королева изменили расстановку сил в мировой атомной промышленности и освоении космоса.