Перевод коллективной статьи Practical experiences based on MIPSfpga, не так давно представленной Сарой Харрис на симпозиуме в Торонто. Приводится подробное описание MIPSfpga 2.0, релиз которой состоялся 3 июля 2017 года. Основное, на мой взгляд, отличие по сравнению с версией 1.3: пакет лабораторных работ расширен набором, ориентированным на внутреннюю работу процессора. Так что, если вы хотите узнать, как работает современное ядро, то MIPSfpga 2.0 — это ваш выбор для качественного самообразования. Крайне полезной данная статья будет для преподавателей ВУЗов — подробно и с примерами рассматривается вопрос интеграции MIPSfpga 2.0 в учебный процесс, включая ее соответствие Методическим рекомендациям IEEE/ACM для программ бакалавриата в области вычислительной техники.

Рубрика «MIPS microAptiv UP»

MIPSfpga – практический опыт

2017-08-17 в 16:56, admin, рубрики: C, fpga, mips, MIPS microAptiv UP, MIPSfpga, SoC, Verilog, Анализ и проектирование систем, образование, перевод, программирование микроконтроллеров, системное программированиеПоднимаем Linux на MIPSfpga и ПЛИС Altera

2017-07-22 в 21:56, admin, рубрики: C, fpga, mips, MIPS microAptiv UP, MIPSfpga, SoC, Verilog, Анализ и проектирование систем, программирование микроконтроллеров, системное программирование

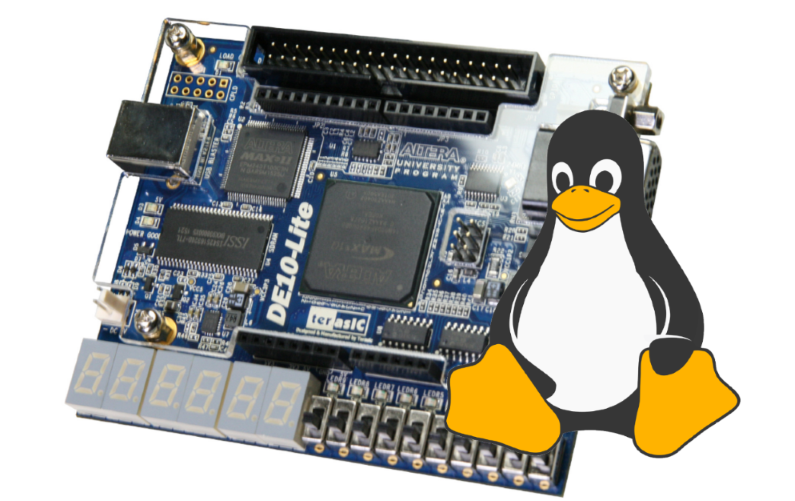

Предоставленная Imagination Technologies документация на MIPSfpga очень хорошо и подробно описывает развертывание Linux. Но используемая при этом система на кристалле построена с помощью Xilinx-специфических периферийных модулей. Потому ее повторение на отладочной плате с ПЛИС Altera в исходном виде представляется невозможным. Решением является система на кристалле MIPSfpga-plus с ее платформонезависимой периферией. О том, как запустить на ней Linux, читайте в этой статье.

Текущая активность вокруг MIPSfpga и не только

2017-07-19 в 17:27, admin, рубрики: C, fpga, mips, MIPS microAptiv UP, MIPSfpga, SoC, Verilog, Анализ и проектирование систем, программирование микроконтроллеров, системное программирование

Есть несколько событий и тем, которыми хотелось бы поделиться с сообществом. По-хорошему, по каждой можно писать отдельную статью, но общий дефицит времени заставляет немного схалтурить. Наши сегодняшние темы:

- релиз MIPSfpga 2.0;

- процессор schoolMIPS и Летняя школа юных программистов в Новосибирске;

- школа-семинар по цифровому дизайну и компьютерной архитектуре в Томске;

- запуск ванильного ядра Linux на MIPSfpga-plus;

- поддержка АЦП Altera MAX10 в MIPSfpga-plus;

- логотип MIPSfpga-plus.

Если тематика MIPSfpga-plus вам не безразлична, то в конце есть небольшой опрос на тему чего мне писать (или не писать) следующую статью. Ваш выбор поможет мне сориентироваться и расставить приоритеты. Welcome!

Портирование MIPSfpga на другие платы и интеграция периферии в систему. Часть 3

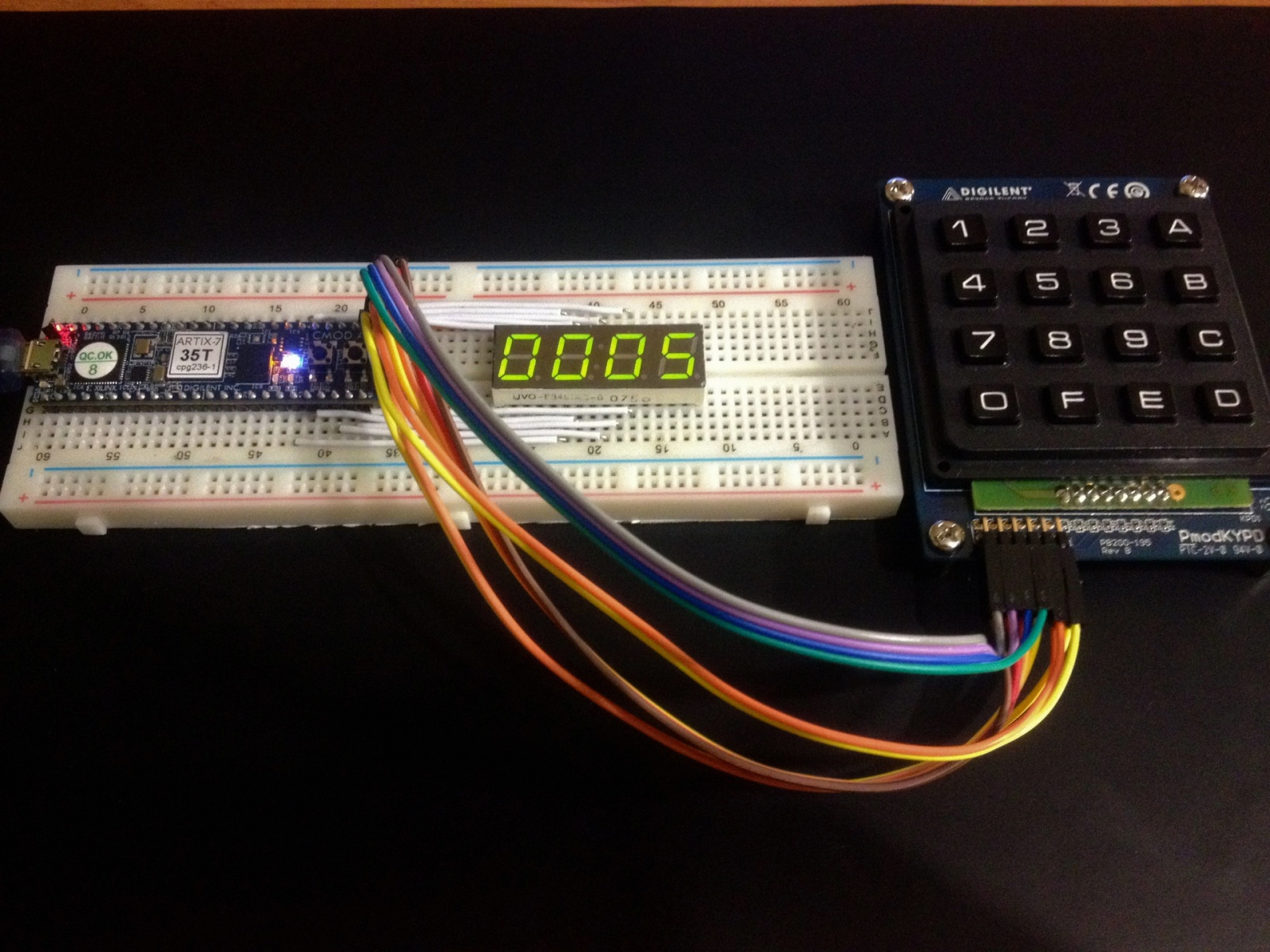

2017-05-31 в 3:55, admin, рубрики: Altera, fpga, imagination technologies, mips, MIPS microAptiv UP, MIPSfpga, SPI, uart, Verilog, vhdl, xilinx, Анализ и проектирование систем, параллельное программирование, ПЛИС, программирование микроконтроллеровВ первой части я описал на примере cmoda7 как портировать MIPSfpga (Портирование MIPSfpga на другие платы и интеграция периферии в систему. Часть 1) на FPGA платы отличные от уже портированых среди которых такие популярные как: basys3, nexys4, nexys4_ddr фирмы Xilinx, а так же de0, de0_cv, de0_nano, de1, DE1, de10_lite, de2_115, DE2-115 фирмы Altera(Intel), во второй части как интегрировать клавиатуру Pmod KYPD (Портирование MIPSfpga на другие платы и интеграция периферии в систему. Часть 2).

В этой части добавим к MIPSfpga-plus встроенный АЦП, и популярный LCD от Nokia 5100.

С предыдущих частей можно сделать вывод, что интеграция периферии в MIPSFPGA состоит из пять основных этапов:

- Добавление модуля интерфейса общения с периферией (i2c, spi, и т.д.).

- Соединение входных/выходных портов модуля с шиной AHB-Lite.

- Присваивание адресов сигналов подключаемого устройства.

- Добавление констрейнов на физические контакты платы.

- Написание программы для MIPS процессора.

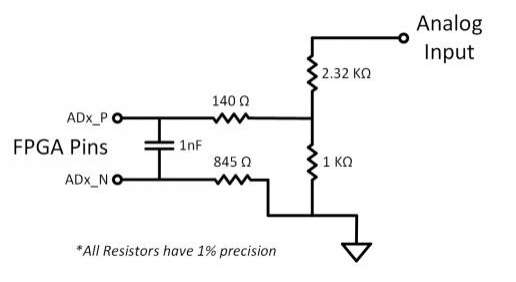

Подключение встроенного в cmoda7 АЦП

Как я уже говорил плата cmodA7 имеет встроенный АЦП, pin 15 и 16 используются в качестве аналоговых входов модуля FPGA. Диапазон работы встроенного АЦП от 0-1V, поэтому используется внешняя схема для увеличения входного напряжения до 3.3V.

Эта схема позволяет модулю XACD точно измерить любое напряжение от 0 В и 3,3 В (по отношению к GND). Чтобы работать с АЦП в Vivado существует блок IP (интеллектуальной собственности) Xilinx, с помощью которого можно будет просто его интегрировать в нашу систему MIPSfpga.

Читать полностью »

Портирование MIPSfpga на другие платы и интеграция периферии в систему. Часть 2

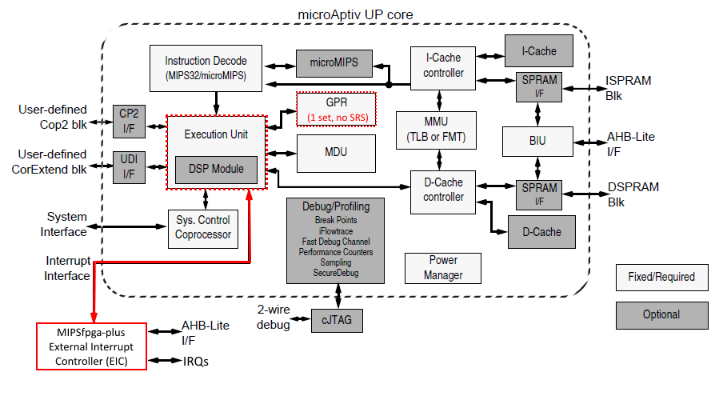

2017-05-31 в 3:39, admin, рубрики: Altera, fpga, imagination technologies, mips, MIPS microAptiv UP, MIPSfpga, SPI, uart, Verilog, vhdl, xilinx, Анализ и проектирование систем, ПЛИС, программирование микроконтроллеровMIPSfpga микропроцессор MIPS32 microAptiv описаный на языке Verilog для образовательных целей фирмы Imagination, который имеет кэш-память и блок управления памятью. Код процессора доступен пользователю (инструкция по скачиванию) и может использоваться для моделирования и реализации процессора на FPGA плате.

Данная статья является продолжением статьи о том как портировать MIPSfpga-plus на другие платы, и в ней будет описано как интегрировать периферию в систему MIPSfpga:

Так же о том как начать работать с MIPSfpga написано в статье:

habrahabr.ru/post/275215

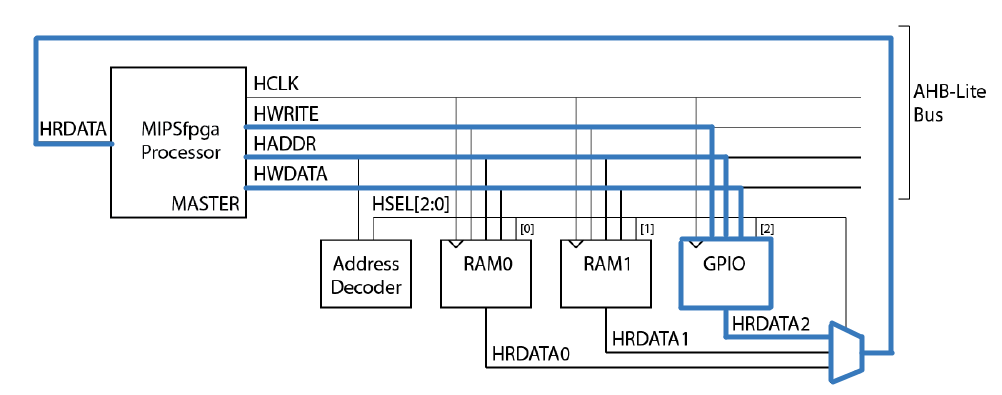

Процессор использует интерфейс памяти для связи с периферийными устройствами. То есть, это означает что данные записываются и считываются с подключенной периферии так же, как и с блока памяти RAM. Интеграция периферии в процессор осуществляется подключением к шине AHB-Lite(подробная документация). Подробней попробуем разобраться в процессе подключения.

Для начала нужно иметь понятие как будут проходить сигналы по шине AHB-Lite:

Видно, что процесс считывания данных с периферии осуществляется по сигналу HRDATA, передача данных производится по HWRITE с активным высоким уровнем на сигнале разрешения записи, выбор GPIO осуществляется выбором адреса на HADDR.

Читать полностью »

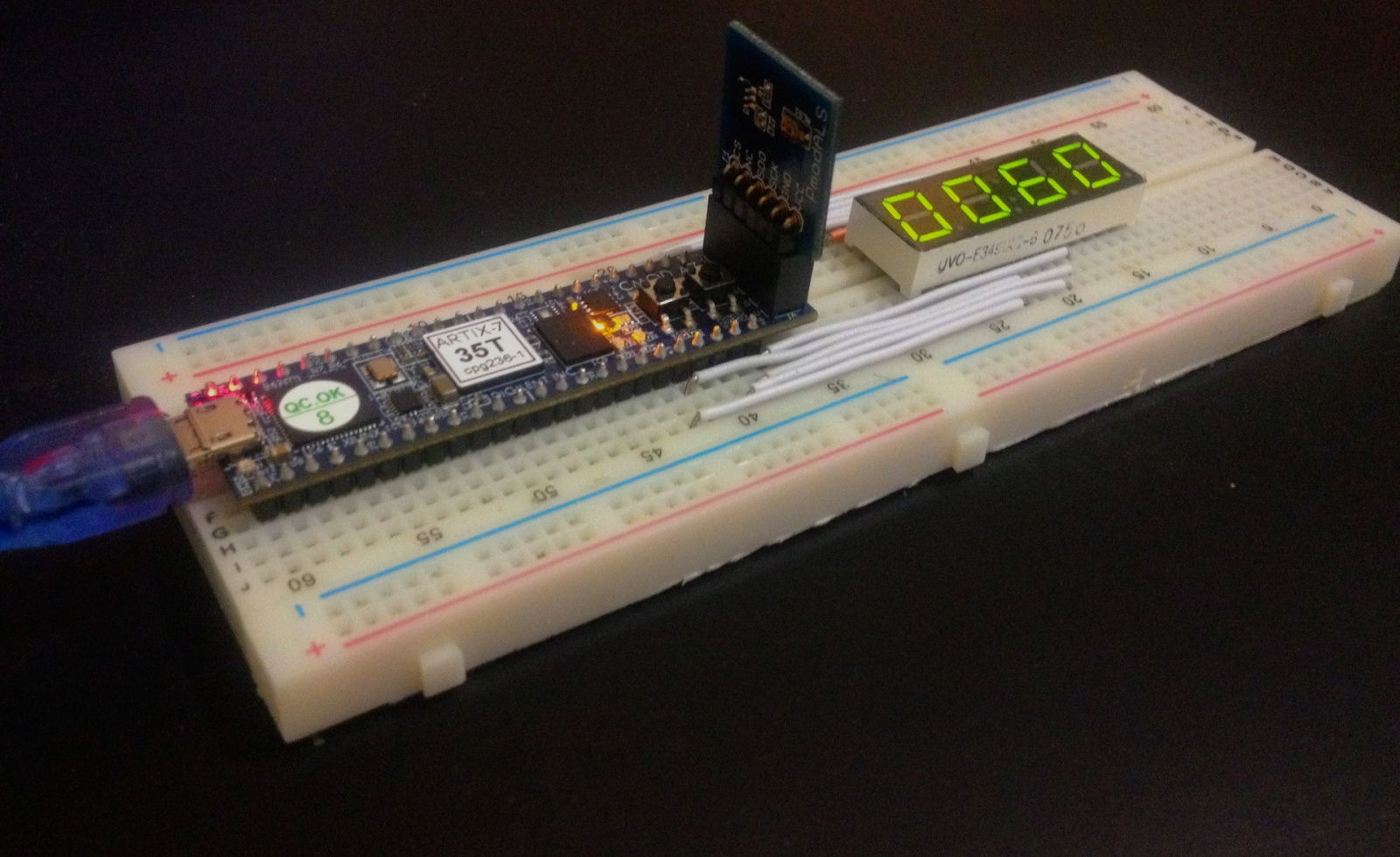

Портирование MIPSfpga на другие платы и интеграция периферии в систему. Часть 1

2017-05-30 в 13:19, admin, рубрики: Altera, fpga, imagination technologies, mips, MIPS microAptiv UP, MIPSfpga, SPI, uart, Verilog, vhdl, xilinx, Анализ и проектирование систем, ПЛИС, программирование микроконтроллеровMIPSfpga представляет собой предназначенный для образовательных целей микропроцессор MIPS32 microAptiv фирмы Imagination, который имеет кэш-память и блок управления памятью. Код процессора на языке Verilog доступен пользователю и может использоваться для моделирования и реализации процессора на FPGA плате.

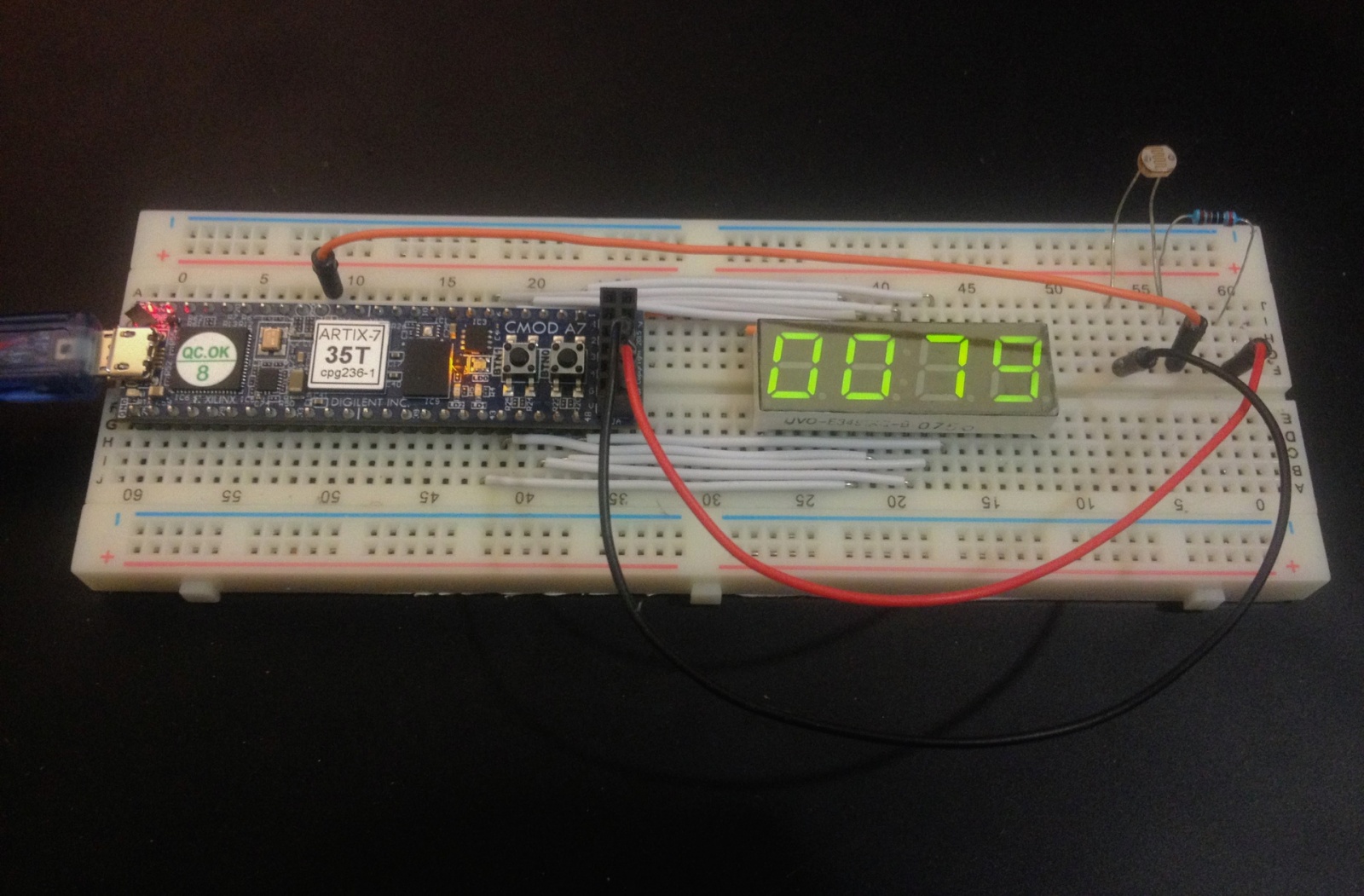

В даной статье будет описано на примере Digilent cmodA7 как портировать процессор MIPSfpga-plus на другие платы.

На сегодняшний день MIPSFPGA портирован на популярные платы таких фирм как ALTERA и Xilinx, среди них Basys 3, Nexys4 ddr, и другие (полный список находится на github). Такие платы наиболее популярны среди разработчиков на FPGA. Цена на такие платы довольно не маленькая, да и загружаются программы в ядро MIPSfpga с использованием интерфейса EJTAG и адаптера Bus Blaster ценой около 50$. Адаптер Bus Blaster получает команды по высокоскоростному кабелю USB 2.0 и преобразует их в последовательный протокол EJTAG, это позволяет загружать программы в ядро MIPSfpga и управлять отладкой программ, которые на нем выполняются. Проблема с относительно дорогим Bus Blaster была решена введением в систему MIPSfpga ряда улучшений. Улучшеный вариант системи MIPSfpga, названый MIPSfpga-plus включает в себя такие новые функции:

— Возможность загрузки программного обеспечения с использованием USB-to-UART коннектора ценой в $ 5 FTDI вместо $ 50 Bus Blaster, который иногда не так уж и легко достать.

— Возможность изменять тактовую частоту на лету с 50 или 25 МГц до 1 Гц (один цикл в секунду) для наблюдения за работой процессора в режиме реального времени, включая промахи в кэш-памяти и перенаправления конвеера.

— Пример интеграции датчика освещенности с протоколом SPI.

— Небольшая последовательность инициализации программного обеспечения, которая вписывается в 1 КБ вместо 32 КБ памяти, что позволяет переносить MIPSfpga на более широкий выбор плат FPGA без использования внешней памяти. Реализация UART описана в статье: MIPSfpga и UART.

Читать полностью »

MIPSfpga и UART

2017-03-29 в 20:18, admin, рубрики: C, fpga, mips, MIPS microAptiv UP, MIPSfpga, SoC, Verilog, Анализ и проектирование систем, программирование микроконтроллеров, системное программированиеПрошло чуть больше месяца с тех пор, как я портировал open source модуль UART16550 на шину AHB-Lite. Писать об этом на тот момент было несколько не логично, так как еще не была опубликована статья про прерывания MIPSfpga.

Если вы опытный разработчик, то для вас только одна полезная новость: UART16550 добавлен в состав системы MIPSfpga-plus, дальше можете не читать. А тем, кого интересует разобранный пример использования этого модуля — добро пожаловать под кат.

MIPSfpga и прерывания

2017-03-27 в 11:59, admin, рубрики: C, fpga, mips, mips assembler, MIPS microAptiv UP, MIPSfpga, SoC, Verilog, Анализ и проектирование систем, программирование микроконтроллеров, системное программированиеВ статье приводится несколько примеров настройки и использования прерываний MIPS32 Release 2, включая подробное описание задаваемой при этом конфигурации, описывается работа с контроллером внешних прерываний.

Весь описываемый код опубликован на github в составе проекта mipsfpga-plus [L3].

Новый курс по микроконтроллерам — совместный проект индустрии и университетов

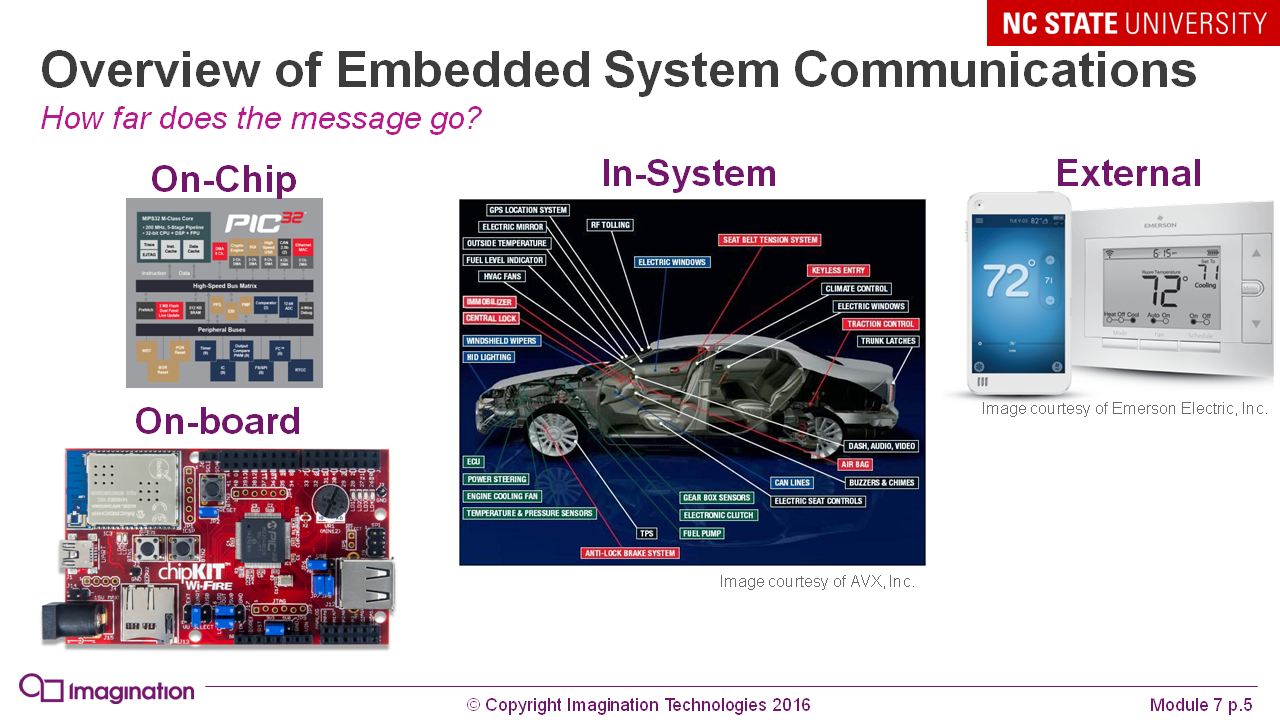

2016-04-20 в 6:06, admin, рубрики: assembly, cloud computing, digilent, imagination technologies, Microchip Technology, mips, MIPS microAptiv UP, national instruments, PIC32MZ, rtos, интерфейсы, Облачные вычисления, параллельное программирование, программирование микроконтроллеровБританская компания, две американские компании и 18 университетов (включая российские МИЭТ, ИТМО, СГАУ, ННТУ) сотрудничали, чтобы выпустить современный курс по микроконтроллерам c небольшой привязкой к интернету вещей. Об этом – сегодняшний пресс-релиз Imagination Technologies, Microchip Technology и Digilent (отделения National Instruments). Главный автор — профессор Александр Дин из университета Северной Каролины. В отличие от более легковестных курсов интернета вещей, новый курс подводит под предмет твердую инженерную базу – в нем подробно обсуждается использование RTOS-ов, архитектура микропроцессорного ядра микроконтроллера, протоколы периферии и даже оптимизация алгоритмов при программировании.

Скачать курс можно здесь:

https://community.imgtec.com/university/resources/connected-microcontroller-lab/

В пресс-релизе, помимо цитат из США, Великобритании, Германии, Китая, есть и цитата из России:

– Alexey Pereverzev, Head of Computer Engineering, National Research University of Electronic Technology (MIET), Russia

Пару десятков слайдов из курса, чтобы вы почувствовали его вкус:

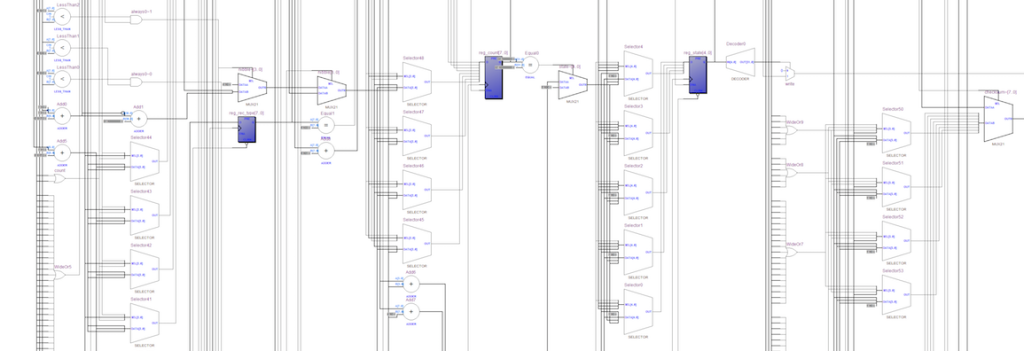

Как делать парсинг текста голым хардвером, без процессора и без софтвера

2016-03-10 в 6:53, admin, рубрики: Altera, altera de0-cv, altera de0-nano, digilent basys 3, digilent nexys 4 ddr, elf, fpga, mips, MIPS microAptiv UP, MIPSfpga, motorola s-records, regular expressions, state machine, turing machine, Verilog, vhdl, xilinx, Анализ и проектирование систем, ненормальное программирование, ПЛИС, программирование микроконтроллеров, Регулярные выраженияКто-то парсирует текстовый файл программой на Питоне, другой пишет скрипт с регулярными выражениями на Перле, Си-программист стыдливо возится с буферами и указателями, иногда применяя Yacc и Lex.

А можно ли парсировать текст голым железом? Вообще без программы?

— А как это?, — спросил меня знакомый, — С помощью Ардуино?

— Внутри Ардуино стоит вполне фон-неймановский процессор и работает программа, — ответил я, — Нет, еще более голое железо.

— А-а-а-а, этот, микрокод?, — догадался мой товарищ и взглянул на меня победно.

— Нет, термин «микрокод» использовался для специфической организации процессоров в 1970-е годы, потом его использование сошло на нет, — ответил я и добавил, — Правда есть еще микрооперации в интеловских процессорах, в которые перекодируется x86, но это тоже другое. Нет, я имею в виду парсинг текста устройством, состоящим из логических элементов И-ИЛИ-НЕ и Д-триггерами, как на картинке ниже.

— Невозможно! — воскликнул мой приятель, — в таком устройстве где-то сбоку должен сидеть процессор и хитро подмигивать!

— Почему это невозможно?, — парировал я, — Вот машину Тьюринга знаешь? Парсирует текст на ленте, а сбоку никакие интелы и ардуино не подмигивают.

— Нуу, машина Тьюринга, — протянул приятель, — это абстракция, типа Демона Максвелла.

— Никакой абстракции, сейчас увидишь работающую схему, парсирующую текст, — сказал я и прибавил, — но сначала расскажу, зачем мне вообще это понадобилось.