Часть I

Часть II

Часть III

Часть IV

Часть V

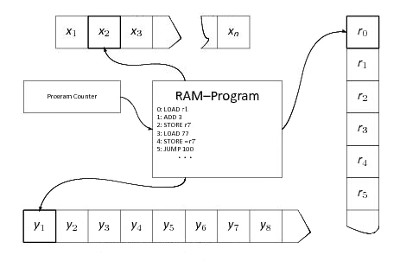

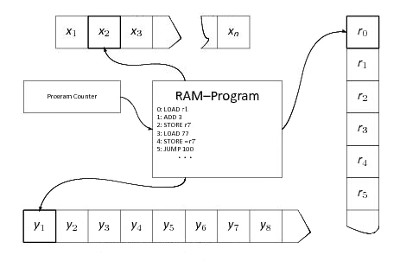

На Хабре уже была опубликована статья, посвящённая RAM-машине.

Вообще, статья про RAM-машину есть на Википедии.

RAM-машина, которая упоминается в книге «Построение и анализ вычислительных алгоритмов» -авторы: Ахо, Хопкрофт, Ульман — имеет ограниченный набор арифметических команд, у нас же из арифметических команд будут только «сложение» и «вычитание». Кроме арифметических доступны также команды ввода-вывода, косвенной адресации и команды ветвления.

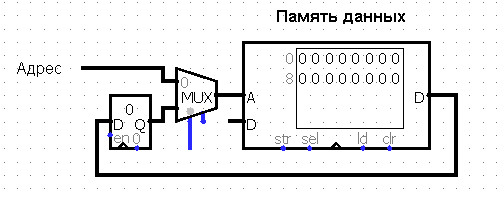

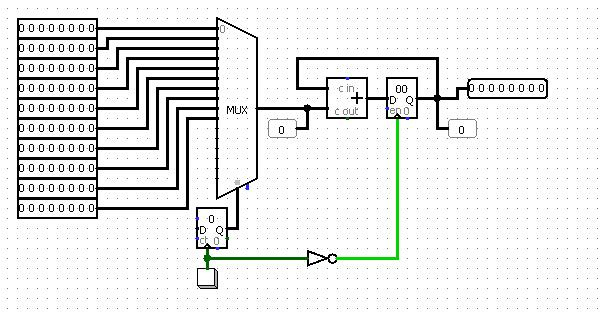

Отличием LIttle Man Computer'а (который я описывал в предыдущих частях цикла) от RAM-машины является механизм, обеспечивающий косвенную адресацию (возможность работать с числом, хранящемся в памяти, как с адресом).

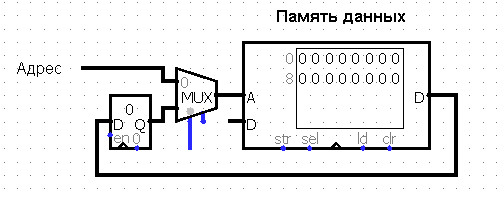

Для того, чтобы работать с числом, хранящимся в памяти, как с адресом, подключим к адресному входу Памяти Данных мультиплексор MUX, осуществляющий выборку между, собственно, адресом (поступающим из Памяти Команд) и числом, представляющем адрес и хранящемся в Памяти Данных.

Читать полностью »