Через неделю будет выставка ChipEXPO, на которой для будет школа проектирования железа для начинающих с упражнениями на FPGA платах, а для более продвинутых - конференция Микроархитектура, верификация и физическое проектирование микросхем.

И на секции для школьников, и на секции для взрослых будут выступать проектировщики RISC-V процессора из Syntacore / Yadro Станислав Жельнио и Никита Поляков. Сегодня Коммерсантъ сравнил этот проект с полетом на Луну.

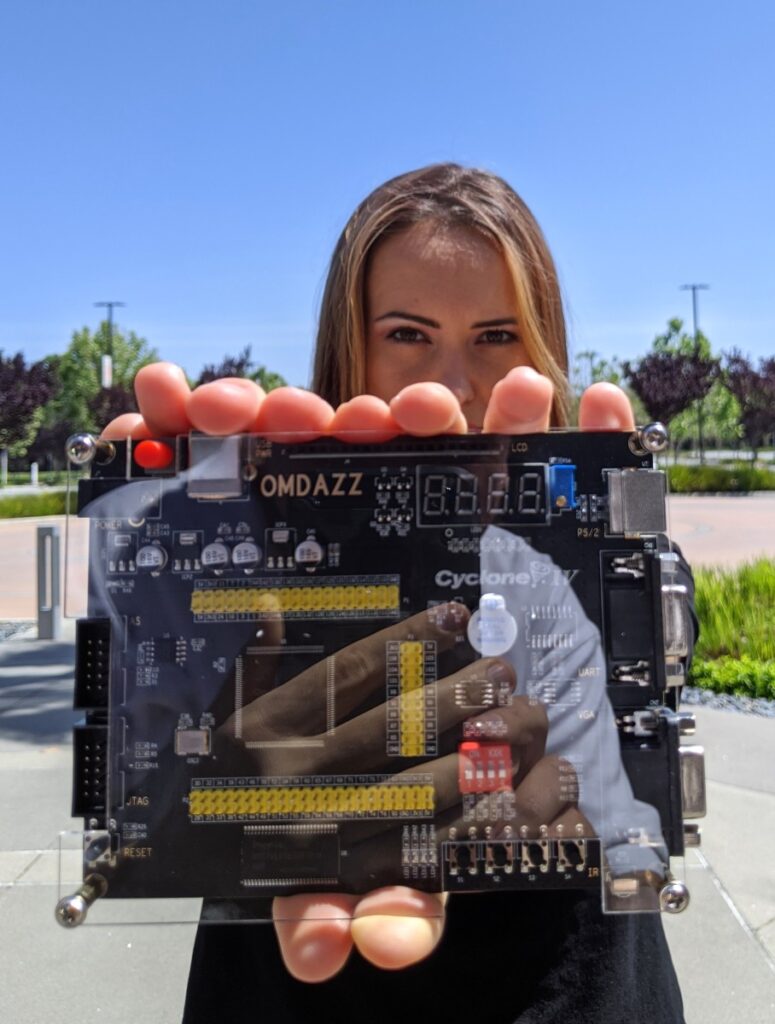

Количество заявок на школу существенно превысило количество посадочных мест, но у нас еще остался небольшой резерв FPGA плат, с бесплатной их раздачей школьникам и преподавателям из далеких от Москвы городов, которые могут принять участие в школе онлайн. В начале этой заметке мы опишем как получить плату и установить софтвер, нужный для упражнений.

Далее мы расскажем про новые упражнения в школе этого года - распознавание и генерацию музыки с помощью FPGA и приведем забавные сведения из советской физматшкольной книжки 1963 года как Бах изменил гаммы.

В конце поста мы покажем, как эта деятельность поможет получить в будущем интересные и высокооплачиваемые работы в Apple, Intel, SpaceX, как и самом в модном в этом сезоне российском микроэлектронном проекте - Syntacore / Yadro (в конце поста скриншоты их объявлений).

Прежде всего, так как количество заявок вдвое (а сейчас уже может и втрое) превысило количество мест офлайн, мы решили отдавать приоритет на посадочные места для тех, кто прошел три небольших онлайн-курса от Роснано «От транзистора до микросхемы», «Логическая сторона цифровой схемотехники» и «Физическая сторона цифровой схемотехники».

Этот курс гарантирует, что человек, который садится за стол с FPGA платой, по крайней мере не впервые в жизни слышит слова D-триггер и неблокирующее присваивание. Без этого человек будет переносить на код на языке описания аппаратуры Verilog свои ассоциации с программированием, и происходящее на плате будет казаться бредом. Также без курса может быть непонятно как упражнения с лампочками и кнопочками приводит к позиции проектирощика на уровне регистровых передач (Register Transfer Level (RTL) Desigfn Engineer) в тоp-20 электронных компаниях или в купленном Ядром стартапе Syntacore, который теоретически может превратить Россию в великую электронную державу лет через 10-20, аккурат к творческим вершинам карьеры современных школьников.

Прохождение этого курса также нужно, если вы не можете приехать в Сколково, но вы хотели бы получить плату, чтобы практиковаться удаленно. Эта опция доступна школьникам и преподавателям школ, вузов и кружков. Помимо платы вы получите микрофон и усилитель для упражнений со звуком. Вам нужно показать серфитикат после прохождения роснановского онлайн-курса и договориться с Михаилом Коробковым (Команда проекта FPGA-Systems.ru, fpga-systems@yandex.ru) чтобы он выслал вам плату.

Если у вас нет платы, вы не школьник и просто хотите посмотреть, вы можете присоединиться к занятиям Школы через интернет, на онлайн платформе eventwallet, на которую будут вестить прямые трансляции всех лекций и практических занятий Школы. Для этого нужно зайти на платформу, зарегистрироваться и перейти на вкладку ПРОГРАММА в левом меню. Там увидите виртуальный конференц-зал, в котором будет идти трансляция.Можно задавать вопросы спикерам в режиме чата.

Деньги на платы, перевод и трансляцию мероприятия дали: Cadence Design Systems, Siemens EDA / МЕГРАТЕК (Megratec - Mentor Graphics Technologies), Наносемантика, Alchemical Music Box, Максим Маслов (сооснователь Eltechs и автор шумящего сейчас поста "Легенды и мифы процессора Эльбрус в примерах") и ваш покорный слуга Юрий Панчул.

Примеры которые используются в этой части семинара работают со всеми версиями Quartus начиная с 13.0sp1. Желательно конечно использовать последнюю из бесплатных (Lite) версий, но текущая бесплатная версия Quartus Prime Lite Edition 20.1.1 не работает сразу после скачивания ни на текущей версии Windows 10, ни на текущей версии Linux Ubuntu 20.04 LTS. Для Windows у нее истекла дата сертификата драйвера, а для Linux она использует устаревшую библиотеку.

Обе проблемы можно решить: для Windows - c помощью скачивания patch, а для Linux - с помощью "sudo ln -sf /lib/x86_64-linux-gnu/libudev.so.1 /lib/x86_64-linux-gnu/libudev.so.0".

Для проверки, что ваша FPGA плата и установка Quartus работает, вы можете скачать минимальный пакет "before" по следующей ссылке:

ChipEXPO 2021 Digital Design School before package v2.0 https://bit.ly/chipexpo2021ddsbefore20

Прямая ссылка

В качестве инструкций можно использовать видео Сергея Иванца с прошлого года, но применять их для нового пакета, а также использовать новые версии Quartus для Linux и Windows.

Теперь насчет упражнений по распознаванию и генерации звуков на верилоге с помощью FPGA платы. Сначала мы думали использовать синтетический звук из телефона, но потом решили, что это неспортивно - нужен живой звук, на котором можно тренировать техническую смекалку, требуемую для решения задач на распознавание.

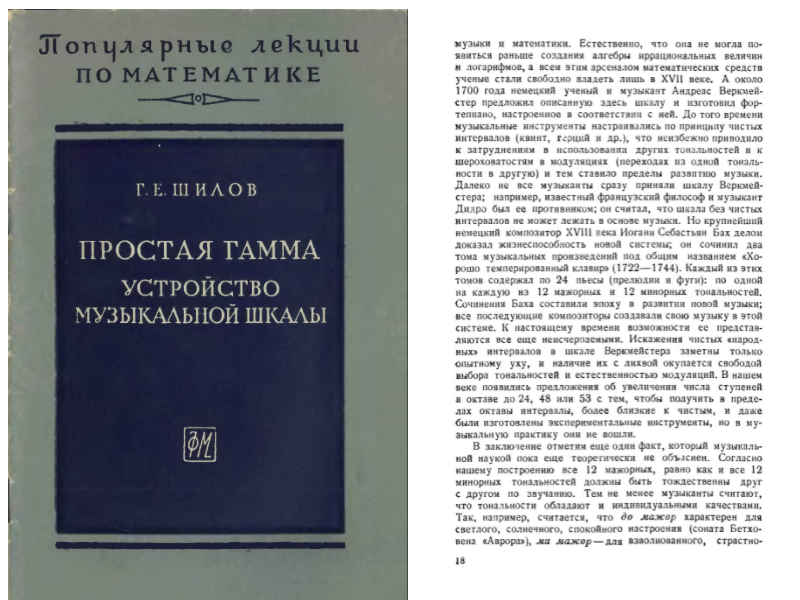

В процессе подготовки упражнений с музыкой на FPGA я узнал из советской книжки для детей 1963 года удивительный факт:

Оказывается, современные гаммы отличаются по частотам нот от гамм, которые были до Баха. В современных гаммах полутона находятся в геометрической прогрессии, на расстоянии корня 12-той степени из двойки друг от друга. А в 17 веке клавесины и арфы настраивали по другому, так, чтобы частоты образовывали кратные отношения (так называемый "чистый строй"). Из-за этого мелодии нельзя было транспонировать в другие тональности - они начинали звучать криво. Собственно именно Бах пропиарил новую систему в "Хорошо темперированном клавире" и доказал что с корнем 12-й степени из двойки сочинять можно. До этого эстеты лет 20 считали новую систему ("равномерно темперированный строй") немного варварской.

В упрямой России нововведение критиковали даже в 19 веке, согласно википедии: "Русский простолюдин с музыкальным дарованием, у которого ухо ещё не испорчено ни уличными шарманками, ни итальянскою оперою, поет весьма верно; и по собственному чутью берет интервал весьма отчетливо, разумеется, не в нашей уродливой темперированной гамме" Владимир Одоевский

Более реально чем теплый ламповый звук между прочим!

Каким образом FPGA плата может распознать какую-нюбудь простую мелодию, например из фильма "Крестный отец" (эта мелодия также звучит в советском мультфильме "Контакт")?

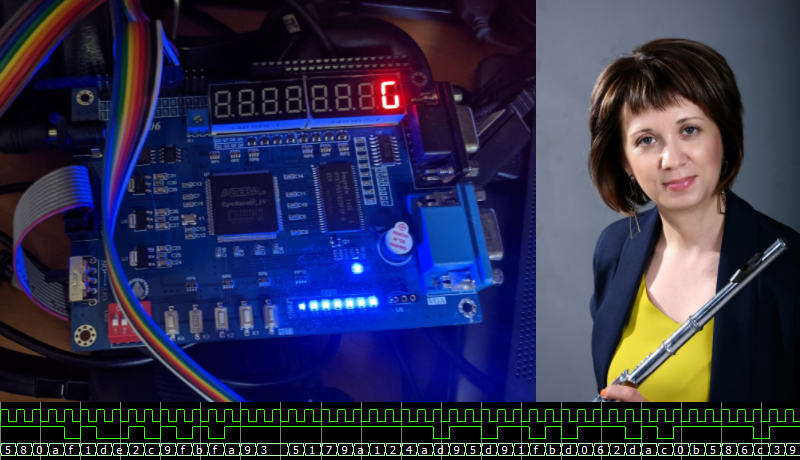

Если звук достаточно чистый, то можно распознать и без Фурье-преобразования, просто подсчетом тактов (но не музыкальных, а тактового сигнала 50 MHz на FPGA плате) между моментами, когда синусоида уровня сигнала пересекает его среднее значение. Этот метод называется zero crossing, и он вполне работает для звуков флейты. Флейту принесет преподавательница Мария Беличенко . Вот как zero-crossing выглядит на языке описания аппаратуры Verilog:

https://github.com/DigitalDesignSchool/ce2020labs/blob/master/day_2/piswords/lab_5_mic/top.v

reg [15:0] prev_value;

reg [19:0] counter;

reg [19:0] distance;

localparam [15:0] threshold = 16'h1000;

always @ (posedge clk or posedge reset)

if (reset)

begin

prev_value <= 16'h0;

counter <= 20'h0;

distance <= 20'h0;

end

else

begin

prev_value <= value;

if ( value > threshold

& prev_value < threshold)

begin

distance <= counter;

counter <= 20'h0;

end

else if (counter != ~ 20'h0) // To prevent overflow

begin

counter <= counter + 20'h1;

end

end

// Теперь в distance у нас лежит период нижней гармоники ноты

// выраженный в тактах 50-мегагерцового тактового сигнала

Уровень звукового сигнала снимается вот таким микрофоном, который мы выдадим:

Также с помощью вот такого усилителя можно сгенерировать звук. Если все хорошо отладить, то после распознавания мелодии ее можно продолжить из усилителя:

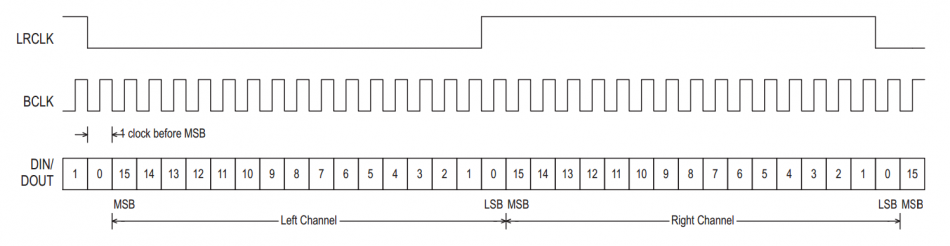

Микрофон передает уровень сигнала в FPGA с помощью протокола SPI, а усилитель использует протокол I2S.

Оба протокола реализуются простым сдвиговым регистром, см. код для I2S Виктора Прутьянова:

module i2s

(

input clk, // CLK - 50 MHz

input reset,

input [2:0] octave,

input [3:0] note,

output mclk, // MCLK - 12.5 MHz

output bclk, // BCLK - 3.125 MHz serial clock - for a 48 KHz Sample Rate

output lrclk, // LRCLK - 32-bit L, 32-bit R

output sdata

);

reg [9:0] clk_div;

reg [31:0] shift;

reg [7:0] cnt;

wire [15:0] value;

wire [7:0] cnt_max;

always @ (posedge clk or posedge reset)

if (reset)

clk_div <= 0;

else

clk_div <= clk_div + 10'b1;

assign mclk = clk_div [1];

assign bclk = clk_div [3];

assign lrclk = clk_div [9];

always @ (posedge clk or posedge reset)

if (reset)

cnt <= 0;

else if (clk_div [9:0] == 10'b11_1111_1111)

cnt <= (cnt == cnt_max) ? 8'b0 : cnt + 8'b1;

assign sdata = shift [31];

always @ (posedge clk or posedge reset)

if (reset)

shift <= 0;

else

begin

if (clk_div [8:0] == 9'b1_1111_1111)

shift <= value << 16;

else if (clk_div [3:0] == 4'b1111)

shift <= shift << 1;

end

lut lut

(

.octave ( octave ),

.note ( note ),

.x ( cnt ),

.x_max ( cnt_max ),

.y ( value )

);

endmoduleДля усилителя вам нужны будут наушники, а если хотите генерировать стерео звуки, то вот такой кабель:

Может вы сможете повторить сцену из мультфильма Контакт с помощью FPGA платы:

Кроме лаб со звуком, лаб с процессором schoolRISCV еще будут лабы с VGA играми. Они были очень популярны на школе в Зеленограде:

Для этих упражнений вам понадобится дополнительный монитор с VGA входом, чтобы воткнуть его в FPGA плату. Этих мониторов у нас дефицит, так как в Сколково будуь стоять только 25 моноблоков, которые нам организовал Евгений Певцов из МИРЭА. Если можете принести свой мониторчик, будет хорошо (если вы делаете упражнения удаленно, у вас наверняка есть старый монитор или вы можете одолжить).

Теперь зачем все это нужно. Упражнения с FPGA - это путь в проектирование на уровне регистровых передач. Он на уровне верилога и микроархитектуры более-менее общий и для FPGA и для ASIC - микросхем которые стоят в сматрфонах и других массовых устройствах. Причем работы в крутых компаниях есть и на FPGA, и для интернов. Это интересно и хорошо оплачивается. Причем и на школе для начинающих, и на школе для продолжающих (секции 2 и 3) у нас будут задачки по мотивам реальных вопросов на собеседованиях :-)

Автор: Юрий Панчул / Yuri Panchul