Ссылка на первую часть

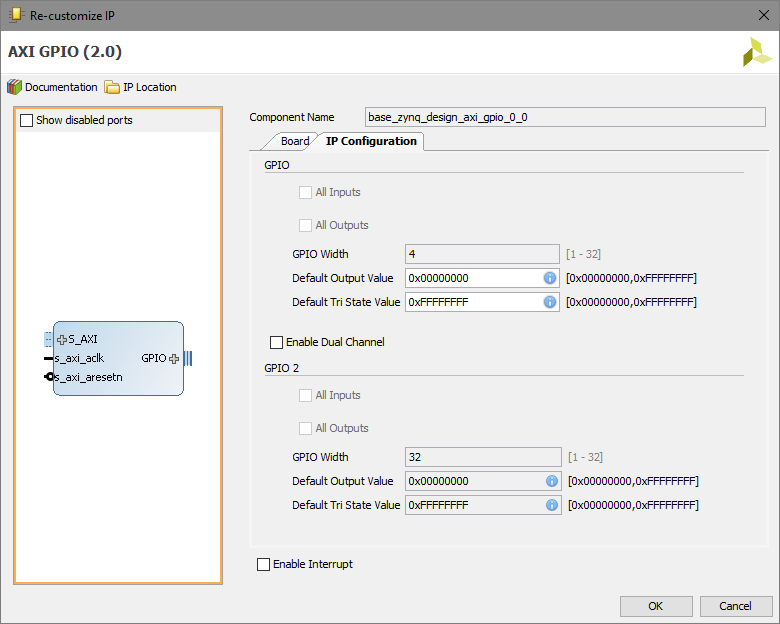

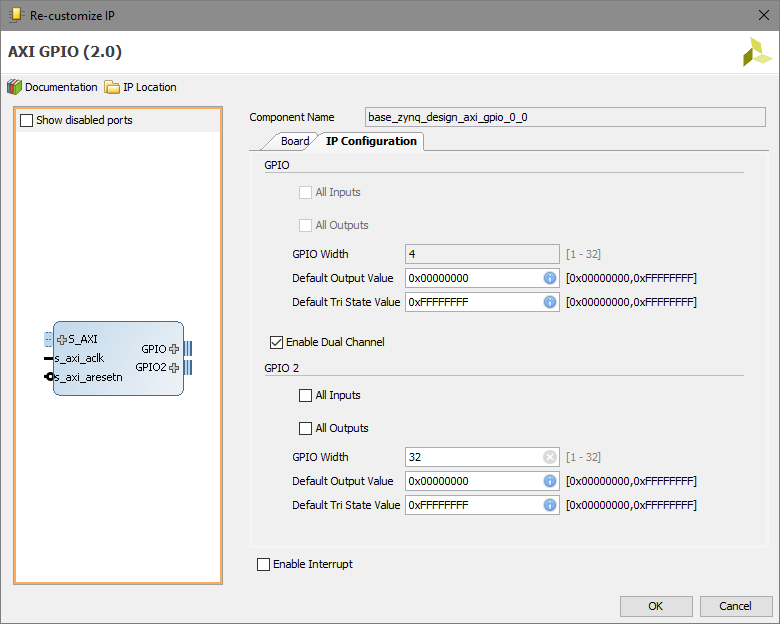

Если вы уже успели поработать с блочным дизайном в Vivado, то могли увидеть, что внешний вид многих стандартных IP изменяется в зависимости от настраиваемых параметров. Например, модуль AXI-GPIO может быть одноканальным или двухканальным в зависимости от параметра «Enable dual channel»:

|

|

Для проекта БК-0010 нам тоже будет удобно воспользоваться этой технологией и сегодня мы узнаем, как это сделать.

Также в этой части мы:

– Рассмотрим общие сведения об архитектуре БК-0010

– Поговорим об интерфейсах, о том, как их создавать и как с ними работать.

– Создадим несколько вспомогательных IP, внешний вид и характеристики которых меняются в зависимости от параметров.

Читать полностью »