Часть 1

Часть 2

Часть 3

Часть 4

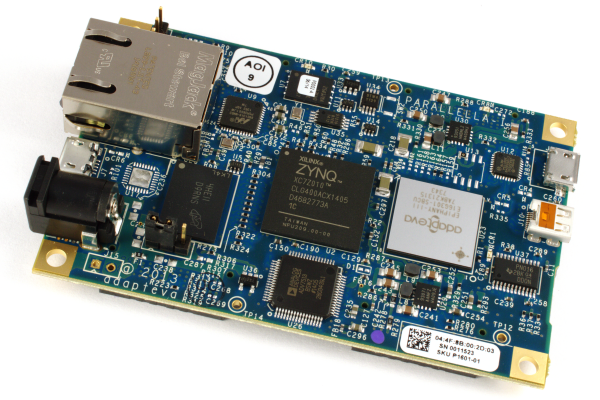

Parallella

компания/проект — Adapteva, Parallella.org

обзор LinuxGizmos

страница продукта

CPU — Xilinx Zynq-7020 или -7010 SoC (2x Cortex-A9 @ 667MHz plus FPGA); 16-core Epiphany RISC chip

Память — 1GB DDR3 RAM

Цена — $99

Плата предназначена для построения энергоэффективных серверных кластеров и исследований в области параллелизма, и построена на базе Zynq ARM/FPGA SoC работающего под управлением дистрибутива Ubuntu 15.04, названного Parabuntu, а также «доморощенного» 16-ядерного сопроцессора Epiphany. Порты включают microSD, GbE, micro-HDMI, и два USB. Четыре 60-pin разъёма служат для расширения ввода-вывода и связаны с FPGA и с чипом Epiphany. Adapteva также предлагает за $75 версию Micro-Server с Zynq-7010, у которой нет USB, HDMI, и расширений I/O. В прошлом году также был выпущен корпус Parallella Aluminum Case за $29.50 с теплорассеивающей пластиной, но сейчас его нет в продаже. Новый чип Epiphany-V, содержащий 4.5 млрд. транзисторов должен был выйти уже несколько месяцев назад.

Читать полностью »