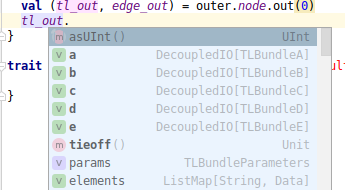

В предыдущей части мы собрали микроконтроллер вообще без оперативной памяти на базе ПЛИС Altera/Intel. Однако на плате есть разъём с установленным SO-DIMM DDR2 1Gb, который, очевидно, хочется использовать. Для этого нам потребуется обернуть DDR2-контроллер с интерфейсом

В предыдущей части мы собрали микроконтроллер вообще без оперативной памяти на базе ПЛИС Altera/Intel. Однако на плате есть разъём с установленным SO-DIMM DDR2 1Gb, который, очевидно, хочется использовать. Для этого нам потребуется обернуть DDR2-контроллер с интерфейсом ALTMEMPHY в модуль, понятный для протокола работы с памятью TileLink, используемого повсюду в RocketChip. Под катом — тактильная отладка, брутфорс программирование и ГРАБЛИ.

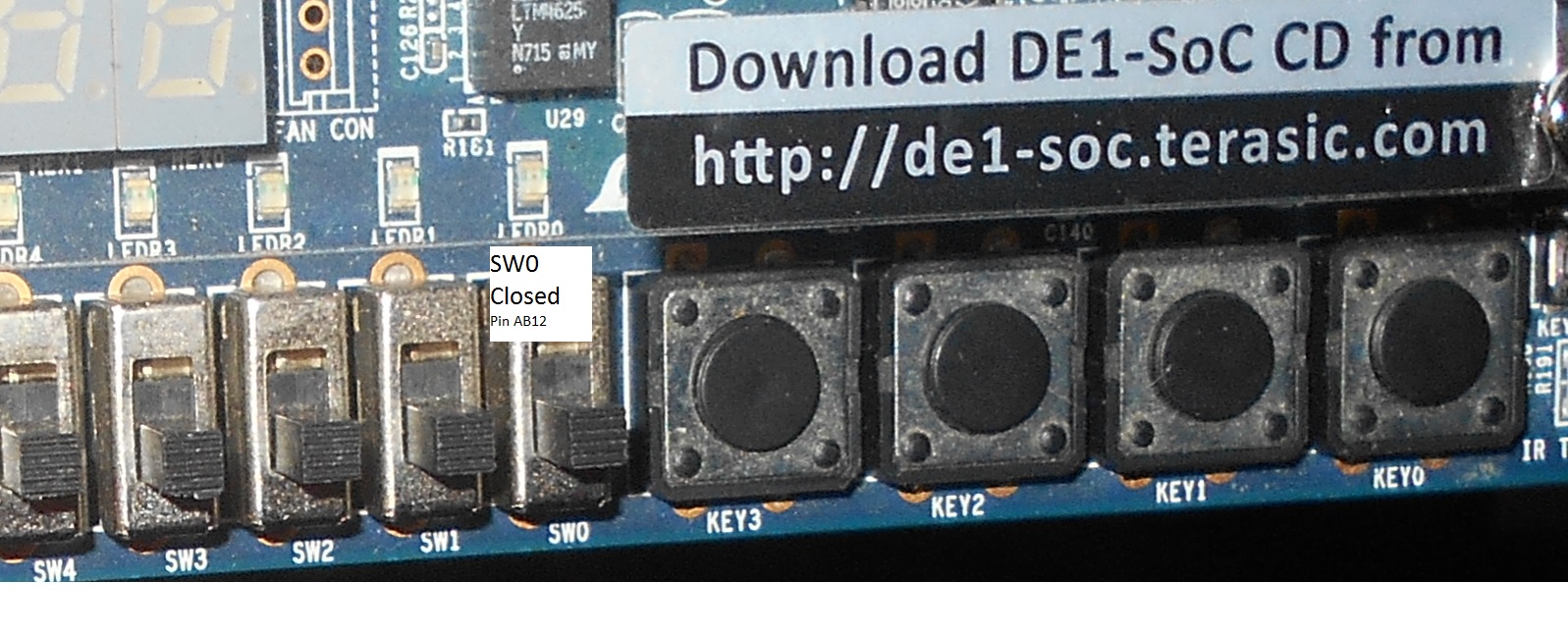

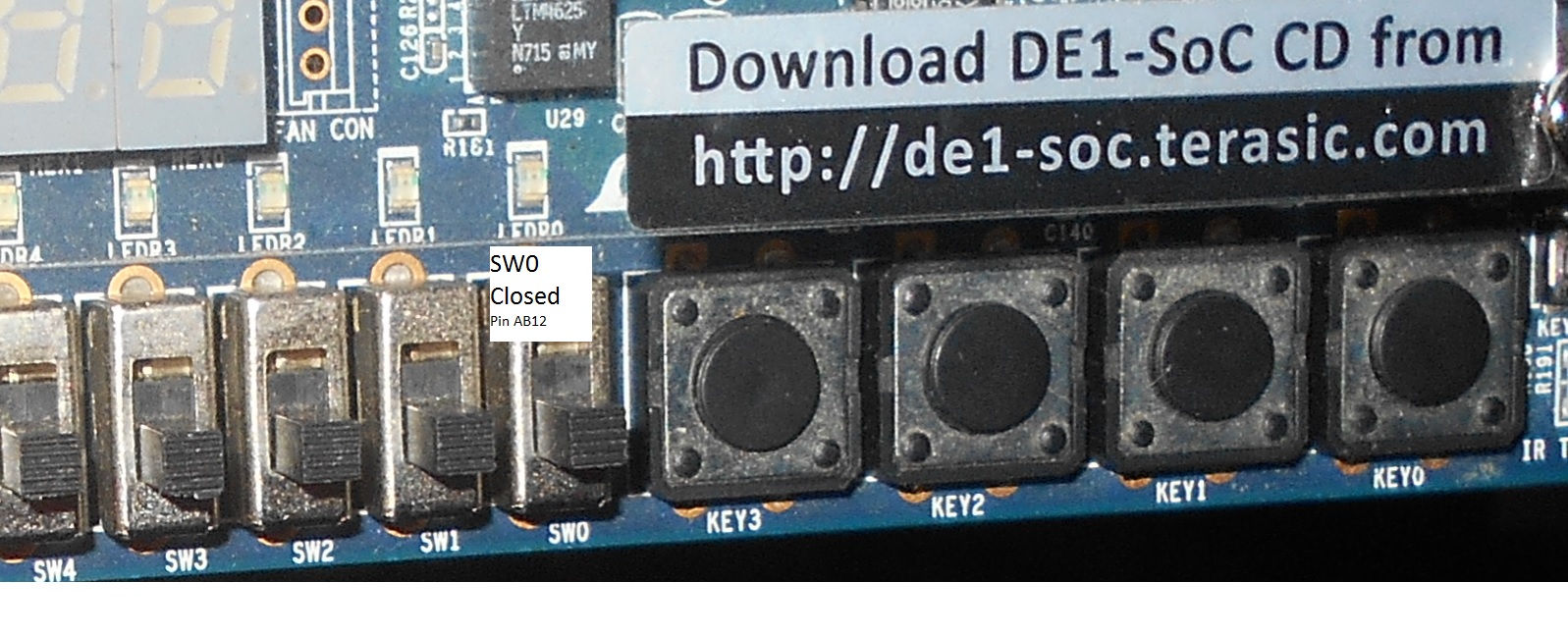

Как известно, в Computer Science есть две главные проблемы: инвалидация кешей и именование переменных. На КДПВ вы видите редкий момент — две главные проблемы CS встретили друг друга и что-то замышляют.