Перевод коллективной статьи Practical experiences based on MIPSfpga, не так давно представленной Сарой Харрис на симпозиуме в Торонто. Приводится подробное описание MIPSfpga 2.0, релиз которой состоялся 3 июля 2017 года. Основное, на мой взгляд, отличие по сравнению с версией 1.3: пакет лабораторных работ расширен набором, ориентированным на внутреннюю работу процессора. Так что, если вы хотите узнать, как работает современное ядро, то MIPSfpga 2.0 — это ваш выбор для качественного самообразования. Крайне полезной данная статья будет для преподавателей ВУЗов — подробно и с примерами рассматривается вопрос интеграции MIPSfpga 2.0 в учебный процесс, включая ее соответствие Методическим рекомендациям IEEE/ACM для программ бакалавриата в области вычислительной техники.

Рубрика «fpga» - 25

MIPSfpga – практический опыт

2017-08-17 в 16:56, admin, рубрики: C, fpga, mips, MIPS microAptiv UP, MIPSfpga, SoC, Verilog, Анализ и проектирование систем, образование, перевод, программирование микроконтроллеров, системное программированиеИсследование асинхронной схемы в ModelSim

2017-08-15 в 7:51, admin, рубрики: fpga, modelsim, Verilog, асинхронные схемы

Прочитал статью FPGA/Асинхронный дешифратор от ajrec.

Я сперва прочитал и ничего не понял, а потом прочитал еще раз и опять ничего не понял. На самом деле я прочитал уже все статьи ajrec про асинхронные схемы и должен констатировать, что мало понимаю, что это вообще такое (хотя считаю, что опыт проектирования в FPGA у меня есть).

В комментариях к статьям автор в основном получает минусы, народ посмеивается и кажется так же не понимает, как и я.

Честно говоря, я всегда с любопытством смотрю на проекты, которые «не такие, как все». Я считаю, что только такие проекты имеют шанс либо глубоко провалиться, либо высоко взлететь. Если делаешь что-то так же, как и сотни других разработчиков, то идешь проторенной дорогой, здесь легко и комфортно. Сделать шаг в сторону и пойти своей тропой могут далеко не все.

Я попробовал разобраться в проекте асинхронного дешифратора и по крайней мере сделать временную симуляцию кода в ModelSim. Далее о том, что из этого получилось.Читать полностью »

Асинхронный дешифратор

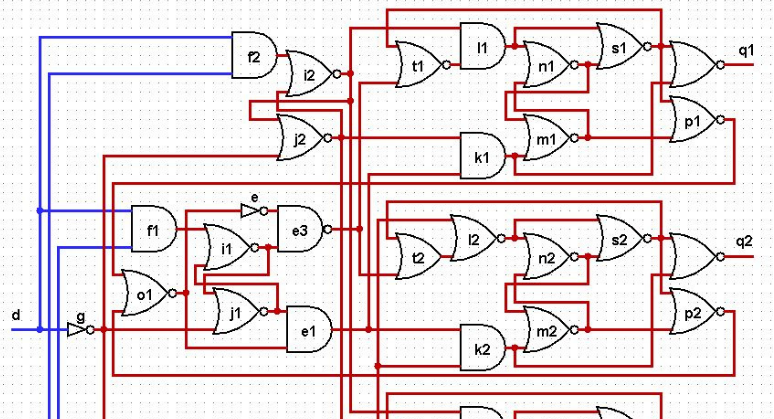

2017-08-08 в 13:22, admin, рубрики: fpga, асинхронные схемы, асинхронный дешифраторКак и обещал в предыдущей статье, речь в этой статье пойдет о представлении в асинхронном виде операций над адресами. В качестве примера опишу операцию дешифрации адреса. Сразу же хочу предупредить инсинуации, с которыми столкнулся после опубликования предыдущей статьи. Речь пойдет о целиком и полностью асинхронном устройстве. И прошу, не надо ссылаться на реферат узбекского университета. Якобы асинхронный дешифратор можно получить из синхронного с помощью нехитрых манипуляций. Заодно вопрос тем, кто утверждает, что асинхронный процессор произведен 20 лет назад. Как это удалось без асинхронного дешифратора?

Итак, об асинхронном дешифраторе. После размышлений я пришел к выводу, что единственный вменяемый путь синтеза асинхронного дешифратора это поэтапное удвоение разрядности адреса с помощью схемы надстройки над двумя дешифраторами вдвое меньшей разрядности. Доказать что альтернативного пути нет я не берусь. Но могу утверждать что альтернативный путь (если он есть) куда более затратен по количеству добавляемых новых сигналов.

Ввиду изложенного, речь в этой статье пойдет о двухразрядном дешифраторе. Как удвоить разрядность асинхронного дешифратора, тема следующей статьи.

Как мы создали устройство быстрой обработки потока событий на FPGA

2017-07-31 в 16:32, admin, рубрики: algorithmic trading, fpga, HFT-трейдинг, high performance, pre-trade, risk checks, стартапы; команда; опыт, я пиарюсьУстройство называется CEPappliance. CEP — от Complex Event Processing, а appliance — (и так должно быть понятно, но на всякий случай) “устройство” с английского.

Затеяли мы его в далеком 2010 году как хобби, трудясь над ним после основной работы долгими вечерами, плавно переходящими в короткие ночи, и по выходным дням. За 5 лет такой работы мы создали 3 прототипа в поисках решения с минимальными задержками и простой моделью программирования логики обработки данных.

В 2015 году мы осознали, что у нас получилось достойное творение, которое позволяет обрабатывать потоки данных с гарантированной задержкой в 2-3 микросекунды. И мы начали искать возможности превратить начатое в коммерческий продукт и, вероятно, перестать работать на “дядю”, заняться только нашим продуктом, посвящая ему все свое время. В конце 2015 мы нашли первого клиента, оставили “дядей” и пустились в “свободное плавание”.

Сегодня мы можем точно сказать, что устройство у нас получилось. Мы еще не реализовали всего задуманного и нам по-прежнему приходится много работать, чтобы добавлять новый функционал, иногда исправлять ошибки. Но наше устройство уже год работает в промышленной эксплуатации.

Читать полностью »

Опыт использования FPGA платы DE10-Standard и DMA PL330

2017-07-26 в 8:07, admin, рубрики: Cyclone V, DMA, fpga, HPS, kernel, linux, SoC

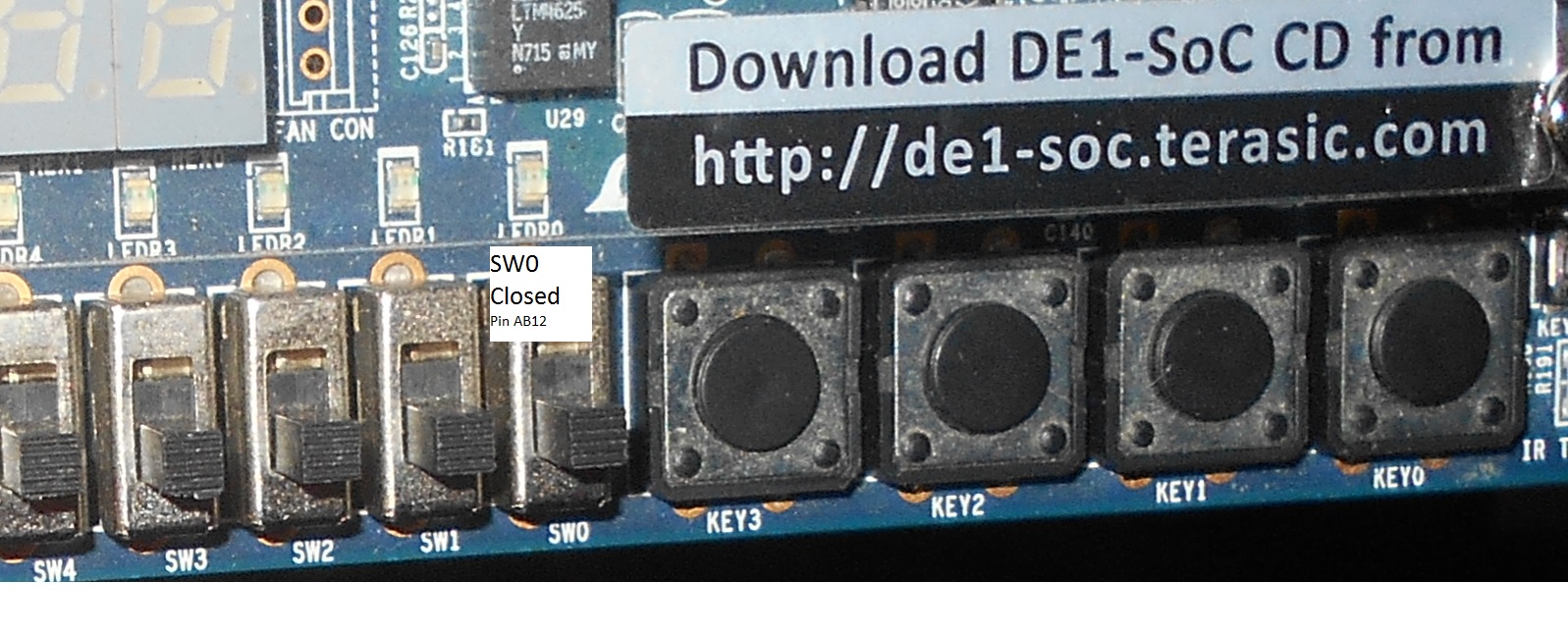

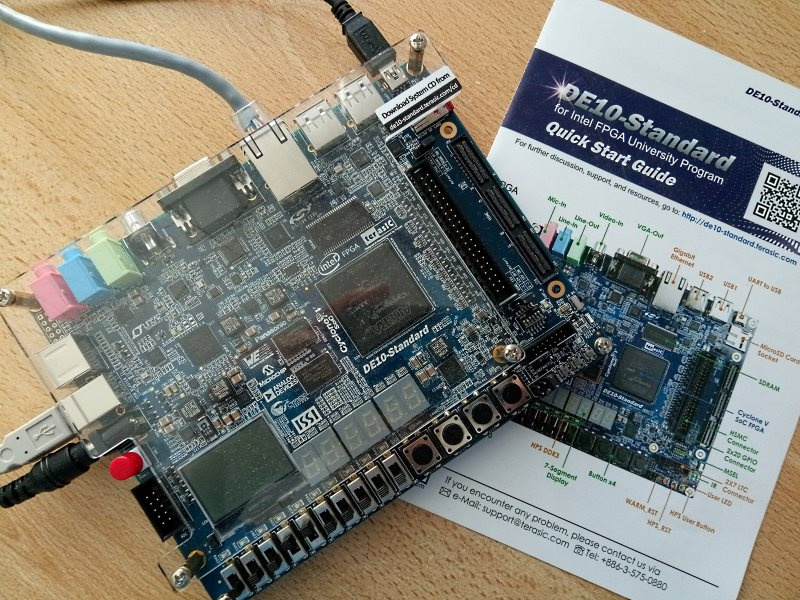

Получил в свое распоряжение плату Terasic DE10-Standard. На ней много всего интересного: встроенный JTAG программатор, светодиоды, переключатели, кнопки, разъемы Audio / VGA / USB / Ethernet. Думаю, что нет особой необходимости перечислять все ее возможности, ведь каждый желающий может прочитать спецификацию платы на сайте производителя.

Для меня важно, что на плате стоит FPGA чип Cyclone V SX – 5CSXFC6D6F31C6N. Эта микросхема содержит два процессора ARM Cortex-A9 и 110K логических элементов FPGA. Это уже настоящая SoC HPS: System-On-Chip, Hard Processor System. С такими ресурсами можно пробовать делать довольно сложные проекты. Далее расскажу о своем опыте использования платы.Читать полностью »

Возможен ли асинхронный процессор

2017-07-24 в 17:56, admin, рубрики: fpga, асинхронные схемы, асинхронный процессорЦитата из комментариев к предыдущей статье: «Вот, к сожалению, данные, адреса и любые операции над ними не годятся для графового представления. Если придумаете как это сделать — будет революция. А без данных, адресов и арифметики, лучшее что можно сделать асинхронным (с помощью графового метода) — машину Тьюринга. Но никак не процессор, к примеру. Поэтому тематика и заброшена, уже 20 лет как.» В компетенции автора сомневаться не приходится, все-таки доктор наук. А я вот попробую сделать революцию.

Как видно из цитаты проблема состоит из двух частей: операции над данными и операции над адресами. С адресами разберусь в следующей статье, а сейчас — данные.

Для примера попробую сделать схему разряда регистра, выполняющего две операции. Почему две? Потому что две, три операции или десять — принципиальной разницы нет. От увеличения количества операций увеличивается только объем вычислений при синтезе схемы. Главное, чтобы таких операций было более одной. В качестве операций выберу копирование из буфера и сложение с содержимым другого регистра.

Читать полностью »

Поднимаем Linux на MIPSfpga и ПЛИС Altera

2017-07-22 в 21:56, admin, рубрики: C, fpga, mips, MIPS microAptiv UP, MIPSfpga, SoC, Verilog, Анализ и проектирование систем, программирование микроконтроллеров, системное программирование

Предоставленная Imagination Technologies документация на MIPSfpga очень хорошо и подробно описывает развертывание Linux. Но используемая при этом система на кристалле построена с помощью Xilinx-специфических периферийных модулей. Потому ее повторение на отладочной плате с ПЛИС Altera в исходном виде представляется невозможным. Решением является система на кристалле MIPSfpga-plus с ее платформонезависимой периферией. О том, как запустить на ней Linux, читайте в этой статье.

Текущая активность вокруг MIPSfpga и не только

2017-07-19 в 17:27, admin, рубрики: C, fpga, mips, MIPS microAptiv UP, MIPSfpga, SoC, Verilog, Анализ и проектирование систем, программирование микроконтроллеров, системное программирование

Есть несколько событий и тем, которыми хотелось бы поделиться с сообществом. По-хорошему, по каждой можно писать отдельную статью, но общий дефицит времени заставляет немного схалтурить. Наши сегодняшние темы:

- релиз MIPSfpga 2.0;

- процессор schoolMIPS и Летняя школа юных программистов в Новосибирске;

- школа-семинар по цифровому дизайну и компьютерной архитектуре в Томске;

- запуск ванильного ядра Linux на MIPSfpga-plus;

- поддержка АЦП Altera MAX10 в MIPSfpga-plus;

- логотип MIPSfpga-plus.

Если тематика MIPSfpga-plus вам не безразлична, то в конце есть небольшой опрос на тему чего мне писать (или не писать) следующую статью. Ваш выбор поможет мне сориентироваться и расставить приоритеты. Welcome!

Гибридный куб памяти (HMC): что это такое и как его подключить к FPGA

2017-07-18 в 13:12, admin, рубрики: FLIT, fpga, GTX, HMC, IT-стандарты, micron, SSI, Xilinx Virtex, Анализ и проектирование систем, высокая производительность, память, разработка железа, разработка электроники

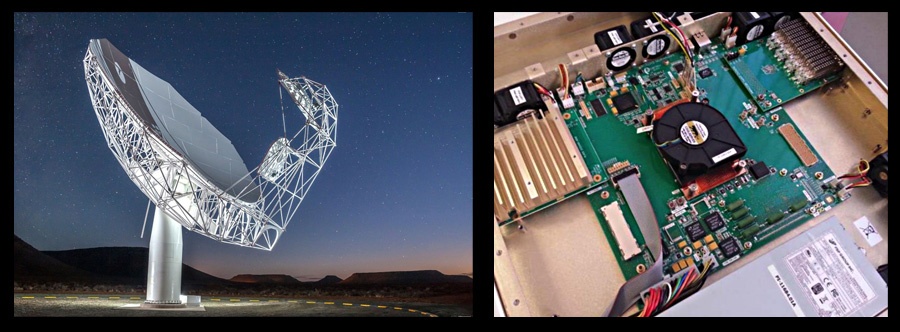

На фото: Платформа SKARAB для цифровой обработки данных с телескопа MeerKAT. За счет технологии HMC каждая из 64 антенн телескопа может передать на платформу поток данных со скоростью 40 Гбит/с

В ожидании нового стандарта памяти DDR5 SDRAM, который появится уже в следующем году, мы исследуем альтернативные технологии. В этой статье изучим память HMC (Hybrid Memory Cube), которая обеспечивает 15-кратный рост производительности при 70% экономии на энергопотреблении на бит по сравнению с DDR3 DRAM.

В то время как DDR4 и DDR5 представляют собой эволюцию стандарта, HMC — это революционная технология, которая может изменить рынок не только в сфере специализированных высокопроизводительных вычислений, но также в области потребительской электроники, такой как планшеты и графические карты, где важен форм-фактор, энергоэффективность и пропускная способность.

Читать полностью »