В прошлой публикации я упомянул, что мой SBC для экспериментов пал смертью храбрых. Само собою, встала проблема нового подопытного.

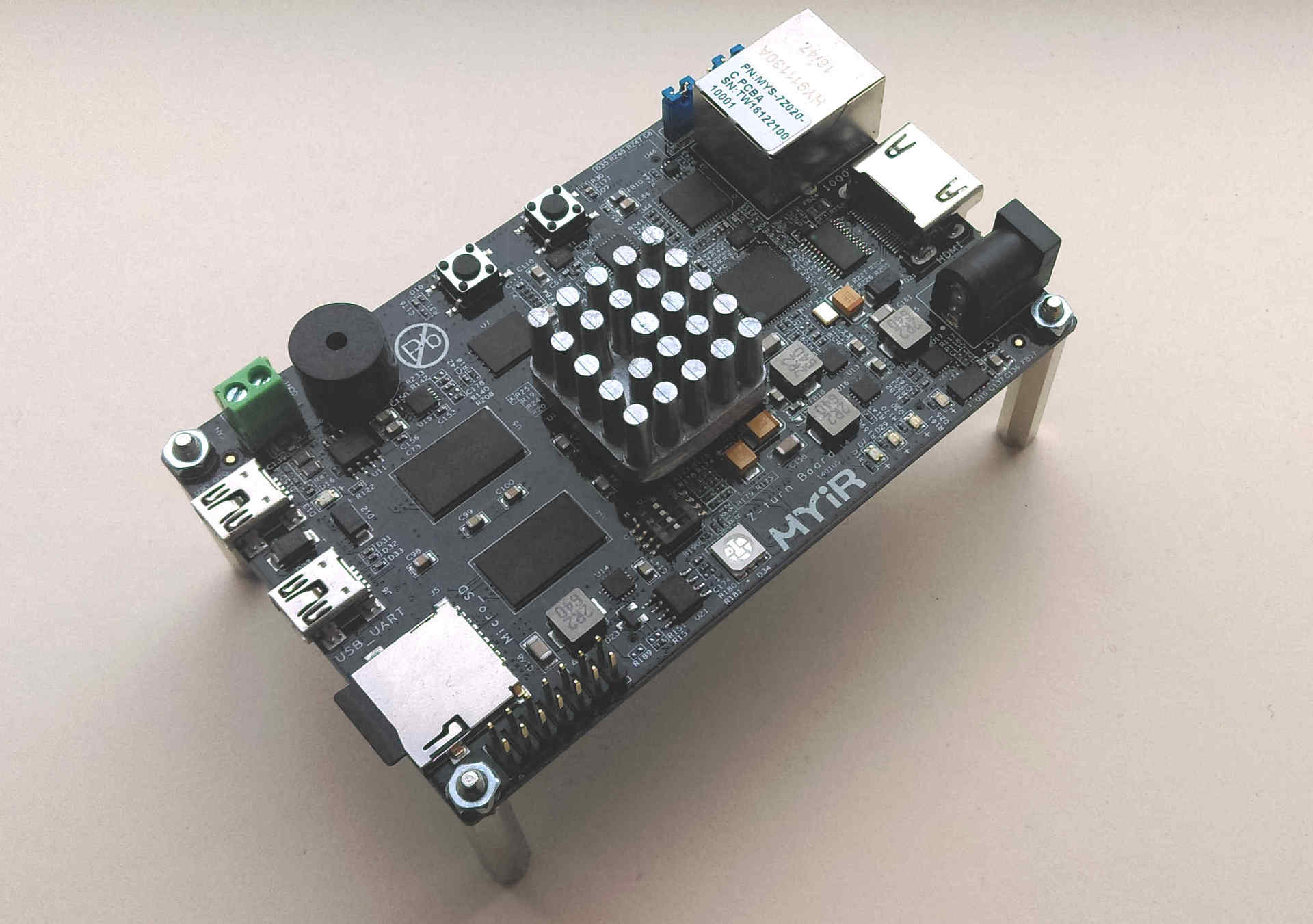

Простой одноплатник мне как-то не хотелось приобретать, поэтому выбор мой пал на SoC'и. Выбирал я между Zynq и Cyclone V. По названию темы, думаю, догадались, что же я решил выбрать.

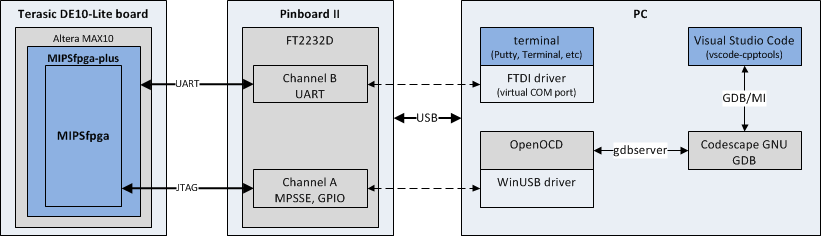

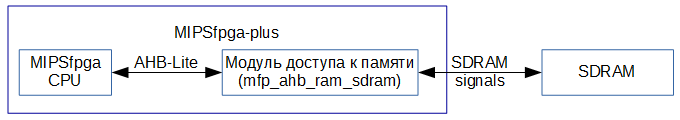

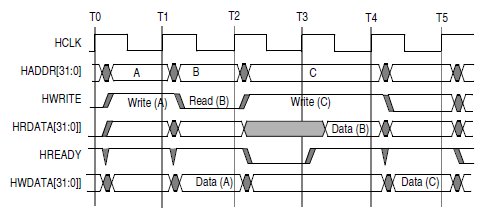

Данная публикация будет состоять из небольшого обзора платки с заглавной картинки и того, как «программировать» и «конфигурировать» подобное железо.

Кому это интересно прошу под кат.Читать полностью »