Реализация связки прошивки ПЛИС, ПО микроконтроллера NIOS и управляющего ПО под Linux на базе Altera Cyclone V SoC с использованием Avalon Mailbox для создания на их основе распределенной системы управления.

Читать полностью »

Рубрика «fpga» - 22

Распределённая система управления на базе SoC FPGA

2018-04-17 в 16:26, admin, рубрики: fpga, linux, SoC, системное программированиеРешение FizzBuzz на FPGA с генерацией видео

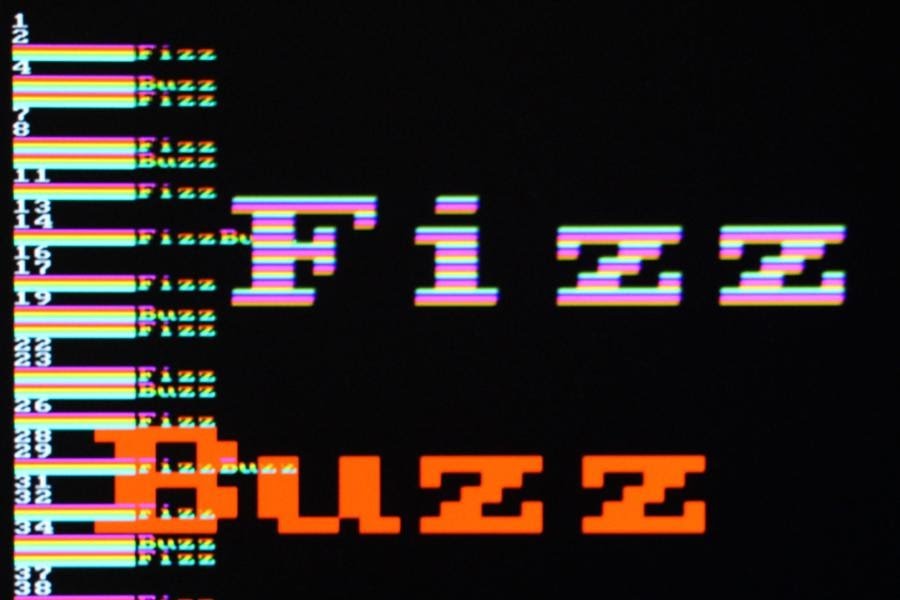

2018-04-13 в 11:24, admin, рубрики: fizzbuzz, fpga, Mojo, Spartan 6, Verilog, VGA, видео, Мониторы и ТВ, ПрограммированиеЭта статья рассказывает, как сгенерировать видеосигнал на FPGA, используя в качестве примера игру FizzBuzz. Генерировать видео оказалась проще, чем я ожидал — проще, чем предыдущая задача с последовательным выводом FizzBuzz на FPGA. Я немного увлёкся проектом, поэтому добавил анимацию, разноцветный текст и гигантские прыгающие слова на экране.

FizzBuzz на плате FPGA. Плата генерирует прямой видеосигнал VGA с анимацией слов “Fizz” и “Buzz”

Если Вы не знакомы с задачей FizzBuzz, то она заключается в написании программы, которая печатает числа от 1 до 100, где кратные трём заменяются словом Fizz, кратные пяти — словом Buzz, а кратные пятнадцати — FizzBuzz. Поскольку FizzBuzz реализуется в нескольких строчках кода, эту задачу дают на собеседованиях, чтобы отсеять совсем не умеющих программировать. Но на FPGA решение гораздо сложнее.

Читать полностью »

Генерация и тестирование ядра RISC-V

2018-04-10 в 14:48, admin, рубрики: fpga, open source, parallella, risc-v, zynq, Тестирование IT-системКак я писал в прошлом посте, название моего проекта на GSoC-2016 — «порт RISC-V на Parallella», и первая вещь, которую я должен был сделать, это познакомиться с экосистемой RISC-V. Один из лучших способов это сделать, — посмотреть видео с презентации первого воркшопа RISC-V на Youtube. Для того, чтобы понять самые важные концепции, я рекомендую следующие презентации:

- Введение (Krste Asanović) видео слайды

- Тулчейн RISC-V (Andrew Waterman) видео слайды

- SoC-генератор RISC-V “Rocket Chip” в Chisel (Yunsup Lee) видео слайды

- Структура программного стека RISC-V (Sagar Karandikar) видео слайды

- Отладка на RISC-V (Albert Ou) видео слайды

- Портирование нового кода на RISC-V с OpenEmbedded (Martin Maas) видео слайды

- Окружение тестирования RISC-V (Stephen Twigg) видео слайды

Ещё одна ссылка, если вы интересуетесь Chisel, языком, основанным на Scala, который используется для описания текущей аппаратной реализации ядра RISC-V (ядро Rocket имеет in-order конвейер, BOOM — out-of-order), и любых будущих реализаций.

Краткое руководство по Chisel (Jonathan Bachrach) видео слайды

Работа с Rocket Chip, добавление расширений, инфраструктура ASIC и FPGA (Colin Schmidt) видео слайды

Если вы глубоко заинтересованы в RISC-V и развитии сообщества, я предлагаю вам принять участие в воркшопах.

ECO Flow в Vivado или работа в режиме редактирования нетлиста

2018-04-07 в 17:35, admin, рубрики: fpgaАннотация

В статье рассмотрен режим работы Vivado, позволяющий вносить изменения в проект на уровне редактирования списка соединений (в дальнейшем – нетлиста). Описаны как сам режим ECO, так и некоторые нюансы, которые появляются во время работы в нём. Приведён демонстрационный пример и описана полная последовательность действий для получения результата, в работоспособности которой может убедиться каждый желающий. Статья будет полезна для «общего развития» FPGA-разработчикам, а особенно — тем, кто часто отлаживает проекты в Logic Analyzer. Надеюсь, работа в этом режиме вызовет интерес у разработчиков, работающих с большими кристаллами, время компиляции в которых может достигать часов (а то и десятков часов), поскольку в этом режиме время, затрачиваемое на имплементацию, при внесении изменений в нетлист может сократиться до буквально пары минут.

Оглавление

- Аннотация

- Введение

- 1. ECO: краткий обзор

- 2. Design Сheckpoint

- 3. Разработка тестового проекта

- 3.1. Создание проекта

- 3.2. Создание и добавление HDL файлов в проект

- 3.3.Создание проекта MicroBlaze и работа в IP Integrator

- 3.4.Синтез и имплементация

- 3.5.Написание программы для MicroBlaze

- 3.6.Запуск программы и отладка

- 4. Переход в режим ECO

- 5. ECO: описание интерфейса

- 6. Внесение изменений в проект

- 6.1. Создание новых элементов в нетлисте

- 6.2. Изменение свойств/параметров компонентов

- 6.3. Подключение других цепей к пробникам и ILA

- 6.4. Замена портов ввода/вывода

- 7. Сравнительный анализ

- 8. Заключение

- 9. Домашнее задание

- Библиографический список

Использование произвольных DataFlash 25-й серии вместо дорогих конфигураторов FPGA Altera без дополнительной аппаратуры

2018-04-03 в 8:01, admin, рубрики: fpga, ПЛИСИз любого описания на FPGA известно, что для хранения их конфигураций используются специальные микросхемы – конфигураторы. Например, для Altera Cyclone используются микросхемы EPCS. Вот схема от типичной макетной платы с кристаллом семейства Cyclone IV. На ней мы видим конфигуратор EPCS16. Всё бы ничего, но традиционно эти конфигураторы достаточно дороги, поэтому хотелось бы использовать что-нибудь подешевле.

Подробности в длиннющем тексте ниже. Если же очень интересно, но лень читать так много букв, то можно упростить задачу, посмотрев подробное 20-минутное видео.

Преобразователи Time-To-Digital (TDC): что это такое и как они реализованы в FPGA

2018-03-29 в 11:11, admin, рубрики: Altera, asic, fpga, FPGA Cyclone IV, intel, IT-стандарты, TDC, Verilog, Анализ и проектирование систем, времяизмерительная система, ПЛИС, Программирование, Промышленное программирование, разработка электроники

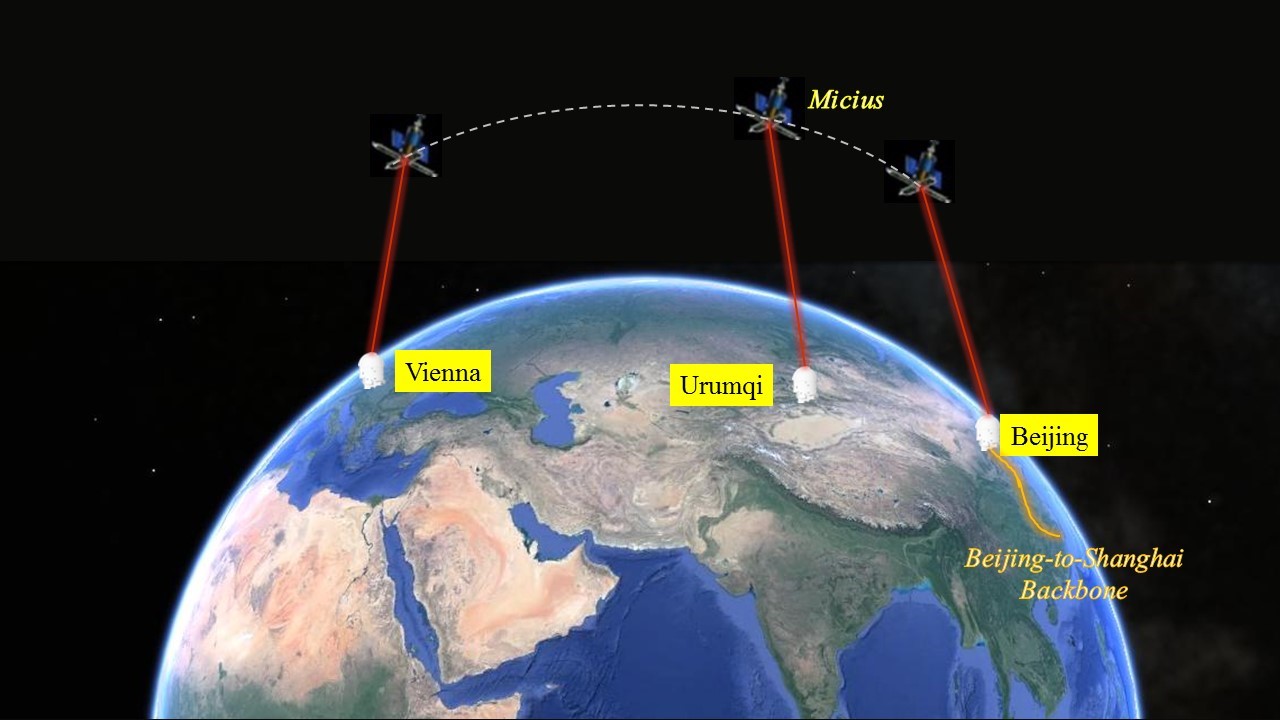

На рисунке — первый в мире спутник квантовой связи «Мо-Цзы», который запустили из Китая в 2016 году, в нем летает TDC, реализованная в FPGA.

Объяснить своей девушке (или парню), что такое ADC и DAC, и в каких домашних приборах они используются, может каждый человек, называющий себя инженером. А вот что такое TDC, и почему у нас дома их нет, зачастую можно узнать только после свадьбы.

TDC — это time-to-digital converter. По-русски говоря: времяизмерительная система.

Основные потребители быстродействующих TDC — научные группы. Как правило, под определенный исследовательский проект требуется что-то очень специфическое. То каналов надо много, то разрешение очень высокое, то исполнение компактное. А уровень развития современных FPGA и их доступность как раз дают исследователям возможность экспериментировать с реализациями и подстраивать их под собственные нужды.

В этой хабрастатье приводится детальное описание простенькой времяизмерительной системы на FPGA Cyclone IV. Статья будет полезна не только для расширения кругозора, но и с методической точки зрения, поскольку реализация системы нетривиальная.

Читать полностью »

FPGA-ускорители уходят в облака

2018-03-28 в 8:21, admin, рубрики: fpga, FPGA Altera, fpga дизайн, fpga/asic, Блог компании Селектел, высокая производительность, высокопроизводительные вычисления, Облачные вычисления

Появление на рынке FPGA-ускорителей, которые можно перепрограммировать сколь угодное число раз, причем на языке высокого уровня типа "С", стало настоящим прорывом в нише высокопроизводительных вычислений. Но не меньшим прорывом стала возможность использовать технологию FPGA, не покупая эти весьма дорогостоящие адаптеры (цена в России от 250 тыс.руб.), — а просто арендуя выделенный сервер с ускорителем в облаке провайдера.

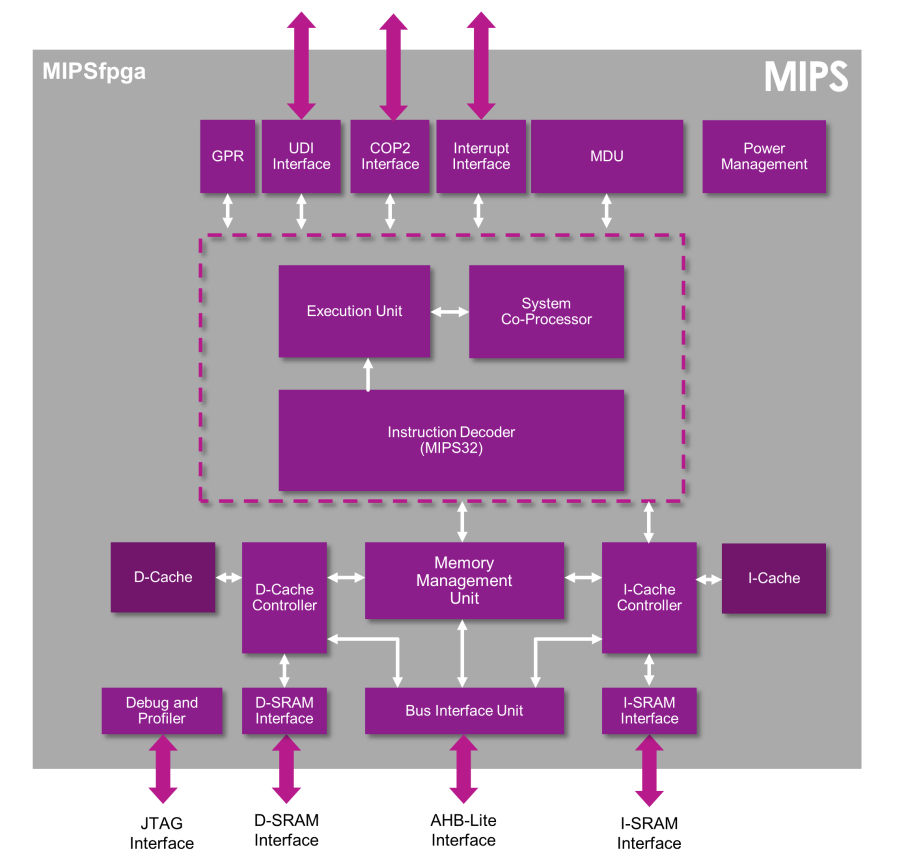

О портировании проекта MIPSfpga

2018-03-20 в 19:57, admin, рубрики: Altera, fpga, MIPSfpga, Quartus, virtual LEDs, Анализ и проектирование систем, Марсоход3, отладка, программирование микроконтроллеров

Перенос программного обеспечения с одной компьютерной архитектуры на другую в принципе, с некоторыми оговорками, дело относительно простое. Здесь на помощь приходят такие общеизвестные инструменты, как autoconf / automake/ libtool / gnulib. Собрать программу из исходников на каком нибудь Raspberry/ARM бывает так же просто, как и на ПК с Ubuntu/x86-64.

А вот как заставить проект ПЛИС разработанный для одной платы работать на другой плате? Там и сама ПЛИС может быть другой и на плате совершенно другие компоненты могут стоять. Простой перекомпиляцией проекта не обойтись.

Расскажу о своем опыте портирования проекта MIPSfpga для платы Марсоход3 с ПЛИС MAX10 Intel. Статьи о проекте MIPSfpga неоднократно появлялись на хабре. Они были так интересны, что мне захотелось и самому попробовать этот проект в имеющейся у меня плате. В своей работе я опирался на хабровские статьи

И многие другие…

Итак, что нужно сделать, чтобы портировать проект ПЛИС на другую плату?Читать полностью »

Реализация FizzBuzz на FPGA

2018-03-17 в 12:44, admin, рубрики: 8N1, Elbert 2, fizzbuzz, fpga, Mojo, Papilo One, Spartan 6, Verilog, конечный автомат, матричный переключатель, Программирование, Производство и разработка электроники, уровень регистровых передач, что после Arduino, Электроника для начинающихНедавно я увлёкся программированием FPGA и решил, что будет интересно реализовать на FPGA алгоритм игры FizzBuzz. FPGA (программируемая пользователем вентильная матрица) — интересная микросхема. Она программируется на выполнение произвольной цифровой логики. Можно сконструировать сложную схему, не прокладывая физические каналы между отдельными вентилями и триггерами. Микросхема способна превратиться во что угодно, от логического анализатора до микропроцессора и видеогенератора.

Тест FizzBuzz — написать программку, которая выдаёт числа от 1 до 100, где кратные трём заменяются словом “Fizz”, кратные пяти — словом “Buzz”, а кратные пятнадцати — “FizzBuzz”. Поскольку такая программа реализуется в нескольких строчках кода, то её часто задают на собеседованиях чтобы отсеять тех, кто вообще не умеет программировать.

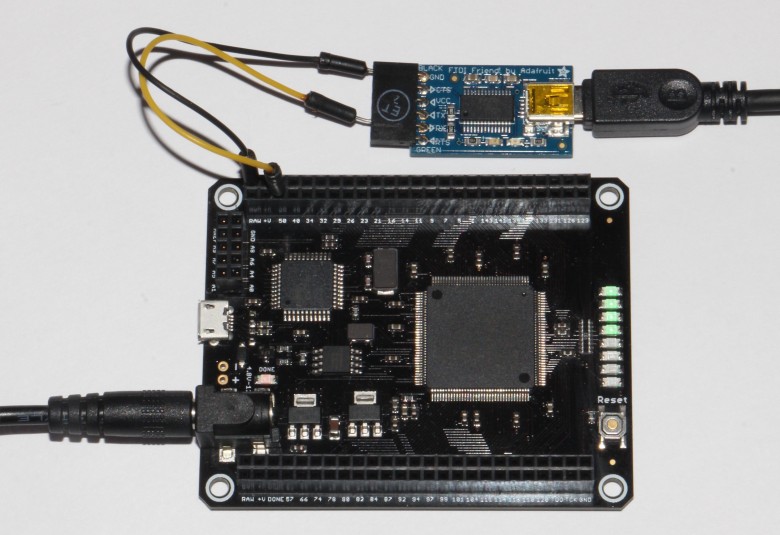

Плата Mojo FPGA, подключенная к порту serial-to-USB. Большой чип на плате — это Spartan 6 FPGA

Реализация FizzBuzz в цифровой логике, а не в коде, довольно бессмысленна, но показалась мне хорошим примером для обучения.1 Для этого проекта я использовал простую плату разработки Mojo V3 FPGA для начинающих. На ней установлен FPGA семейства Xilinx Spartan 6. Это один из самых маленьких FPGA, но у него 9000 логических ячеек и 11 000 триггеров — так что малыш на многое способен.

Читать полностью »

Как я blakecoin майнер делал

2018-03-13 в 18:42, admin, рубрики: blakecoin, C, cgminer, fpga, беда-беда, высокая производительность, криптовалюта, криптография, майнер, печаль

Не знаю кому как, а меня прошедший 2017 год шокировал стремительным взлетом биткоина. Сейчас, конечно, ажиотаж уже ушел, а в 17-м году про криптовалюты говорили и писали все кому не лень.

Я видел, что люди пытаются зарабатывать на криптовалютах. Кто как умеет. Кто-то на все сбережения скупал видеокарты и начинал самостоятельно майнить в гараже. Кто-то вкладывался в облачный майнинг. Кто-то пытается организовать свой пул. Кто-то запустил в производство шоколадные биткоины, а кто-то выпускает минеральную воду:

Я тоже стал изучать, что же такое эти самые биткоины. Когда-то я даже начал свое собственное иследование алгоритма SHA256 и написал статью здесь на хабре "Можно ли вычислять биткоины быстрее, проще или легче?". Мои исследования алгоритмов хеширования до сих пор продолжаются и еще и близко не завершены… Может быть когда нибудь напишу про это отдельную статью. А сейчас пока вот это..Читать полностью »