Борис Цирлин и Александр Кушнеров

30.10.2019

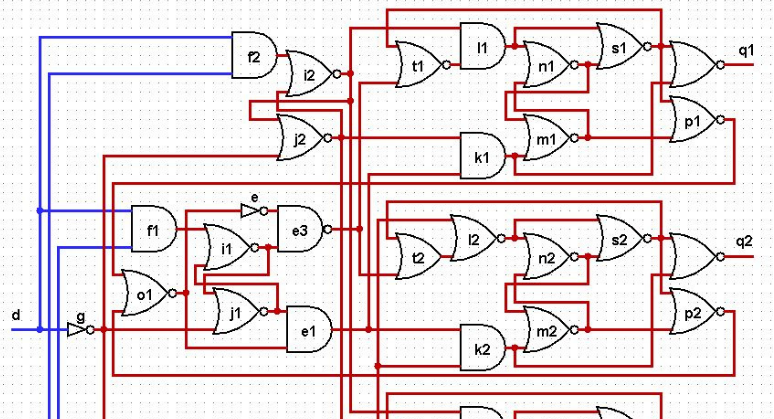

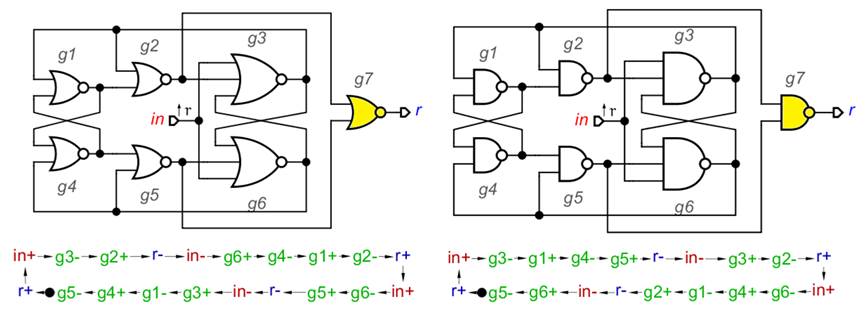

Для опытного разработчика схем не составляет большого труда узнать знакомую схему, в каком бы виде она не была нарисована. В этой статье мы покажем, что две транзисторные схемы из патентов являются вариантом асинхронного счётного триггера (АСТ). По сравнению со стандартной схемой, в схемах из патентов отсутствуют некоторые транзисторы. Это может рассматриваться как неисправность. Мы покажем, что, если такая же неисправность возникает в стандартной схеме, она продолжает работать правильно. АСТ, реализованный только на элементах ИЛИ-НЕ [1] или только на элементах И-НЕ известен как гарвардский триггер. Оба варианта схем показаны на Рис. 1, где g7 – это индикатор завершения переходных процессов. В дальнейшем мы его рассматривать не будем. На Рис. 1 показаны также графы сигнальных переходов (STG) [2] построенные в Workcraft [3].

Рис. 1. Асинхронный счётный триггер (АСТ) и его STG.

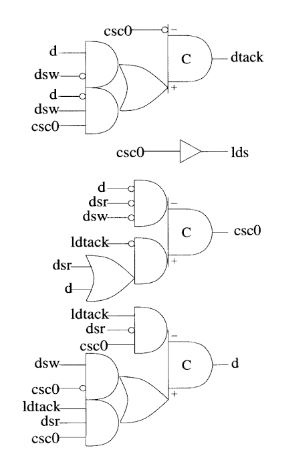

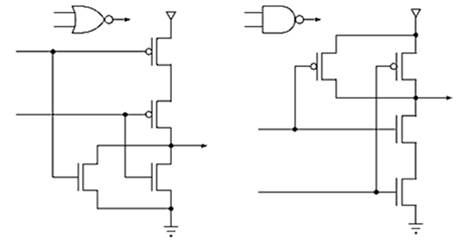

Обратим внимание, что в обоих вариантах АСТ есть три пары элементов (g1, g2), (g4, g5) и (g3, g6), которые имеют общий вход. Транзисторные схемы элементов 2И-НЕ и 2ИЛИ-НЕ показаны на Рис. 2. Трёхвходовые элементы устроены аналогично и содержат 6 транзисторов.

Рис. 2. Транзисторные схемы элементов 2И-НЕ и 2ИЛИ-НЕ.

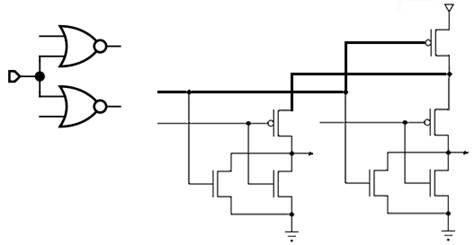

Возьмём два элемента 2ИЛИ-НЕ и выберем у каждого вход, где p-MOS транзистор подключён к Uпит. Соединим эти входы вместе и подключим к земле (лог. 0). Оба транзистора откроются и напряжение на их стоках будет равным Uпит. Достаточно ли этого чтобы безопасно соединить стоки и заменить два транзистора на один, как показано на Рис. 3? Нет. Нужно проверить что произойдёт если на общий вход подать лог. 1. Выходы обоих элементов соединятся с землёй, и мы будем иметь мостиковую схему из четырёх p-MOS транзисторов. Для оставшихся двух входов имеем четыре комбинации 0 и 1. Легко показать, что ни в одной из них не возникает короткого замыкания между Uпит и землёй.

Рис. 3. Два элемента 2ИЛИ-НЕ, имеющие общий вход.