На этой неделе я закончил работу по добавлению поддержки SDRAM в проект MIPSfpga-plus. Теперь при работе с MIPSFpga помимо блочной памяти, ограниченной ресурсами ПЛИС, доступно еще и внешнее ОЗУ.

Данная статья состоит из 2 частей:

Часть 1. Краткое описание модуля доступа к SDRAM. Пример использования.

Часть 2. Подробное описание работы с памятью, достаточное для того, чтобы в работе модуля смог разобраться человек, ранее не имевший дела с микросхемами ОЗУ. Список литературы.

Предполагается, что читатель как минимум:

- знаком с предметной областью в объеме учебника Харрис-энд-Харрис [1];

- имеет опыт программирования на C, ассемблере, использования gcc;

- имеет минимальный опыт работы с MIPSfpga. Не имея такого опыта, будет логичным начать с более простых вещей, и лишь затем думать о том, как использовать ОЗУ в своей системе.

Если вы уже опытный разработчик, то Часть 1 стоит пробежать глазами по диагонали, Часть 2 — не содержит для вас ничего нового. При этом вы можете принести несомненную пользу обществу, если добавите поддержку SDRAM для еще одной отладочной платы. На текущий момент она реализована только для Terasic DE10-Lite — одной из 9 плат, на которые в рамках проекта MIPSfpga-plus было портировано ядро MIPSfpga.

Общие сведения

MIPSfpga — это доступное под академической лицензией (бесплатно лицензируемое для образовательных и исследовательских проектов) промышленное микропроцессорное ядро MIPS microAptiv. О том, как получить доступ к исходным кодам этого ядра, в свое время подробно писал Юрий Панчул.

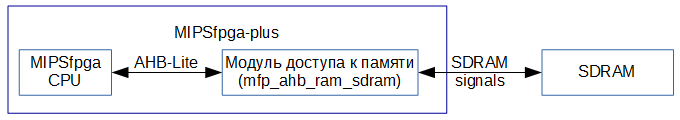

MIPSfpga-plus — это выполненный на основе MIPSfpga проект системы на кристалле, помимо ядра включающий некоторую дополнительную периферийную обвязку. Изначально он создавался для проведения лабораторных работ по работе с MIPSfpga, но ничто не мешает вам взять его за основу своей системы. Одна из основных "фишек" проекта: возможность заливки программы в память системы с использованием usb-uart преобразователей ($5), которые более доступны, чем Bus Blaster ($50).

Конфигурация системы

Основные параметры модуля доступа к SDRAM (mfp_ahb_ram_sdram.v)

- На текущий момент поддерживаются чипы только с 16-разрядной шиной данных — именно такой разрядности память на Terasic DE10-Lite;

- Небольшой размер модуля (менее 300 строк кода);

- Реализован минимально необходимый для работы набор операций: INIT, READ, WRITE, AUTO_REF;

- Модуль работает на частоте процессора (50 МГц), никаких синхронизаций или clock domain crossing;

- Все настройки, связанные с таймингами вынесены в параметры модуля, что упрощает его перенос на другие платы;

- Оптимизация страничного доступа к памяти — отсутствует. Пакетные операции (Burst Operation, WRAP4 в терминологии шины AHB-Lite) обрабатываются как набор отдельных (SINGLE) операций;

- Для запуска в режиме симуляции использована Verilog модель от компании Micron;

- Корректная работа на железе подтверждена на плате Terasic DE10-Lite (чип памяти IS42S16320D);

- Для проверки корректности написана отдельная С-программа 04_memtest, запускаемая на MIPSfpga-plus. Она записывает большой массив в память а затем, с определенной периодичностью проверяет целостность данных в этом массиве, выводя текущий этап на LED, номер цикла проверки и суммарное количество ошибок — на 7-сегментные индикаторы;

- Отладка разработанного модуля доступна "в отрыве" от кода MIPSfpga-plus в рамках проекта: ahb_lite_sdram — это песочница, в которой я начинал разработку. Там тестбенчи, а также standalone модуль, имитирующий работу AHB-Lite master без cpu (для аппаратного тестирования). Этот проект может быть использован для упрощения портирования на другие платы;

- При работе с SDRAM не поддерживается режим занижения тактовой частоты cpu, доступный в MIPSfpga-plus (опция MFP_USE_SLOW_CLOCK_AND_CLOCK_MUX).

Порядок конфигурации и запуска теста памяти

Предполагается, что у вас уже есть развернутые и компилируемые MIPSfpga и MIPSfpga-plus. Если это так, то для использования SDRAM необходимо:

- Получить актуальный код MIPSfpga-plus с github.

- Выбрать тип используемой памяти в mfp_ahb_lite_matrix_config.vh

MFP_USE_BYTE_MEMORY — блочная память с побайтовым хранением (x8);

MFP_USE_WORD_MEMORY — блочная память с хранением по словам (x32);

MFP_USE_BUSY_MEMORY — блочная память с имитацией задержки в работе;

MFP_USE_SDRAM_MEMORY — память sdram. - Перейти в каталог programs4_memtest;

- Выбрать соответствующий режим работы в main.c

SIMULATION

SDRAM_64M

SDRAM_8M - Установить (выбрать) соответствующую режиму и объему памяти границу стека в файле 02_compile_and_link.bat;

Для режима симуляции (SIMULATION)

- Произвести сборку программы, сформировать файлы для инициализации памяти, запустить симуляцию:

02_compile_and_link.bat

05_generate_verilog_readmemh_file.bat

06_simulate_with_modelsim.bat

При работе с платой (SDRAM_64M, SDRAM_8M)

- Выполнить сборку и заливку конфигурации на fpga;

- Выполнить (нажать) сброс на плате — при сбросе инициализируется в т.ч. модуль доступа к sdram;

- Произвести сборку программы, сформировать файл для заливки прошивки, залить прошивку:

02_compile_and_link.bat

08_generate_motorola_s_record_file.bat

12_upload_to_the_board_using_uart.bat - Во время работы LED будут обозначать текущий этап проверки:

0 — цикл записи;

1- цикл сброса кэша;

2 — пауза;

3 — цикл чтение;

4 — все проверки завершены, ошибок нет;

5 — в ходе проверок обнаружен ошибки. - Во время работы 7-сегментные индикаторы (на de10-lite их 6) будут обозначать:

два старших разряда — номер проверки;

четыре младших разряда — количество обнаруженных ошибок чтения.

Что еще можно сделать

Моей целью было создание максимально простого работающего решения, прозрачного и легко переносимого на другие платы. Модуль несколько примитивен по сравнению со своими "взрослыми" аналогами, это оставляет простор для модернизации и повышения его производительности:

- Обеспечить работу памяти на удвоенной частоте (100 МГц), относительно частоты cpu (50 МГц);

- Обеспечить работу памяти на максимально доступной для чипа частоте, добавив clock domain crossing;

- Обеспечить возможность работы памятью другой разрядности;

- Оптимизировать работу модуля для страничного доступа к памяти;

- Выбор наилучшей стратегии запуска AUTO_REF в зависимости от интенсивности использования памяти.

Буду признателен за пулреквесты с исправлением багов и новой функциональностью.

Благодарности

Автор выражает благодарность коллективу переводчиков учебника Дэвида Харриса и Сары Харрис «Цифровая схемотехника и архитектура компьютера», компании Imagination Technologies, а также персонально Юрию Панчулу YuriPanchul.

Автор: SparF