Меня зовут Андрей Бакшаев, я ведущий инженер-программист в YADRO. Моя команда занимается разработкой и оптимизацией математических библиотек под архитектуру x86. До этого я 15 лет работал в Intel. Значительная часть моих задач заключалась в том, чтобы реализовывать некоторые алгоритмы обработки изображений и сигналов в довольно известной математической библиотеке IPP, максимально эффективно используя возможности процессоров. Я также исследовал производительность этих алгоритмов в процессорах на ранней стадии проектирования.

Рубрика «AVX-512»

Как оптимизировать код на С для x86-процессоров: подсистема кэша и памяти, инструкции AVX-512

2023-12-12 в 11:03, admin, рубрики: AVX-512, AVX2, dsp, icelakeНовая библиотека x86 SIMD интринсиков — immintrin debug

2019-05-30 в 8:58, admin, рубрики: AVX-512, simd, x86, Блог компании Intel, высокая производительность, ПрограммированиеС каждым новым поколением процессоров Intel появляются новые и все более сложные векторные инструкции. Хотя длина вектора (512 бит) в ближайшее время расти не будет, появятся новые типы данных и виды инструкций. Например, кто сможет с первого взгляда понять, что делает такой интринсик (и соответствующая ему инструкция процессора)?

Bitwise ternary logic that provides the capability to implement any three-operand binary function; the specific binary function is specified by value in imm8.

__m512i _mm512_mask_ternarylogic_epi32 (__m512i src, __mmask8 k, __m512i a, __m512i b, int imm8)

FOR j := 0 to 15

i := j*32

IF k[j]

FOR h := 0 to 31

index[2:0] := (src[i+h] << 2) OR (a[i+h] << 1) OR b[i+h]

dst[i+h] := imm8[index[2:0]]

ENDFOR

ELSE

dst[i+31:i] := src[i+31:i]

FI

ENDFOR

dst[MAX:512] := 0

ОК, допустим, мы разобрались, как она работает. Следующий уровень сложности — отладка кода, интенсивно использующего такие интринсики.

Читать полностью »

Подводные грабли управления частотами процессоров Intel

2017-11-13 в 15:17, admin, рубрики: AVX-512, intel, Skylake, системное администрированиеВо время сравнения нового серверного чипа Centriq от Qualcomm с имеющимися в наличии Intel Xeon поколения Skylake мною была замечена странная штука: производительность шифра ChaCha20-Poly1305 плохо масштабируется при добавлении ядер. Один поток работал на скорости примерно 2,89 Гбайт/с, а на 24 ядрах и при 48 потоках сумарная производительность составила всего лишь 35 Гбайт/с.

Неплохо, конечно, но я ожидал увидеть что-то вроде 69 Гбайт/с. 35 Гбайт/с это всего лишь 1,46 Гбайт/с на ядро, или около 50 % от производительности одного ядра. AES-GCM масштабируется в тех же условиях гораздо лучше, до примерно 80 % производительности одного ядра, что объясняется способностью процессора повышать частоту при нагрузке на одно ядро.

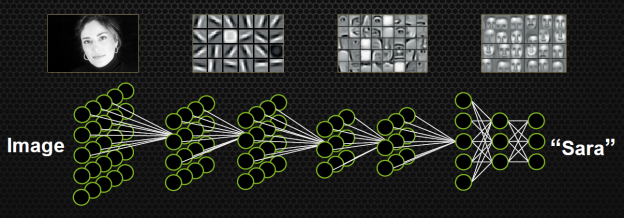

Intel добавит в CPU инструкции для глубинного обучения

2016-10-15 в 12:34, admin, рубрики: AVX-512, cpu, intel, глубинное обучение, искусственный интеллект, Программирование, Процессоры

Некоторые из последних процессоров Intel поддерживают семейство векторных инструкций AVX-512. Они выполняются блоками по 512 бит (64 байта). Преимущество аппаратной поддержки таких больших инструкций в том, что за один такт процессор обрабатывает больше данных.

Если код загружается 64-битными словами (8 байт), то теоретически, если не брать в учёт другие факторы, можно ускорить его выполнение в восемь раз, если использовать инструкции AVX-512.

Читать полностью »

Векторизация кода преобразования координат в пространстве на Intel® Xeon Phi™ с помощью низкоуровневых инструкций

2016-07-13 в 7:35, admin, рубрики: AVX-512, KNC, simd, Алгоритмы, Блог компании Intel, Блог компании Singularis, векторизация, высокая производительность, интринсики, матрицы преобразований, сопроцессорВведение

При решении задач моделирования движения объектов в трехмерном пространстве практически всегда требуется использование операций пространственных преобразований, связанных с умножением матриц преобразований и векторов. Для задачи N тел эта операция используется многократно для задания поворота и смещения тела относительно начала координат. Матрица пространственного преобразования имеет размерность 4х4, а размерность вектора, к которому применяется преобразование, соответственно 4x1. Рассмотрим оптимизацию выполнения такой операции с большим числом матриц и векторов под архитектуру Intel® Xeon Phi™.