“CVAX — когда вы забатите довольно воровать настоящий лучший”.

Надпись, оставленная американскими инженерами для советских коллег в топологии микропроцессора.

Реверс-инжиниринг микросхем — головная боль производителей с самых первых лет существования микроэлектроники. Вся советская электроника в какой-то момент была построена на нем, а сейчас с гораздо большим размахом тем же самым занимаются в Поднебесной, да и не только в ней. На самом деле, реверс-инжиниринг абсолютно легален в США, Евросоюзе и многих других местах, с целью (цитирую американский закон) “teaching, analyzing, or evaluating the concepts or techniques embodied in the mask work or circuitry”.

Самое частое легальное применение реверс-инжиниринга — патентные и лицензионные суды. Промышленный шпионаж тоже распространен, особенно с учетом того, что электрические схемы (особенно аналоговые) часто являются ключевой интеллектуальной собственностью и редко патентуются — как раз для того, чтобы избежать раскрытия IP и участия в патентных судах в качестве обвиняющей стороны. Разумеется, оказавшись в ситуации, когда нужно защитить свою интеллектуальную собственность, не патентуя ее, разработчики и производители стараются придумать способы предотвращения копирования своих разработок.

Другое не менее (а то и более) важное направление защиты микросхем от реверс-инжиниринга — обеспечение безопасности информации, хранимой в памяти. Такой информацией может быть как прошивка ПЛИС (то есть опять-таки интеллектуальная собственность разработчика), так и, например, пин-код от банковской карты или ключ шифрования защищенной флэшки. Чем больше ценной информации мы доверяем окружающему миру, тем важнее защищать эту информацию на всех уровнях работы обрабатывающих ее систем, и хардварный уровень — не исключение.

Перво-наперво: важная вещь, которую надо понимать. Говоря как о реверс-инжиниринге, так и о защите от копирования данных, надо понимать, что абсолютно устойчивых методов защиты не существует, и всё, что реально — сделать процесс настолько долгим и/или дорогим, чтобы он стал экономически нецелесообразным.

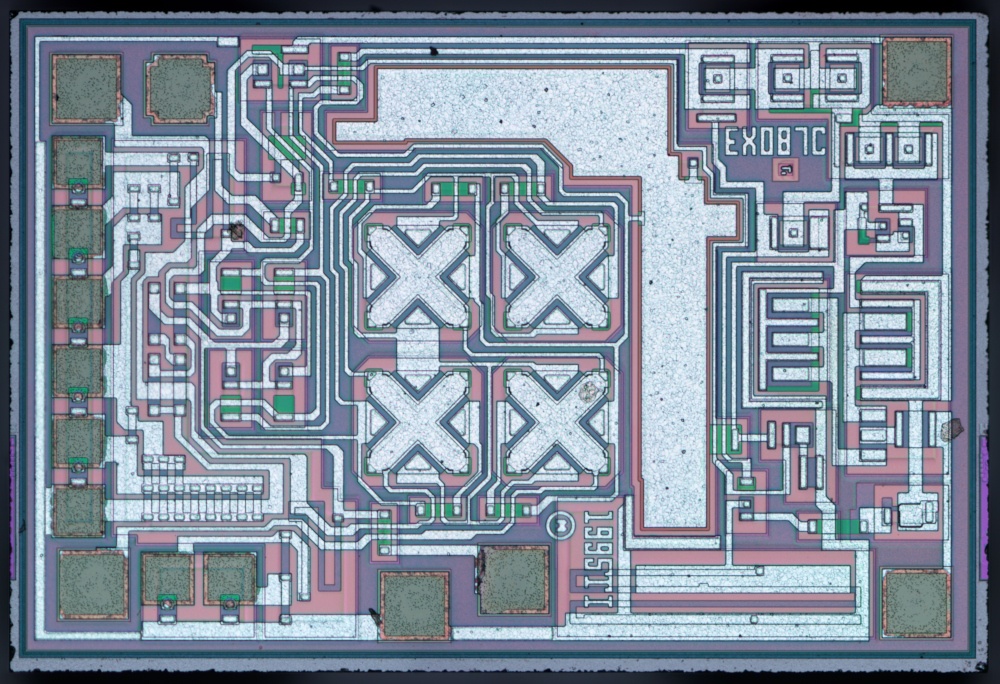

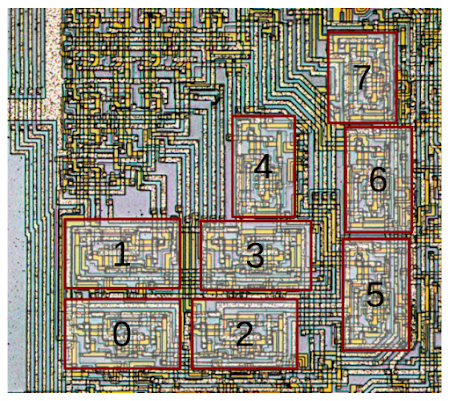

Много лет назад труд реверс-инженера или микроэлектронного пирата был намного проще, чем сейчас. Посмотрите, например, на вот этот снимок (спасибо BarsMonster за наше счастливое детство и хорошие фотографии): при базовом понимании технологии восстановить из него электрическую схему — дело нескольких часов.

Рисунок 2. Снимок топологии операционного усилителя OPA134PA. Источник — zeptobars.com

Вот здесь, кстати, есть пример реверс-инжиниринга микросхемы TL431, сделанного Кеном Ширриффом по фотографиям BarsMonster. А вот здесь — русский перевод. В блоге Кена много всего крутого, если вам интересна тема любительского реверс-инжининга.

А вот здесь (осторожно, трафик!) — отчет от реверс-инжиниринге процессора Zilog Z80-CTC, сделанном в 1979 году, почти сразу после выхода микросхемы. Сейчас это уникальный исторический документ, а тогда это была информация, имевшая колоссальную коммерческую ценность и, полученная (судя по нескольким упоминаниям военных стандартов), вероятно, в процессе серитификации микросхемы для специальных применений.

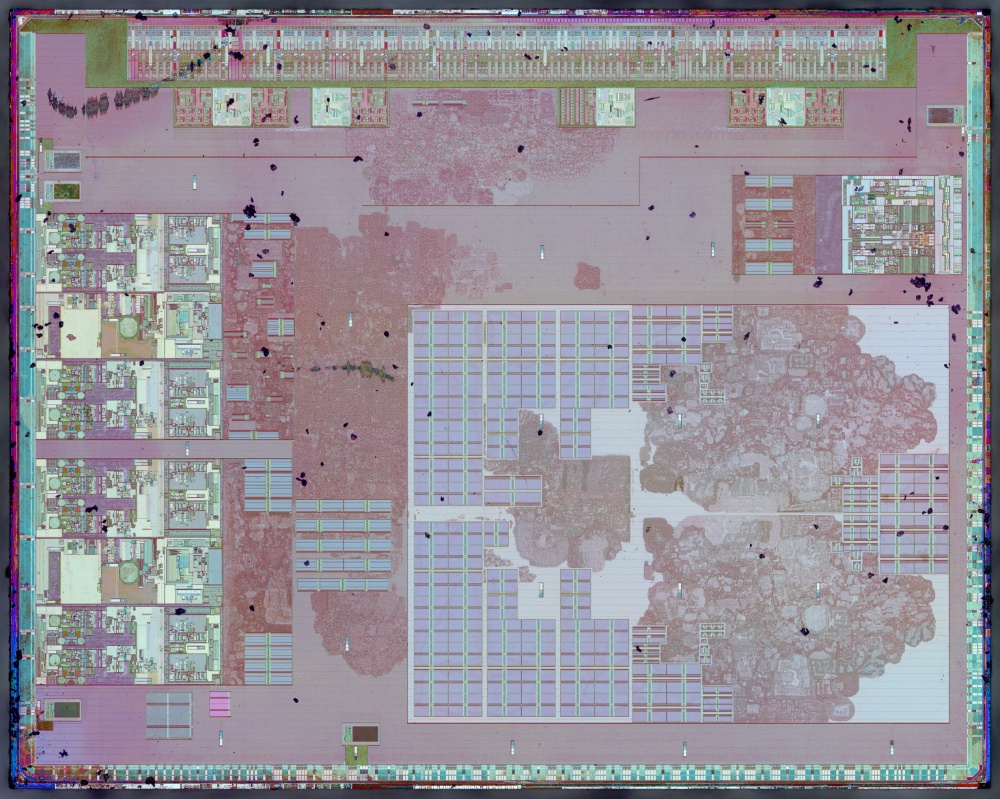

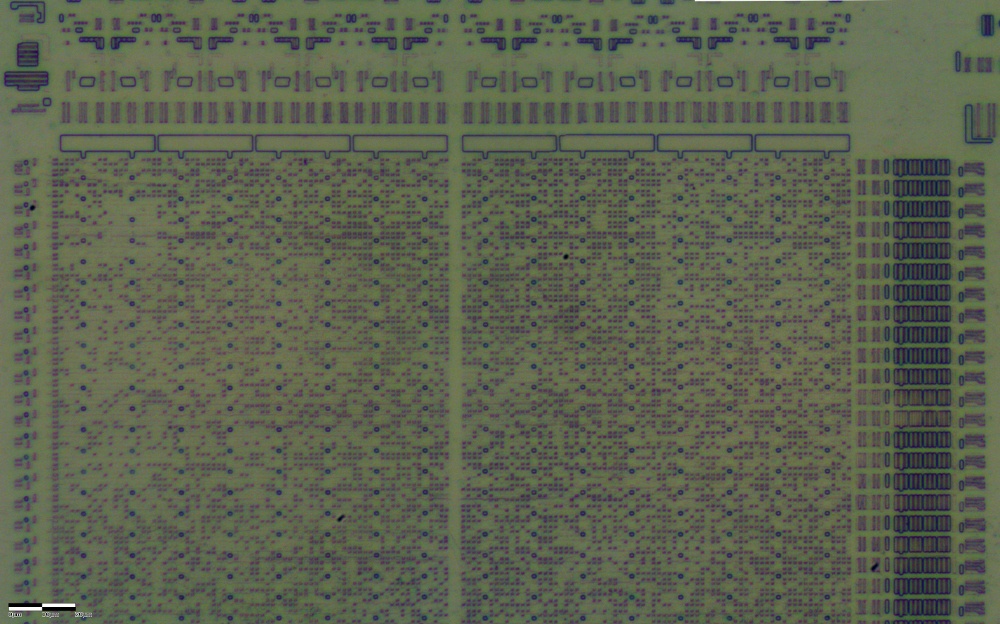

Но мы живем в 2019, а не в 1979 году, и сейчас отреверсить полную схему свежего микропроцессора Intel — дело многих месяцев или лет даже при хорошем уровне автоматизации процесса (не говоря уже о том, что даже отснять в приемлемом разрешении топологию с проектными нормами 14-10-7 нм — это очень сложная задача). Да что Intel? Сравните объем работы по реверс-инжинирингу или анализу усилителя с картинки выше и процессора “Байкал-Т1”, выполненного по очень популярному и относительно доступному 28 нм техпроцессу. Полный реверс-инжиниринг таких больших продуктов нужен крайне редко, чаще интересно посмотреть на какие-то конкретные и относительно небольшие блоки. Например, чтобы узнать, не нарушают ли они ваш патент, или сравнить ваше решение с продукцией конкурентов и попробовать понять, почему оно лучше или хуже. Или чтобы узнать, самостоятельно разработчики чипа реализовали ту или иную функциональность, или позаимствовали ваш IP-блок.

Рисунок 3. Снимок топологии процессора «Байкал-Т1». Источник — zeptobars.com

Тут мы переходим к следующей важной части в истории реверс-инжиниринга. В стародавние времена весь чип от начала до конца разрабатывался внутри одной компании, иногда даже силами очень маленькой команды или гениального одиночки типа Боба Видлара. В современных микросхемах полно IP-блоков, продажа и покупка которых — огромный рынок, на котором, разумеется, тоже есть и контроль за авторскими правами, и промышленный шпионаж, и пиратство. Поэтому смотреть на проблему защиты от несанкционированного копирования можно и нужно не только с точки зрения разработчика конечного продукта, но и с точки зрения разработчика IP, для которого разработчик продукта тоже может быть пиратом.

В случае же со взломом для получения данных нарушителю обычно неинтересна внутренняя структура микросхемы, и частичный реверс-инжиниринг делается (если вообще делается) для того, чтобы найти уязвимые места и использовать эти уязвимости, как при помощи непосредственного подключения,, так и другими методами. Задача разработчика по борьбе со взломом состоит в том, чтобы предотвратить использование потенциально уязвимых мест и, при необходимости, уничтожить чувствительные данные при попытке взлома.

ДЕЙСТВУЮЩИЕ ЛИЦА

Для начала давайте разберемся, кто и от того может защищать дизайн микросхемы. В цепочке от идеи до применения участвуют следующие сущности, имеющие разные виды доступа к информации о содержимом микросхемы.

- Разработчик IP-блока. Имеет всю информацию, все нужные файлы, методики измерения и т.д. и т.п.

- Разработчик микросхемы. В случае применения Soft IP имеет Verilog/VHDL код блока, в случае Hard IP может иметь как топологию, так и черный ящик. В случае наличия в блоке каких-то программируемых или софтовых частей имеет доступ и к ним тоже.

- Фабрика. Имеет доступ в GDSII файлам топологии, но не имеет доступа к программно-зависимой части микросхемы (например, к прошивке PROM).

- Корпусировочное и тестировочное производство. Имеет доступ к кристаллу, а также к методикам тестирования и картам прошивки однократно программируемой памяти. От них редко кто-то целенаправленно защищается, но они должны быть в списке, потому что против них не работает часть методов, пригодных для защиты от фабрики.

- Конкурент/взломщик. Имеет доступ только к готовому изделию и пользовательской документации.

В самом простом случае разработчик микросхемы (2) хочет защититься от копирования конкурентом (5) или сделать чип с защищенной от несанкционированного чтения памятью. В чуть более сложном — разработчик IP (1) хочет удостовериться в соблюдении разработчиком микросхемы (2) лицензионного соглашения. Еще бывает, что разработчик микросхемы (2) не доверяет фабрике (3) и подозревает, что она может гнать контрафакт в ночную смену.

О том, что такое IP в интегральных микросхемах я подробно писал некоторое время назад, так что в этой статье не буду повторяться. Там же есть немного о том, как разработчики IP защищают свою интеллектуальную собственность. Если совсем коротко, то для защиты топологии обычно практикуется участие фабрики как третьей стороны, и собственно топологию покупатель IP не получает, а для зашиты кода на Verilog используются техники обфускации, сходные с техниками обфускации любого другого кода.

ИНСТРУМЕНТЫ

Какие инструменты для анализа микросхемы существуют? Первый уровень — это немного кислоты, чтобы сначала вскрыть корпус микросхемы, а потом снимать слои один за другим, и обычный оптический микроскоп с фотоаппаратом. Стоит недорого, работать с ними просто, и для анализа простых схем, сделанных по не самым новым технологиям, этого вполне достаточно.

Для схем большего размера существуют специальные САПР, позволяющие в той или иной мере автоматизировать восстановление данных из топологии — обеспечивая реверс-инженеру более удобный интерфейс для работы, чем просто рисование линий в графическом редакторе. Автоматизацию также упрощает то, что все современные цифровые схемы построены из библиотек, и после реверс-инжиниринга элементов библиотеки собрать схему — это вопрос времени (или доступной вычислительной мощности).

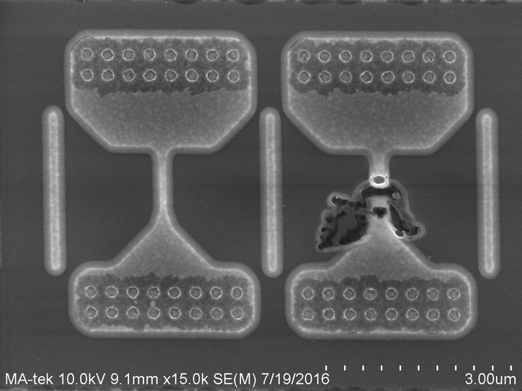

Следующий уровень, недоступный любителям, но присутствующий в специализированных лабораториях — это сканирующий электронный микроскоп (SEM). В нем вместо светового луча используется сфокусированный пучок электронов. Разрешение SEM может доходить до 1 нм и даже чуть ниже, что достаточно для анализа любых современных интегральных схем.

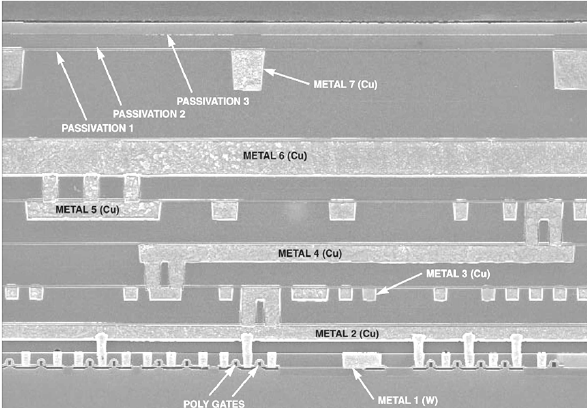

FIB — это аналог SEM, только использующий вместо пучка электронов пучок более тяжелых ионов. Собственно, FIB — это Focused Ion Beam. Главное отличие FIB от SEM — c его помощью можно не только анализировать микросхему, но и модифицировать ее, например, делать разрезы (для того, чтобы посмотреть сечение микросхемы или удалить какой-то кусок) или напылять материал (для того, чтобы создать соединение там, где его нет). FIB широко используются разработчиками и производителями микросхем для работы с тестовыми образцами, потому что исправление ошибки с его помощью, хоть и занимает много времени, но все же гораздо быстрее и дешевле перезапуска опытной партии. Для реверс-инженера это еще и уникальный способ добраться до тех частей кристалла, которые по замыслу разработчика не должны быть доступны. И, проектируя защищенную от взлома микросхему, это тоже надо иметь в виду.

Рисунок 4. Разрез микросхемы, сделанный при помощи FIB. Источник — SERESSA-2015 (осторожно, очень много трафика в pdf по ссылке).

Рисунок 5. Сделанная с помощью FIB модификация микросхемы, меняющая несколько соединений.

Еще один незаменимый инструмент реверс-инженера — набор лазеров. Любителям доступны мощные лазеры, с помощью которых можно вскрывать микросхемы в пластиковых корпусах и получать доступ к кристаллу. Для профессиональных лазеров, в зависимости от длины волны, могут быть прозрачными одни части конструкции микросхемы и непрозрачными другие. Это позволяет использовать лазер, например, для точного вскрытия пассивации и изоляции, чтобы потом можно было удобно присоединиться к металлической линии, не рискуя закоротить ее с соседями. Другие параметры позволят резать металл или сжигать отдельные транзисторы. Третьи — индуцировать ток в транзисторах, переключая ячейки кэш-памяти или какие-то логические линии. Последний вариант повсеместно используется как недорогая имитация воздействия тяжелых заряженных частиц, но в принципе внесение сбоев в работающую микросхему может быть полезна и для компрометирования содержащейся в ней информации. Например, может быть интересно переписать какой-нибудь флаг в регистровом файле или немного подправить работу генератора случайных чисел.

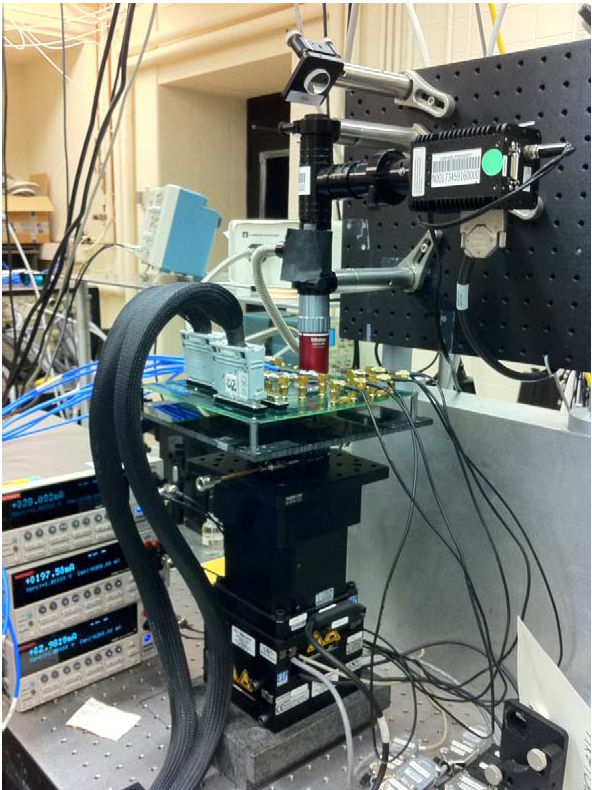

Рисунок 6. Внешний вид лазера для изучения влияния одиночных сбоев на микросхемы. Источник — SERESSA-2015.

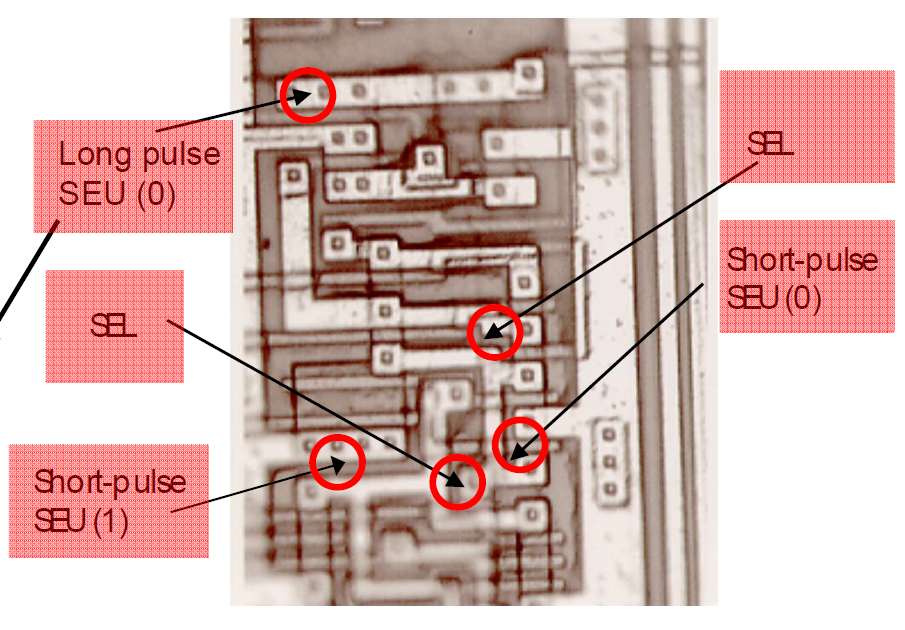

Рисунок 7. Пример полученной с помощью лазера карты чувствительности части микросхемы к одиночным сбоям и отказам. Источник — SERESSA-2015.

В продвинутых лабораториях реверс-инжиниринга и можно найти много других интересных инструментов; например, цифровой сигнал до нескольких десятков МГц можно мониторить в реальном времени, поместив на соответствующую линию небольшой кусочек ниобата лития и подсветив его опять же лазером.

КЕЙС 1: НЕНАДЕЖНАЯ ФАБРИКА

Какие могут быть причины не доверять фабрике, на которой вы изготавливаете свои кристаллы? В идеальном мире вы, разумеется, не станете связываться с фабрикой, которой не доверяете, но иногда коммерческие соображения вынуждают идти на риск. Минимизировать его можно двумя основными способами:

- Так называемое split fabrication или, по-простому, производство на двух фабриках. Но не параллельно (как обычно делается для минимизации риска дефицита в случае непредвиденных задержек на производстве), а часть операций на одной фабрике и часть на другой. Это довольно неудобно для всех участников процесса (и уж точно не каждая фабрика на такое согласится), но это вынудит ненадежную фабрику по крайней мере реверсить оставшуюся часть дизайна чипа и самостоятельно делать недостающие маски. (что, в идеале, должно сделать так, чтобы игра не стоила свеч). Главный минус этого подхода состоит в том, что верхние слои чипа — это металлизация, которая реверс-инжинирится довольно просто. Split fabrication, впрочем, может быть действительно эффективно в сочетании с каким-то технологическим ноу-хау в металлах, которое ненадежная фабрика не в состоянии воспроизвести. Например, если вторая выбранная вами фабрика умеет делать в верхнем слое металлизации энергонезависимую память (MRAM, мемристоры или что-то еще подобное), без которой весь дизайн теряет смысл.

- Если никакого технологического ноу-хау у вас нет, то простой и надежный путь состоит в том, чтобы сделать чип бессмысленным без последующего программирования. Программируемые блоки можно сделать как самостоятельно с помощью конфигурационной памяти, так и в виде блока на основе встраиваемой ПЛИС (такие IP есть на рынке). Конфигурационная память как способ защиты позволяет вам быть уверенными, что фабрика не может просто взять и произвести ваш чип в обход вас. Но ведь конфигурационную память можно прочитать, не так ли? Да, но наличие конфигурационной памяти вынуждает ненадежную фабрику вместо простого пути увеличения объемов производства заниматься тем же реверс-инжинирингом, что и все другие злоумышленники.

Отдельно замечу, что оба описанных метода защиты от ненадёжной фабрики помогают от несанкционированного копирования, но не спасают от популярных в узких кругах “закладок”. Более того, чуть дальше я расскажу о том, как делать “закладки” в топологии самим.

КЕЙС 2: ЗАЩИТА ПАМЯТИ

Наличие в чипе программируемых блоков и конфигурационной памяти — практически непременный атрибут любого современного дизайна, как цифрового, так и аналогового. С уменьшением проектных норм растет разброс параметров от кристалла к кристаллу, и цифровая подстройка — самый простой и надежный способ его преодолеть. А цифровые схемы (например микроконтроллеры) обычно хранят данные прямо на кристалле и могут иметь многоуровневую структуру памяти, разные части которой имеют разный уровень доступа и защиты. Поэтому выглядит логичной идея во-первых, использовать для повышения безопасности и взломоустойчивости инструмент, который у нас и так есть, а во-вторых, идея внимательно думать над тем, какой именно тип памяти использовать.

Прошивка металлическими соединениями (Mask ROM). Обычно выглядит как наличие или отсутствие контакта между двумя металлическими линиями, чуть реже — как наличие или отсутствие транзистора между ними. Самая дубовая, применяется в базовых матричных кристаллах (БМК) — не только в древней оборонке, как вы могли бы подумать, но и во вполне современных решениях, например во вспомогательных чипах внутри процессоров Xeon. Кроме того, при помощи такой памяти делаются семейства микросхем (в основном микроконтроллеров), потому что перепрошивка памяти на производстве путем изменения одной маски дешевле, чем поголовная прошивка каждого произведенного кристалла на пластине или в корпусе. Читается Mask ROM очень легко при помощи микроскопа и аккуратного травления. Дома вполне можно справиться.

Рисунок 8. Прошивка ROM металлическими межсоединениями на поддельном чипе FTDI FT232RL. Источник — zeptobars.com

Здесь также надо заметить, что прошивать память можно не только слоем контактов между металлами, но также наличием и отсутствием металла (легко читается оптически), наличием или отсутствием легирования (легко читается оптически) или, например, уровнем порогового напряжения транзистора (плохо читается оптически). Так что в принципе, у mask ROM не все потеряно, если вы действительно хотите спрятать ее содержимое.

Память на пережигаемых перемычках (Fuse ROM). Допускает одну запись (в том числе запись пользователем на готовом устройстве) и неограниченное количество чтений, очень проста в изготовлении и программировании и поэтому популярна для разного года конфигурационной памяти и прошивок.

Рисунок 9. Два состояния Fuse ROM. Источник — semiengineering.com

Как видите, состояние обычной пережигаемой перемычки (Fuse) очень легко посмотреть в микроскоп, то есть защититься от вскрытия кристалла с ее помощью просто нельзя. Ну и, кроме всего прочего, классическая пережигаемая перемычка довольно большая (несколько квадратных микрон) и поэтому не подходит для больших объемов памяти.

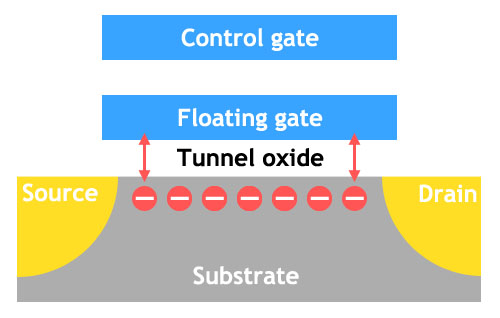

Флэш-память и другие варианты EPROM и EEPROM, основанные на транзисторах с плавающим затвором.

Рисунок 10. Схема записи флэш-памяти. Источник — techreport.com

Принцип функционирования этого типа памяти довольно прост: в толстом слое диэлектрика находится “плавающий” затвор. В этот затвор можно поместить электрический заряд при помощи туннелирования, подав на него высокое напряжение. А дальше, если высокое напряжение не подавать, заряд может храниться в “плавающем” затворе очень долго.

А что с безопасностью? Хорошая новость состоит в том, что состояние EEPROM нельзя увидеть микроскопом. Плохая? Их сразу несколько.

Первая плохая новость состоит в том, что EEPROM стирается не только высоким напряжением, но и воздействием ультрафиолетового излучения (старожилы наверняка помнят чипы с кварцевым стеклом). При этом, если вы внимательно посмотрели в микроскоп на топологию, у вас вполне может получиться прикрыть непрозрачным материалом всю память, кроме тех нескольких бит, которые включают защиту от чтения, и после засветки чип ваш. Мораль: используя в своем проекте EEPROM, накрывайте ее сверху металлом. Причем желательно не только сплошным щитом от излучения, но и какими-то значимыми линиями, чтобы щит нельзя было аккуратно стравить. Впрочем, тут тоже скрывается засада, потому что

В качестве альтернативной опции можно сконфигурировать биты включения/выключения защиты таким образом, чтобы их стирание включало защиту, а не выключало ее.

Вторая плохая новость — существуют сенсоры, способные считать электрический заряд в плавающем затворе или его остатки после операции стирания. Более того, для того, чтобы электрически считать память, в общем случае, на чип не нужно подавать питание, то есть нет риска включить встроенные механизмы уничтожения информации.

MRAM, хоть и относительно редкая, тем не менее, тоже заслуживает нашего внимания. Ее, как и флэш, невозможно считать оптически. Еще MRAM, разумеется, невозможно стереть ультрафиолетом, но вот сенсоры магнитного поля с достаточно высоким разрешением для того, чтобы стравить верхние металлы и считать память побитно, существуют. Хорошая новость? Потенциальный злоумышленник вряд ли их найдет быстро и недорого. В целом, MRAM — это хорошая альтернатива флэшу с точки зрения безопасности, но она пока что мало доступна и только-только пошла в серийное производство в доступных для fabless-компаний технологиях.

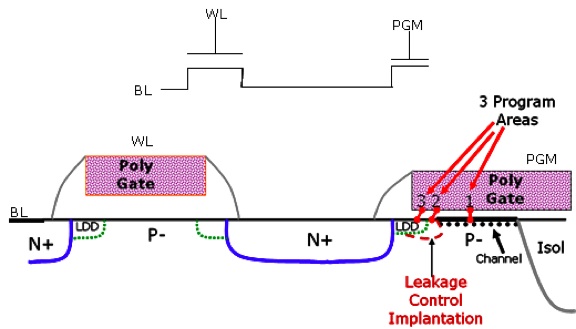

Самой защищенной от реверс-инжиниринга памятью на сегодняшний день считается antifuse ROM. Как видно из названия, она представляет собой некий антипод пережигаемых перемычек, а именно имеет высокое сопротивление в незапрограммированном состоянии и низкое в запрограммированном. Как это достигается? При помощи пробоя подзатворного диэлектрика транзистора высоким напряжением. Область пробоя настолько мала, что ее не видно ни сверху в микроскоп, ни в разрезе на FIB, но она при этом хорошо и надежно обеспечивает изменение сопротивления на несколько порядков, что вполне достаточно для надежного чтения состояния памяти штатным образом.

Рисунок 11. Сечение ячейки antifuse памяти. Показаны несколько областей возможного пробоя транзистора. Это может несколько усложнить схему чтения.

Разумеется, существуют и другие способы узнать содержимое памяти, помимо визуального осмотра ячеек. Самый простой способ — при помощи FIB напрямую подключиться к соответствующим линиям чтения и подать на них любые управляющие сигналы, которые нужно подать, чтобы считать информацию, недоступную нормальным способом. Предварительно можно отключить защиту от чтения, физически отрезав линии, ведущие к соответствующим битам памяти. Как защититься от этого? Правильно спроектировав топологию вашего чипа и, возможно, встроив в него некоторые дополнительные функции. Вот пример того, как это делает компания Cypress:

It is possible to configure the nvSRAM to provide password protected access. In this configuration, instead of performing the normal power up recall sequence on power up, the part waits for the user to enter a 5-byte password followed by an End Password Entry soft sequence. The End Password Entry soft sequence is a specific seven-address read sequence. If you enter the correct password, the part completes the boot up sequence and is ready for the normal nvSRAM operations. If you enter the incorrect password three times or you do not enter the right password within a specified period of time, the part locks up or fills the SRAM memory with random data, as the application requirement may be. The part can be configured to additionally destroy the functionality and cause physical damage to the chip.

Обычно делается так: память накрывается сверху сеткой из линий земли и питания, а все сигнальные линии располагаются строго под ними. При этом надо позаботиться о том, чтобы силовые линии, с одной стороны, не дублировали друг друга (то есть чтобы при перерезании любой из них часть микросхемы переставала работать), а с другой стороны, так, чтобы каждая из них обслуживала достаточно много бит памяти, и врезание амперметра в линию питания не могло позволить оценить состояние памяти по потреблению в режиме чтения (которое различается для разных логических состояний у большинства типов памяти). При такой организации верхних слоев чипа злоумышленнику будет максимально сложно вскрыть часть металлизации, чтобы подключиться туда, куда ему нужно.

Еще в сетку земель и питаний включают дополнительные защитные линии, устроенные таким образом, что разрыв на них (или их короткое замыкание на питание или землю) при подаче питания на чип инициализирует полное стирание содержимого защищенной памяти (или, как мы видели выше, физическое повреждение чипа). Такие защитные линии, расположенные рядом с линиями земли и питания, очень сильно затрудняют работу злоумышленников, потому что операции с FIB требуют ощутимого по меркам нынешних техпроцессов места. Кроме того, в силу конусообразной формы создаваемого микроскопом выреза, чем ниже слой, к которому вы хотите подключиться, тем больше площади вам нужно зачистить над ним.

Но на самом деле очень часто злоумышленнику может быть не нужно точное значение содержимого памяти, ему может вполне хватить уменьшения количества вариантов для перебора на несколько порядков. Например, если ячейка памяти потребляет во время чтения логической единицы X, а во время чтения логического нуля 100*X, то при чтении байта такой памяти мы получим разное потребление в зависимости от содержимого памяти:

0 — 800*X

1,2,4, …, 64, 128 — 701*X

3, 6, 7, …, 160, 192 — 602*X

….

255 — 8*X

Итого, если мы не трогаем память, для подбора содержащегося в ней пароля нам надо 256 попыток. А если мы знаем, что потребление в режиме чтения — 701*X — то всего восемь. Удобно, не правда ли? Самый простой способ что-то сделать с этой проблемой — хранить данные в виде значения и его инверсии в соседней ячейке; тогда потребление любого объема памяти в режиме чтения не будет зависеть от хранимой информации. Это, правда, требует в два раза больше памяти, но нам ведь важна безопасность, правда?

КЕЙС 3: БЕЗ ПАМЯТИ

А что если ваш чип не содержит конфигурационной памяти или содержит всего несколько бит, скрывать содержимое которых бессмысленно. Почему? Так существенно дешевле (не столько за счет уменьшения стоимости масок для литографии, сколько за счет более простого процесса корпусирования и тестирования), а для большинства простых микросхем цена — серьезное конкурентное преимущество.

Кстати, о тестировании. Процесс отбраковки кристаллов на пластинах и прошивки конфигурационной памяти довольно часто отдается на аутсорс, особенно маленькими компаниями, потому что соответствующее оборудование обычно не по карману стартапам, а качество обеспечивать нужно. Так вот, если стороннее производство в курсе ваших тестовых методик и обладает прошивками конфигурационной памяти — то лучше бы вам полностью доверять этим людям. Или иметь дополнительные методы защиты от реверс-инжиниринга, не завязанные на конфигурационную память.

Итак, что делать, если конфигурационная память — не вариант для защиты, или если только ее недостаточно?

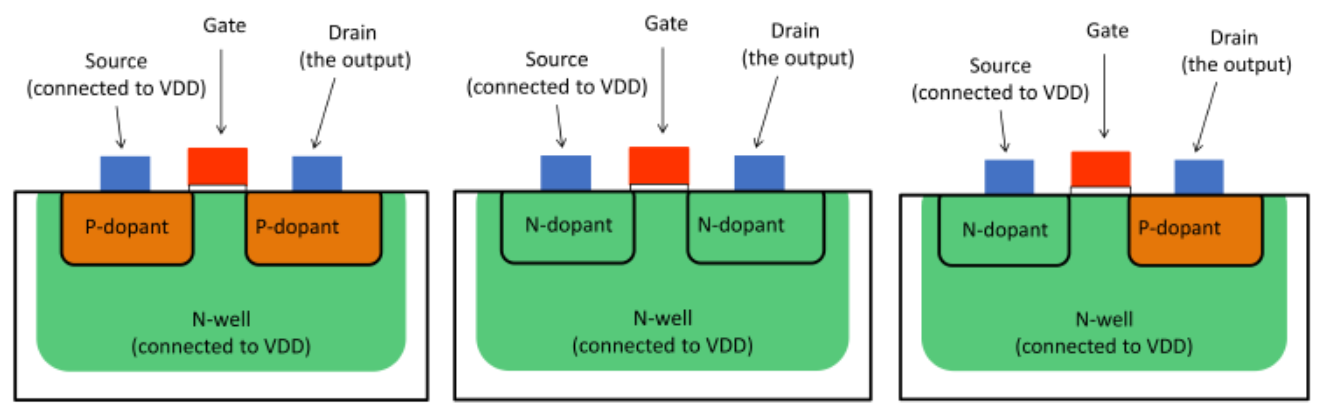

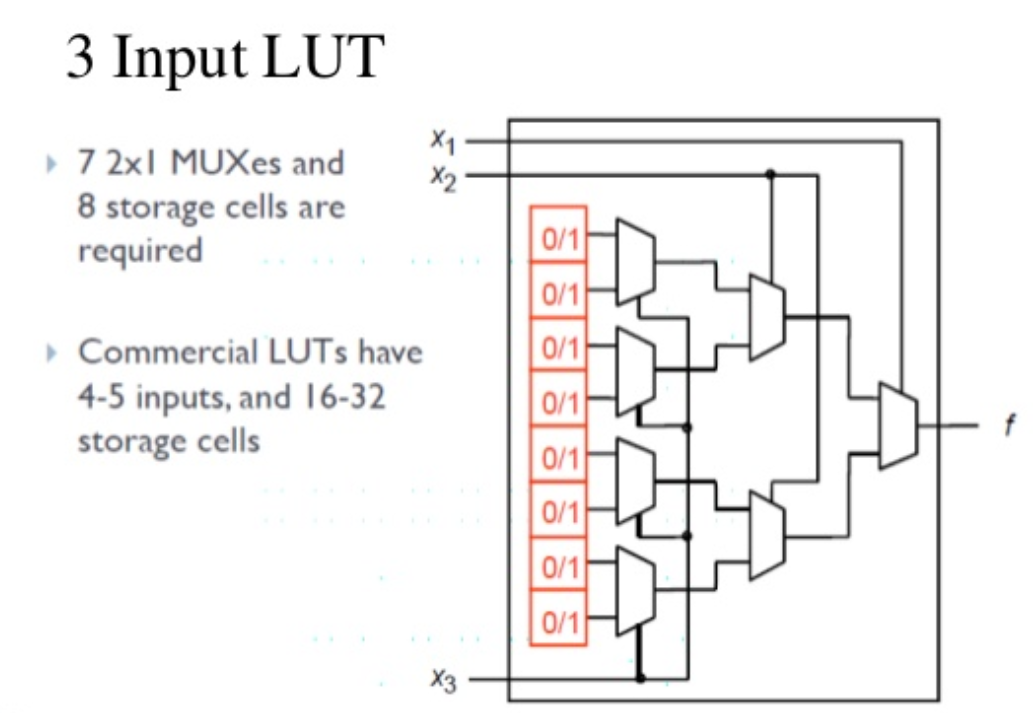

Главный недостаток как оптического микроскопа, так и SEM — на них очень сложно различить типы легирования кремния. То есть, наличие легирования видно, а тип — нет. Поэтому при анализе топологии и экстракции схемы тип легирования восстанавливается из контекста и подразумеваемой логики работы схемы (n-канальные транзисторы подключены к земле, p-канальные к питанию, и т.д. и т.п.). Нарисовав топологию вашей микросхемы так, что она не будет совпадать с интуитивно наиболее вероятным вариантом, вы можете очень здорово попортить кровь реверс-инженеру. Особенно если использовать несколько разных схем, замаскированных под одну и ту же. При некоторой сноровке можно не только затруднить анализ вашей схемы, но и заставить произведенный (или хотя бы смоделированный, но веселее, если произведенный ) по восстановленной топологии девайс делать что-то определенное, от закорачивания земли с питанием до выдачи на все выходы матерных слов. Детерминированное поведение неправильно украденного дизайна, к слову, может быть полезно не только для того, чтобы спалить пиратам осциллограф, но и для того, чтобы, когда к вам потом придут разочарованные пользователи “ваших” чипов, вы могли наглядно продемонстрировать им, что они купили подделку.

Рисунок 12. Разрез трех структур, неразличимых в микроскоп. Левая — pMOSFET, средняя — короткое замыкание, правая — обратно смещенный диод (разрыв).

Рисунок 13. Топология трех цифровых библиотечных ячеек, неразличимых в микроскоп. Левая — инвертор, средняя — прямое соединение входа и выхода, правая — логическая единиц на выходе.

Каждая из ячееек на рисунке выше выглядит почти как самый обычный инвертор, но может на самом деле быть инвертором, повторителем или генератором логического нуля или логической единицы. Выдают наш «инвертор» только контакты к диффузии от входа и выхода. Впрочем, отказавшись от них, мы получим совсем не отличимую от штатной схему в обмен на невозможность реализовать соединение входа и выхода (но сможем использовать для этой цели два инвертора). Впрочем, с возможностью при помощи одной и той же ячейки инвертировать или не инвертировать сигнал борьба со злоумышленником гораздо интереснее, потому что ничто так не усложняет попытки разобраться с неполадках незнакомого дизайна, как лишний инвертор где-нибудь в цепи тактирования или включения/выключения.

Хотя нет, бывает. Хорошо построенная руками топология обычно неплохо читается. Отличный пример есть в уже упомянутом блоге Кена Ширриффа.

Рисунок 14. Арифметико-логическое устройство (АЛУ) чипа Intel 8008. Показаны отдельные разряды.

На топологии АЛУ Intel 8008 прекрасно видны восемь идентичных схем — по числу разрядов. Понимая, что это АЛУ, вы сможете без труда восстановить схему по топологии. Если часть элементов в ней будет фальшивой, это несколько усложнит ваш труд, но не более того. А все потому, что топология хорошо ложится в базовое представление об интерфейсах между составными частями. Для того, чтобы запутать злоумышленника настолько сильно, чтобы он бросил попытки реверс-инжиниринга, надо сделать топологию непредсказуемой и неповторяющейся. Самый простой способ — не делать никакие блоки вручную, а генерировать в помощью САПР весь нетлист чипа целиком. Автотрассировщики, несмотря на колоссальную экономию времени на создание топологии (по сравнению с ручным трудом) прекрасно справляются с задачей создания неинтуитивной расстановки элементов и местами совершенно безумных соединений. И чем больше дизайн, топология которого была синтезирована целиком, тем сложнее его реверс-инжинирить.

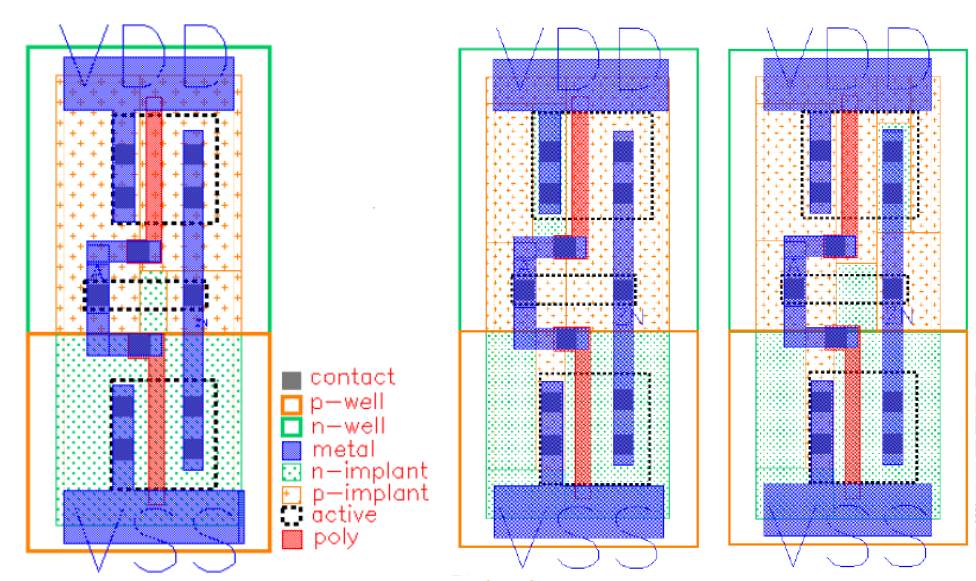

Но это самый простой способ. Есть более интересные варианты. Например, использовать набор ячеек-хамелеонов как набор генераторов логических нулей и единиц для входов мультиплексора, реализовав при этом произвольную логическую функцию. Собственно, так устроены элементы ПЛИС, LUT (Look-Up Table).

Рисунок 15. Реализация трехвходового LUT. Источник.

Поставив в разные места схемы несколько таких вот LUT и подведя к входам «ячеек памяти» какие-нибудь сигналы, мы решим сразу несколько задач:

1) Если наш маневр останется неразгаданным, то мы сможем задать то, как именно будет себя вести реверс-инжинированная схема. Варианты — любые, ограничены только вашей фантазией.

2) Использование произвольных сигналов из других блоков в качестве «входных» для ячеек, генерирующих логические ноль и единицу, затруднит процесс визуального разделения дизайна на блоки.

3) Даже если реверс-инженер поймет, что мы используем такие защищенные LUT, ему придется перебирать множество вариантов, чтобы восстановить функциональность схемы по топологии, так что даже относительно небольшое количество защишенных ячеек может сделать реверс-инжиниринг чрезмерно времязатратным. Мое любимое — собрать на таких LUT конечный автомат, управляющий переходами микросхемы из одного рабочего режима в другой.

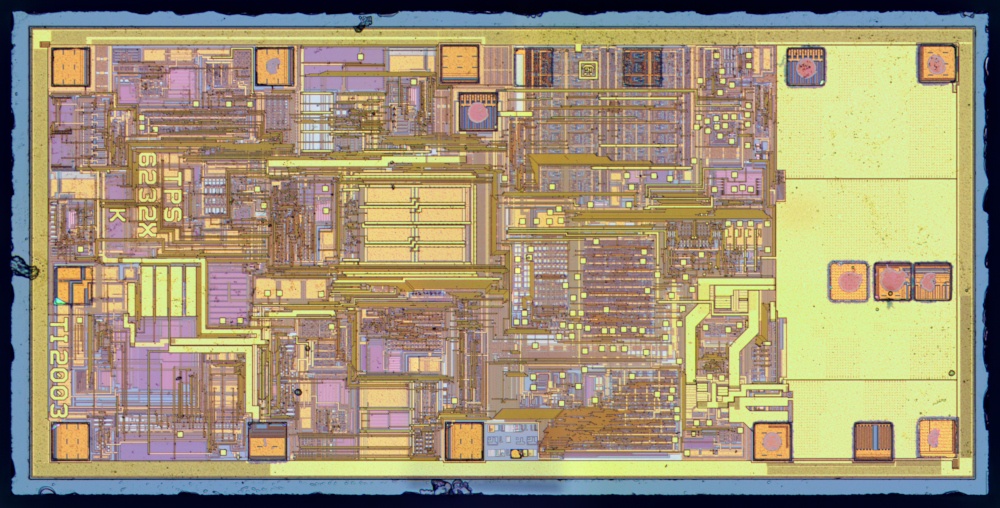

ТЕСТОВЫЕ СХЕМЫ

Хорошие инженеры очень любят всесторонне тестировать свои чипы. И под “всесторонне” я имею в виду — примерно так, как это сделано в DC/DC конвертере TI на рисунке ниже. Десятки небольших контактных площадок, к которым можно подключиться еще до разрезки пластины на отдельные кристаллы, чтобы проверить все нужные параметры, состояние важных внутренних линий, принять решение о том, годный чип или нет, и при необходимости выяснить причину проблем.

Рисунок 16. Топология Texas Instruments TPS 62321. Источник — zeptobars.com

Особенно важно хорошее покрытие тестовыми контактными площадками для тестовых запусков и прототипов, а вот для серийного производства их часто отключают (коррекцией одной-двух масок или пережигаемыми перемычками), чтобы минимизировать влияние на поведение изделия. Так вот, о чем это я? Тестовые контактные площадки — это ваша огромная помощь злоумышленнику, потому что вы не только сами указываете на важные точки в дизайне, но и даете удобный доступ к ним. Пережженная перемычка легко восстанавливается на FIB, и вуаля! В идеале, безопасность требует полного удаления тестовых контактных площадок из серийного чипа. Если же этот вариант нерационален (допустим, вам и в серийном производстве требуется тестирование на пластине), то стоит как минимум позаботиться о том, чтобы механизм отключения тестовых площадок не поддавался восстановлению, например, располагался непосредственно под площадкой и был нарисован таким образом, чтобы разрыв нельзя было удобно соединить.

Про то, что все современные цифровые дизайны имеют встроенный JTAG для тестирования, позволяющий непосредственно посмотреть состояние любого триггера на кристалле, я даже не хочу начинать. Тестопригодность — одна из ключевых характеристик любого дизайна, и именно это обстоятельство делает крайне важным надежное и невосстанавливаемое отключение всех тестовых интерфейсов перед тем, как чип покинет стены компании-производителя.

Еще хорошие инженеры любят располагать на периферии кристалла тестовые схемы для следующих ревизий. Обычно это достаточно важные схемы, иначе зачем тратить время и силы на организацию их тестирования? “Важные схемы, составляющие вашу интеллектуальную собственность и критичные для функционирования чипа? Заботливо положенные отдельно от всего дизайна? Спасибо большое!” — скажет вам реверс-инженер за такой королевский подарок. Если вы не хотите, чтобы тестовые помогли злоумышленнику изучить и скопировать ваш дизайн — позаботьтесь о том, чтобы они не попали в кристаллы для серийного производства или уничтожались после тестирования на пластинах в процессе резки пластины на кристаллы.

НЕМНОГО ПРАКТИКИ

Для того, чтобы еще раз продемонстрировать, как это работает, пример вскрытия микроконтроллера PIC12C508A, описанный в диссертации Сергея Скоробогатова, защищенной в 2004 году в Кембридже. Перевод сокращенный и достаточно вольный:

Необходимо вскрыть корпус и найти на кристалле защитную память, стираемую ультрафиолетовым излучением. Это делается довольно легко, при помощи просмотра линий, идущих к пину программирования чипа. Дальше вы прикрываете основную память непрозрачным для УФ материалом, и через пять-десять минут облучения вы сможете считать память штатным программатором. Другой вариант — после нахождения ячейки памяти защиты от копирования, просто перерезать ведущую к ней металлическую дорожку, которая на этом чипе по каким-то причинам расположена далеко от других линий — настолько далеко, что перерезать ее можно не только FIB, но и просто иголкой.

Рисунок 17. А вот и та самая злополучная линия. Действительно, находится посреди пустого места, никак не защищенная, можно резать.

ЗАКЛЮЧЕНИЕ

Разумеется, объять необъятное невозможно, ведь технологии и реверс-инжиниринга микросхем, и защиты от него не стоят на месте и постоянно совершенствуются. Тема защиты информации — одна из ключевых при проектировании для интернета вещей, поэтому разработчики уделяют ей много внимания, и такой легкой добычи, как пятнадцать или двадцать лет назад, реверс-инженерам ожидать не приходится. Тем не менее, всегда нужно помнить о том, что плохо защищенная система — это потенциальные убытки, огромные убытки или даже жизни людей, и защита от несанкционированного доступа и реверс-инжиниринга должна быть частью системы на всех уровнях функционирования, не исключая и «железный».

Автор: Валерий Шунков