С чего все началось

Я прочитал статью о позиционном кодировании (one-hot), которое работает быстрее для конечных автоматов.

Я сделал генераторы всех базовых арифметических и логических команд для любой разрядности, но оказалось, что я получу преимущество только если буду использовать логические элементы с транзисторами, спроектированные на другой уровень FO(Fan Out, не FO-4).

Но получил самый быстрый способ реализовать любую 2-4-битную функцию. (последовательный сумматор, работающий так же быстро, как сумматор с опережением переноса). Так что я создал селектор :)

Декодеры адресов DRAM/SSD и что о них можно прочитать

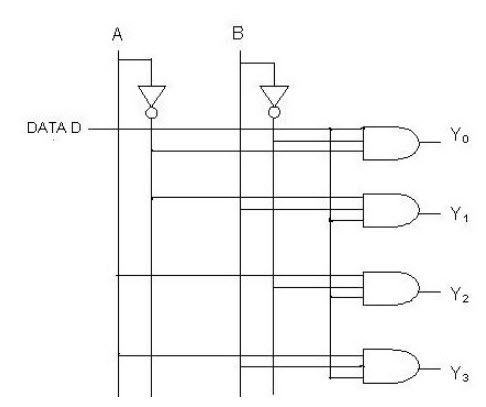

Ну, это разочаровывает. Вся информация о дешифраторах адресов памяти выглядит так:

-

(Демультиплексор NOR с N транзисторами на строку на N бит адреса, FanOut - M/2, где M - количество линий)

-

(Демультиплексор NAND с N транзисторами на строку на N бит адреса, FanOut - M/2, где M - количество линий)

-

(Что называется Еще хуже, "мы сделали предекодинг и уменьшили нагрузку до 64 затворов на линию")

И все в таком духе.

По сути, более 4–10 затворов на одной линии — плохая практика. Затворы ячеек DRAM, "Висящие в воздухе" и затворы транзисторов, подключенных к питаниюземле очень сильно различаются по уровню емкостной нагрузки на линию (в общем, при переходе от FO-4 к FO-64 задержку нужно увеличить в 16 раз, или уже 16 задержек FO-4 и это только на 256 линий (не 65536)). Так же следует учесть что некоторые транзисторы могут просто не поддерживать высокие емкостные нагрузки (из-за дополнительно выделяемого тепла при переходных процессах).

Поэтому я ограничился двумя транзисторами на строку для любой разрядности адреса.

Как?

Все просто: бинарное дерево с разветвлением 4 или 16, где каждый селектор включает только один селектор после себя и транслирует оставшийся адрес к нему.

Но прежде всего нам нужно преобразовать наш бинарный адрес в One-hot(унарную позиционную) кодировку.

После этого мы просто пишем дерево селекторов.

Почему это сработало?

Вместо энкодеров строк NOR и NAND мы получаем постоянный коэффициент ветвления (4 или 16) и низкую емкостную нагрузку.

Также мы получаем низкую логическую глубину в селекторе.

И в результате мы получаем возмутительно высокую скорость (сравнимую со скоростью сумматора со сквозным переносом с той же разрядностью). И низкое энергопотребление (около 40 переключений транзисторов для 16 бит)

Кроме того, мы получаем только 1–2 транзистора на строку для любой разрядности адреса (!).

Как я могу сравнить это с тем что есть?

Задержка в 13 FO-4 для 16-тибитного селектора(65536 линий), или меньше чем в ucdavis 16 FO-4 (256 линий).

Это около 20 ps на 7 nm для 16 bit (65k lanes) или около 40 ps для селектора строк и столбцов (32-битное адресное пространство). Или более 5 ГГц. Плюс переходные процессы в линиях и так далее.

В любом случае, это намного быстрее, чем селекторы NOR/NAND, и потребляет меньше энергии (переключение около 40 транзисторов; чтобы получить 1 Вт, нужно переключать около 5 миллионов транзисторов на частоте 1 ГГц на 32 nm).

Забавный пример — на хранение результата сложения может уйти больше энергии, чем на сложение. Вот почему каждый институт из топ-50 имеет свою собственную исследовательскую программу топологической сортировки и маппинга операций для FPGA). (С «выдающимися результатами, которые лучше, чем у любого ОБОРУДОВАНИЯ СЕГОДНЯ», конечно). И почти полное отсутствие арифметических блоков «AddMulJmpe» на частоте 1–2 ГГц. (За исключением MantiCore(ethz) и некоторых команд ARM, но, согласно публикациям, это скорее Волшебство (также известное как дерево шин 8 Тбит/с), чем парадигма Compute More Store Less)

Где я могу посмотреть результаты?

Как и в случае с методом глобальной оптимизации, который лучше, чем в Matlab, результаты синтеза можно посмотреть здесь.

Результаты включает в себя синтез на 130 nm, обзор характеристик для различных параметров синтеза, а так же общие сводки с результатами.

Использованные материалы

1) MantiCore - ethz

2) Изображение - https://www.elprocus.com/different-types-of-demultiplexers/

3) Синтез - OpenLane

Автор:

ValeriyPus