Доброго времени суток. В этой статье расскажу как интегрировать модули, на примере двух ультразвуковых датчиков HC-SR04 и Pmod MAXSONAR, в систему на кристалле на основе MIPSfpga. Также расскажу как написать программу для управления подключенных модулей.

Основываясь на моем примере вы сможете подключить ваши собственные модули, управлять ими при помощи программы. Создавать систему со своим набором периферии, на основе MIPSfpga.

Рубрика «fpga» - 31

Подключение периферийных модулей к MIPSfpga, на примере ультразвуковых датчиков расстояния

2016-12-03 в 14:30, admin, рубрики: fpga, mips, MIPSfpga, Verilog, Анализ и проектирование систем, программирование микроконтроллеровСобственная платформа ч0.1 Теория о процессорах

2016-12-01 в 19:13, admin, рубрики: C, compiler, cpu, fpga, Компиляторы, программирование микроконтроллеровЗдравствуй, мир! Сегодня у нас серия статьей для людей со средними знаниями о работе процессора в которой мы будем разбираться с процессорными архитектурами (у меня спелл чекер ругается на слово Архитектурами/Архитектур, надеюсь я пишу слово правильно), создавать собственную архитектуру процессора и многое другое.

Принимаются любые замечания!

Хакатон нового типа испробован в Киеве, планируется повторить этот опыт в России

2016-11-28 в 7:18, admin, рубрики: Altera, C, fpga, IoT, Quartus, SoC, Verilog, vhdl, киев, кну, ПЛИС, сенсоры, хакатон, ХакатоныВ Киевском Политехническом Институте прошел хакатон нового типа, с одновременной разработкой и программной (Си, ассемблер), и схемотехнической (Verilog) частей системы, синтезируемой для реализации в микросхемы реконфигурируемой логики (ПЛИС/FPGA). Хакатон также поддерживался одной из кафедр Киевского Национального Университета и Imagination Technologies, разработчиком графического процессора PowerVR внутри Apple iPhone. Результат хакатона превзошел ожидания (об этом ниже), и сейчас разрабатываются планы повторить его в других местах, в частности в Томске или Новосибирске.

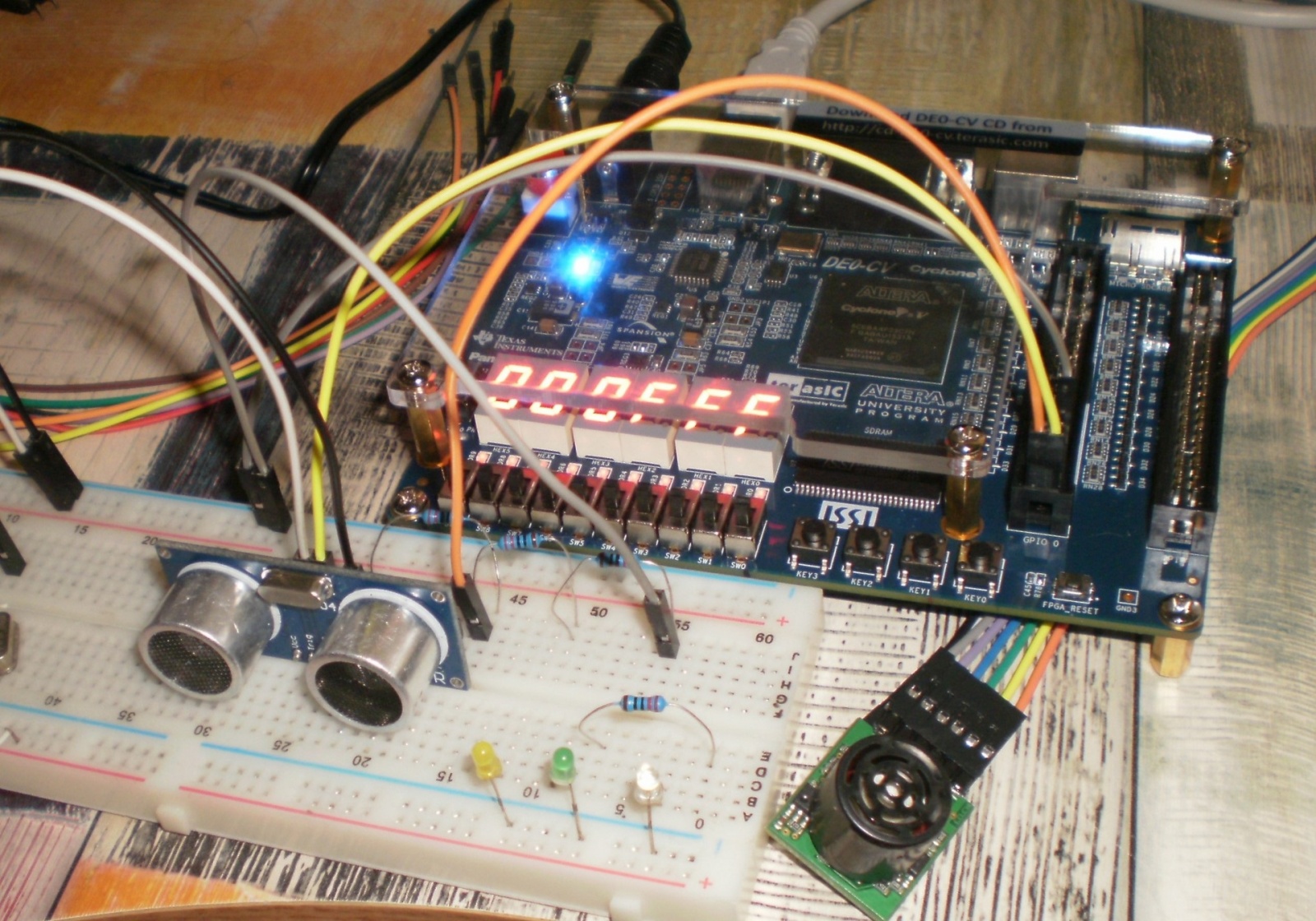

Хакатон в КПИ по MIPSfpga был экспериментальным в том смысле, что обычно в хакатонах участники или просто программируют (например решения SaaS), или делают устройства из готовых фиксированных микросхем и программируют их (Ардуино, STM32 Discovery). Здесь же участники и писали программу, и разрабатывали схему, интерфейсный блок на уровне регистровых передач (Register Transfer Level — RTL), после чего встраивали этот блок в синтезируемую систему с процессорным ядром MIPS microAptiv UP и шиной AHB-Lite, и реализовывали эту систему в FPGA.

Вот как это выглядело на экранах их ноутбуков, на FPGA-плате и концептуально:

Читать полностью »

Применение FPGA для расчета деполимеризации микротрубочки методом броуновской динамики

2016-11-21 в 13:19, admin, рубрики: fpga, gpgpu, HLS, HPC, высокая производительность, параллельное программированиеВсе готово, чтобы рассказать Хабр аудитории о применении FPGA в сфере научных высокопроизводительных вычислений. И о том, как на данной задаче надо удалось значительно обскакать GPU (Nvidia K40) не только в метрике производительность на ватт, но и просто с точки зрения скорости вычисления. В качестве FPGA платформы использовался кристалл Xilinx Virtex-7 2000t, подключенный по PCIe к хост компьютеру. Для создания аппаратного вычислительного ядра использовался язык C++ (Vivado HLS).

Под катом текст нашей оригинальной статьи. Там, как обычно бывает, сначала идет долгое описание зачем это все надо и модели, если нет желания это читать, то можно переходить сразу к реализации, а модель посмотреть потом при необходимости. С другой стороны без хотя бы беглого ознакомления с моделью читатель не сможет получить впечатление о том, какие сложные вычисления можно реализовать на FPGA )

Наконец-то приличный отечественный процессор ЦОС – 1967BH28

2016-11-11 в 9:42, admin, рубрики: 1967BH28, ADSP-TS201S, dsp, fpga, высокая производительность, процессор, цос

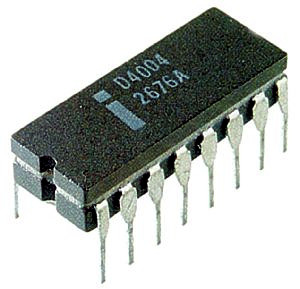

Несмотря на стремительное развитие процессоров общего назначения (ARM, x86 и более экзотических), не теряют своей актуальности специализированные процессоры цифровой обработки сигналов (ЦОС). Одним из самых популярных процессоров ЦОС с плавающей точкой в родном отечестве стал процессор ADSP-TS201S фирмы Analog Devices. В свое время (10-15 лет назад) этот процессор не знал себе равных в высокопроизводительных системах ЦОС, работающих в реальном времени. Его основные характеристики:

- Частота процессора – 600 MГц

- Объем внутренней памяти – 3 МБайта

- 4 высокоскоростных порта – 600 Мбайт/сек

- Внешняя шина – 100 МГц

- Каналы DMA – 12 каналов

Решения на процессоре ADSP-TS201S хорошо себя зарекомендовали в широком классе аппаратуры как гражданского, так и не очень гражданского назначения. Но всему хорошему приходит сами знаете что конец.

Читать полностью »

Можно скачать материалы семинара Nanometer ASIC (РОСНАНО – МИСиС – Imagination Technologies) — ликбез по всему про чипы

2016-11-10 в 9:21, admin, рубрики: fpga, imagination technologies, Nanometer ASIC, Synopsys IC Compiler, Байкал электроникс, высокая производительность, МИСиС, МИЭМ, НИИСИ, ПЛИС, программирование микроконтроллеров, Разработка для интернета вещей, РОСНАНО, элвис-неотек, метки: Nanometer ASICГоспода! Семинар Nanometer ASIC, организованный РОСНАНО, МИСиС и Imagination Technologies, оказался довольно популярным — на него зарегистрировались более 180 человек, пришли 127, причем в аудитории засветились предствители всех значимых российских микроэлектронных проектов — от радиационно-стойких микросхем для космоса из НИИСИ до чипов для умных камер от ЭЛВИС-НеоТек, инженеров из Байкал Электроникс, руководителей проектов по автоматизации проектирования микросхем из МГУ, разработчики российских ПЛИС-ов из Воронежа, преподаватели из ВШЭ/МИЭМ и других вузов, организаторов олимпиад для школьников из МФТИ и многие другие.

Несмотря на то, что для профессиональных спецов по использованию Synopsys IC Compiler семинар был слишком элементарный, но его вводный характер искупился его широтой — инженеры из всей цепочки проектирования и производства могли освежить в памяти области, которые они забыли, инвесторы в полупроводниковой индустрии смогли посмотреть что делают компании, в которые они инвестируют, студенты посмотрели, что им может нравится и так сказать куда копать (в полупроводниковой индустрии Silicon Valley молодые инженеры специализируются в логический / физический / аналоговый дизайн довольно рано в своей карьере).

Ведущий семинара, лектор Калифорнийского университета в Санта-Крус (отделение в Кремниевой долине) Чарльз Данчек (Charles Dancak) отвечает на вопросы:

Скачать все слайды на русском можно здесь.

Под катом — избранные слайды Nanometer ASIC (25 из 322):

Читать полностью »

Как искусственный интеллект меняет рынок чипов

2016-11-07 в 15:09, admin, рубрики: cpu, fpga, Google, gpu, глубокое обучение, Железо, искусственный интеллект, нейросети, Процессоры

Менее, чем за 12 часов, три разных человека предложили мне деньги за то, чтобы я час разговаривал с незнакомым человеком по телефону.

Все они сказали, что им понравилась моя статья про то, как Google создаёт новый компьютерный чип для ИИ, и все они упрашивали меня обсудить эту тему с их клиентом. Каждый описал своего клиента как менеджера большого хедж-фонда, но не назвал его имени.

Запросы пришли от так называемых экспертных сетей – исследовательских фирм, связывающих инвесторов с людьми, которые могут помочь первым понять определённые рынки и обеспечить конкурентное преимущество (иногда, судя по всему, через инсайдерскую информацию). Эти экспертные сети желали, чтобы я объяснил, как ИИ-процессор от Google повлияет на рынок чипов. Но сначала они потребовали подписать для них соглашение о неразглашении. Я отказался.

Читать полностью »

Хардвер вторгается в софтвер на московской конференции SECR

2016-11-02 в 16:02, admin, рубрики: fpga, imagination technologies, mips, rtos осрв микроконтроллеры, Анализ и проектирование систем, исп ран, нииси ран, параллельное программирование, программирование микроконтроллеров, тестирование, метки: rtos осрв микроконтроллерыТрадиционно московская конференция CEE-SECR (Central & Eastern European Software Engineering Conference in Russia) была про софтвер, но в этом году ее организаторы решили поэкспериментировать и впустить темных демонов хардвера. Причем не из чего-то народного типа Ардуино, а из уровней посуровее: микроархитектуры микропроцессоров, прототипирования систем на кристалле с помощью микросхем ПЛИС/FPGA, и автоматической генерации тестов для процессоров во время их разработки. Чтобы привязать данный материал к чему-то знакомому для программистов, в хардверной теме возникли приложения встроенных процессоров для интернета вещей, связь лицензируемых микропроцессорных ядер с российскими микропроцессорными проектами, обучение хардверу в российских университетах, а также российские встроенные операционные системы реального времени для тех применений, куда нельзя впускать длинный нос американского Госдепа.

Можно сказать, что хардверная тема на SECR-е удалась: вся комбинация докладов была сбалансированна и покрывала тему с разных сторон; людей в зале было не то что особенно много, но выше среднего; возникли интересные споры о достоинствах и недостатках открытых процессорных ядер супротив частично открытых, но шире используемых в промышленности.

Подключение АЦП к ПЛИС. Особенности, сложности, реализация

2016-10-26 в 19:49, admin, рубрики: adc, Altera, analog devices, fpga, open source, vhdl, xilinx, ацп, ПЛИС, программирование микроконтроллеров, Разработка систем передачи данных, Разработка систем связи

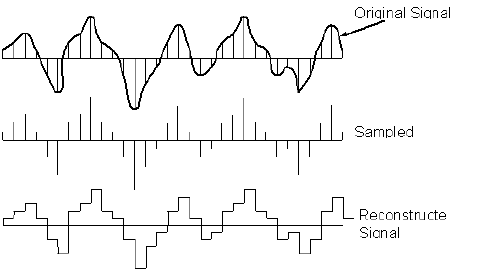

Всем привет! В данной статье речь пойдет о подключении микросхем АЦП к кристаллам ПЛИС. Будут рассмотрены основные особенности соединения узлов схем, представлены современные АЦП и их характеристики. В статье будут даны практические советы по быстрому и правильному подключению АЦП к ПЛИС с минимальными временными затратами. Кроме того, речь пойдет о принципах подключения тех или иных АЦП, будет рассмотрен входной буфер ПЛИС и его базовые компоненты – триггеры, узлы задержки IODELAY, сериализаторы ISERDES и т.д. Более детально с примерами программного кода на языке VHDL будет проведен обзор основных элементов, требуемых для качественного приёма данных от АЦП. Это входной буфер, узел упаковки данных для одноканальных и многоканальных систем, модуль синхронизации и передачи данных на базе FIFO, узел программирования АЦП по интерфейсу SPI, узел синтеза частоты данных – MMCM/PLL. Также в статье будет представлен обзор законченных устройств (в стандарте FMC) от ведущих зарубежных и отечественных производителей аналоговых и цифровых схем. В конце статьи вы найдете ссылку на исходные коды универсального узла приёмника данных от многоканальных схем АЦП. Код простой и гибкий в конфигурировании, он представлен на языке VHDL и заточен на микросхемы ПЛИС Xilinx 7 серии и выше, но может быть применен и в других кристаллах ПЛИС.

Читать полностью »