Каким образом повысить количество российских инженеров, которые были бы знакомы и с разработкой хардвера, и с разработкой софтвера, и могли бы строить системы, в которых часть функциональности находится в специализированном железе, а часть — в программном обеспечении, с соблюдением баланса между ними?

Для этого вовсе не обязательно выбрасывать несуразные деньги а-ля сделка Сколкова и MIT.

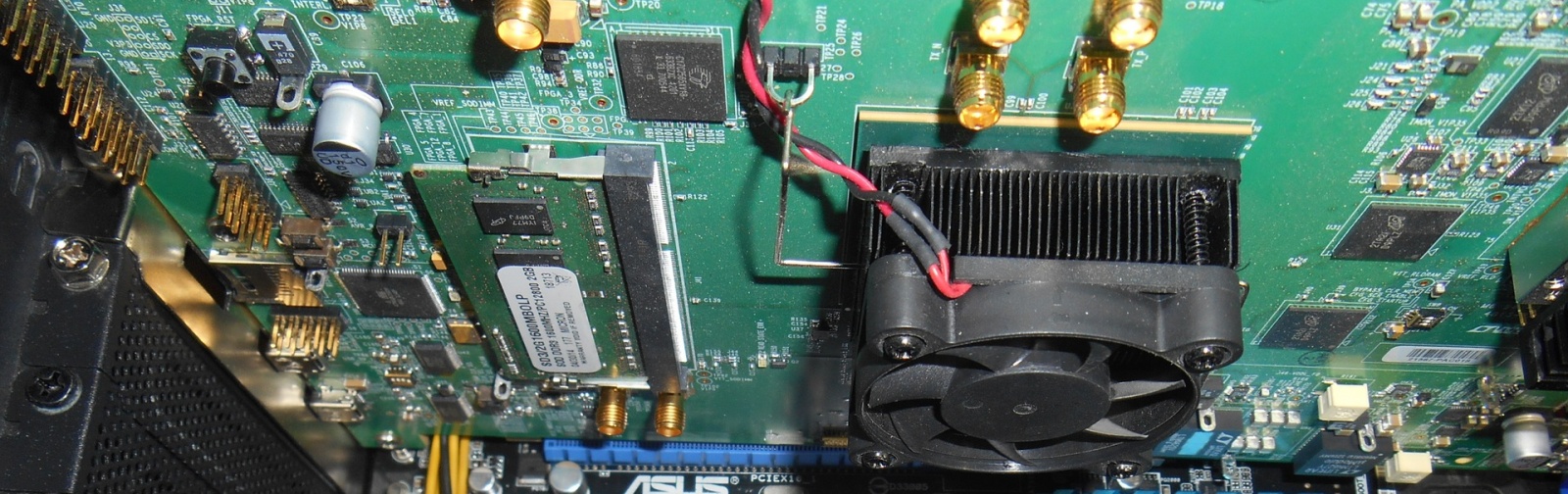

Есть масса дешевых и эффективных мер по апгрейду российской образовательной системы. Одна из них — широко ввести практические классы ПЛИС / ППВМ / FPGA среди старших школьников и студентов. Это то, на чем учатся и инженеры, которые потом разрабатывают микросхемы внутри Apple iPhone в Купертино, Калифорния.

Читать полностью »