27 марта на сайте The Wall Street Journal была анонсирована новость о возможном поглощении компанией Intel известного производителя ПЛИС (программируемые логические интегральные схемы) Altera. Планируемая сделка обещает стать самой крупной за все время существования компании. Компания Altera, может быть поглощена за рекордные для Intel $13,6 миллиарда.

27 марта на сайте The Wall Street Journal была анонсирована новость о возможном поглощении компанией Intel известного производителя ПЛИС (программируемые логические интегральные схемы) Altera. Планируемая сделка обещает стать самой крупной за все время существования компании. Компания Altera, может быть поглощена за рекордные для Intel $13,6 миллиарда.

Читать полностью »

Рубрика «Altera» - 6

Intel планирует выкупить Altera

2015-03-30 в 23:08, admin, рубрики: Altera, intel, m&a, слияния и поглощения, финансы в ITПоиск Bing оптимизировали с помощью нейросети на FPGA

2015-02-27 в 11:45, admin, рубрики: Altera, Bing, fpga, microsoft, Железо, облачные сервисы, свёрточная нейросеть, метки: FPGA

В проектировании серверной инфраструктуры для обработки поисковых запросов у каждой компании есть свои ноу-хау. Например, Microsoft в последние годы активно экспериментирует с использованием FPGA (Field-Programmable Gate Array, программируемые пользователем вентильные матрицы).

Читать полностью »

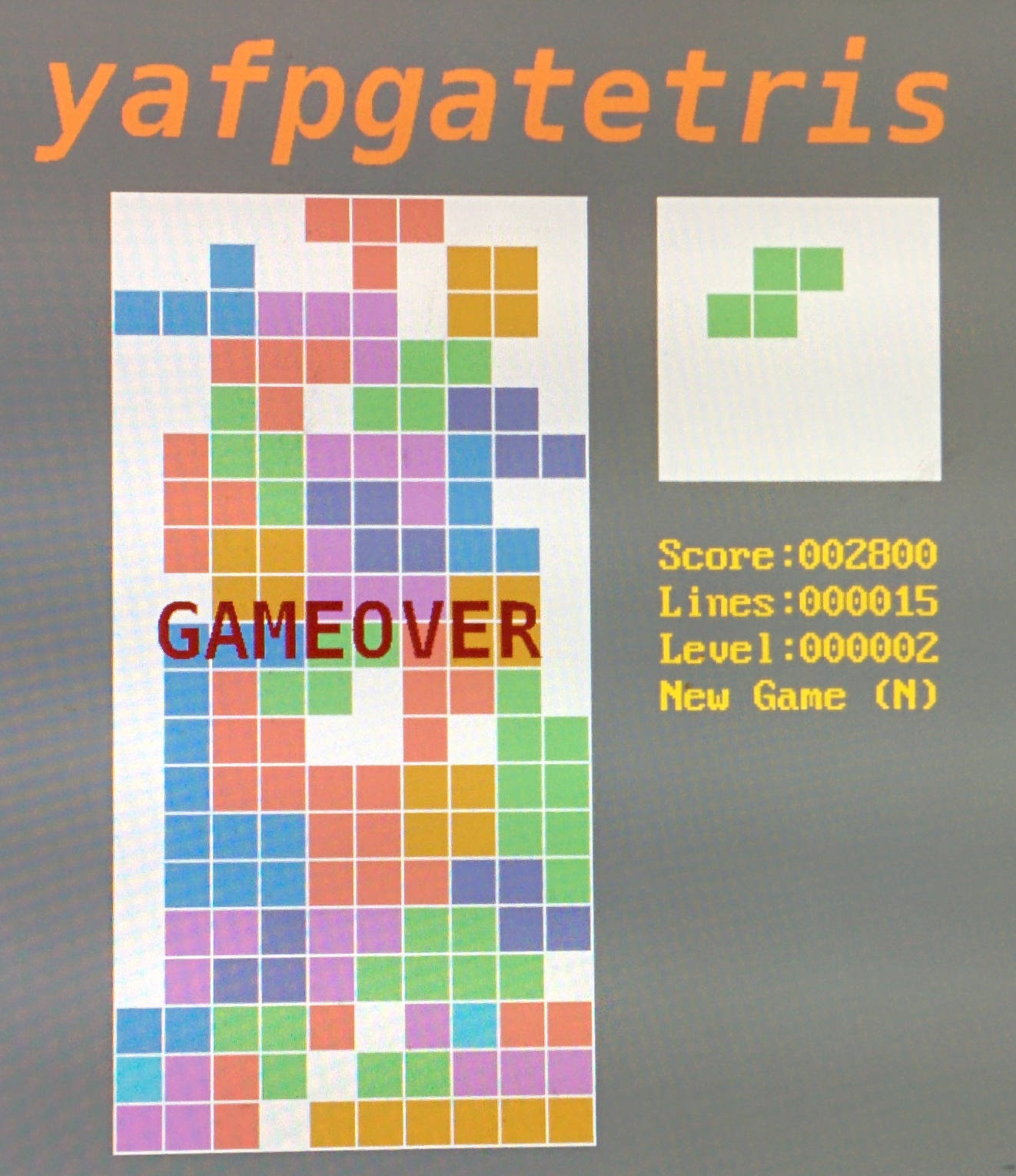

Делаем тетрис под FPGA

2015-01-11 в 14:55, admin, рубрики: Altera, de1, fpga, game development, SoC, SystemVerilog, tetris, Verilog, VGA, девкит, игры, ПЛИС, Программирование, Электроника для начинающихВсем привет!

На этих долгих новогодних выходных я задался вопросом: насколько легко написать какую-то простенькую игрушку на FPGA с выводом на дисплей и управлением с клавиатуры. Так родилась еще одна реализация тетриса на ПЛИС: yafpgatetris.

На этих долгих новогодних выходных я задался вопросом: насколько легко написать какую-то простенькую игрушку на FPGA с выводом на дисплей и управлением с клавиатуры. Так родилась еще одна реализация тетриса на ПЛИС: yafpgatetris.

Конечно, игры на FPGA делаются больше для фана и обучения, чем для каких-то реальных “продакшен” задач, да и от “разработки” игр я очень далек, можно сказать, для меня это новый опыт.

Если интересно, как можно запускать игру без операционной системы, реализуя её на самом низком уровне, с помощью триггеров и комбинационной логики, добро пожаловать под кат.

Cхема > плата > ПЛИС

2014-11-10 в 21:31, admin, рубрики: Altera, Cyclone, Expedition PCB, fpga, IO Designer, Kintex, mentor graphics, pcb, разработка, Электроника для начинающих На Хабре есть статьи для начинающих ПЛИСоводов, есть статьи с обзорами средств трассировки печатных плат. На некоторые из них я уже ссылался в своей первой статье о создании печатных плат. Во второй статье про SimBank в комментариях у меня состоялся диалог о сложности разработки ПЛИС и поддержки проектов с ней. Было высказано мнение, что легче собрать несколько простых устройств вместо одного сложного. Иногда так действительно проще. Когда речь идёт о двух, четырёх, восьми устройствах. Ряд можно продолжать с привычной вам кратностью. До преодоления порога комфорта. Два — это куча? А что делать, если есть желающие на 100 или 200 однотипных устройств?

Использовать или не использовать ПЛИС в той или другой задаче каждый решает сам (или с коллегами).

Сегодня хочу предложить вашему вниманию статью об особенностях создания печатной платы с ПЛИС. За основу возьмём инструмент «IO Designer» от компании Mentor Graphics. Кому-то может материал оказаться полезным, кому-то просто интересным, а кто-то может и не согласиться со мной.

Читать полностью »

Часы на ПЛИС (VHDL)

2014-10-29 в 13:41, admin, рубрики: Altera, Cyclone-II, vhdl, программирование микроконтроллеров, разработка, Электроника для начинающихК этому проектированию меня подтолкнула доступность на каком-то этапе обучения к отладочной плате EP2C20F484C7 фирмы «Altera» (семейство «Cyclone-II»).

В ПЛИС заложены возможности, которые позволяют превратить ее в интегральную схему с любой функцией цифровой логики. Проектирование сводится к выявлению программируемых элементов (перемычек или запоминающих ячеек), после удаления которых в структуре схемы остаются только те связи, которые необходимы для выполнения требуемых функций. На практике эта задача весьма непростая, так как современные ПЛИС содержат в среднем несколько десятков тысяч перемычек. Поэтому для проектирования обязательно применяют системы автоматизированного проектирования (САПР ПЛИС).

Читать полностью »

Ты ждал знак? Вот он!

Много лет я не решался начать программировать ПЛИС, потому что это сложно, дорого и больно (как мне казалось). Но хорошо, когда есть друзья, которые помогают сделать первый шаг. И теперь я не понимаю одного — ПОЧЕМУ Я ЖДАЛ ТАК ДОЛГО?

Сейчас я помогу сделать первый шаг и тебе!

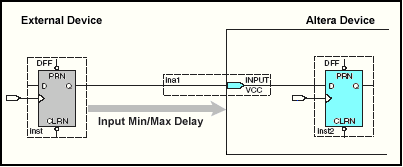

Временной анализ FPGA или как я осваивала Timequest

2014-08-07 в 12:50, admin, рубрики: Altera, fpga, Quartus II, timequest, ПЛИС, Программинг микроконтроллеровДоброго времени суток, уважаемые читатели.

На самом деле я инженер-радиофизик и программирование ПЛИС не является моей непосредственной деятельностью, но в один момент понадобилось написать программу для синхронизации нескольких осцилографических модулей. Пришлось осваивать эту науку. О том, какие у меня возникли с этим проблемы, под катом.

Dell готовится к приходу процессоров ARM в серверы (часть 3)

2014-07-15 в 4:57, admin, рубрики: Altera, dell, intel, RISC, Блог компании Dell, Железо, ПроцессорыМозаика начинает складываться

В двух предшествующих частях материала мы рассмотрели историю и проблематику вопроса. В первой части — славный путь и особенности архитектуры процессоров ARM, а во второй — современные вызовы HPC и позиционирование ARM на этом рынке. На данный момент, до выхода на рынок готовых решений от Dell, в заключительном материале цикла припомним несколько недавних новостей, в которых сейчас прослеживается четкая тенденция.

Читать полностью »

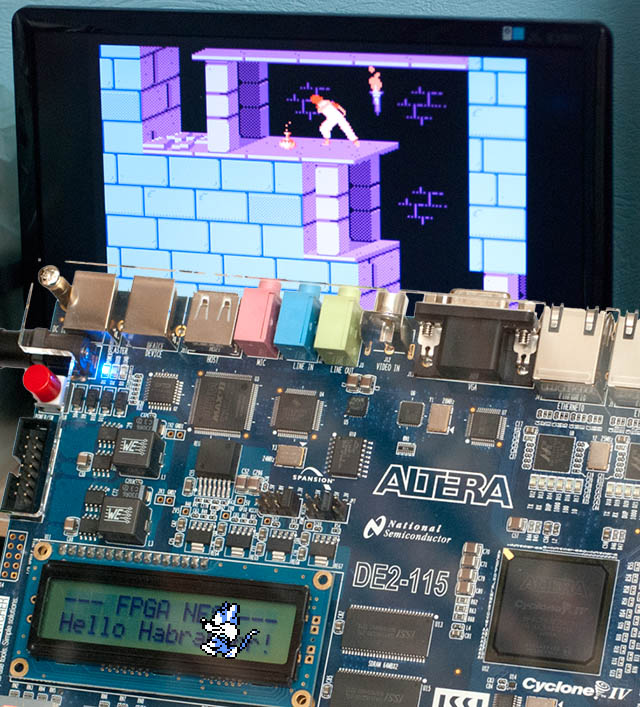

NES, реализация на FPGA

2013-07-08 в 7:58, admin, рубрики: Altera, dendy, diy или сделай сам, fpga, Nes, Verilog, денди, игровая консоль, Игровые приставки, ностальгия, ПЛИС, метки: Altera, dendy, fpga, Nes, Verilog, денди, игровая консоль, ностальгия, ПЛИСДобрый день!

Я хочу рассказать о проекте игровой консоли Nintendo Entertainment System (NES) в реализации на FPGA. На постсоветском пространстве она известна как Dendy.

Желающих посмотреть видео и поностальгировать прошу под кат.

Читать полностью »