Господа! На фотографии Ирина, девушка из Новосибирска, рассматривает музейную экспозицию про персональные компьютеры 1980-х годов. Именно тогда, в 1980-х, окончательно произошел весьма неприятный разрыв между западной электроникой и советской. Если в 1970-х советская электроника просто отставала лет на 7 (если судить по датам выхода DEC PDP-11 и СМ-4), то в районе 386-го она просто померла.

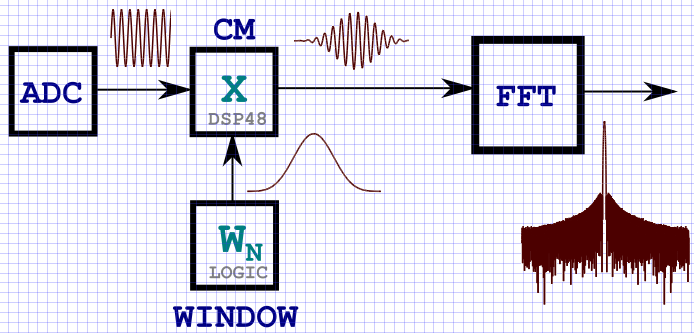

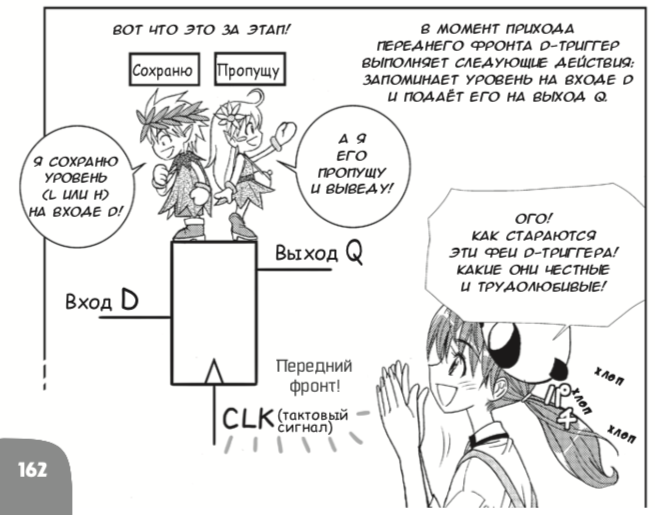

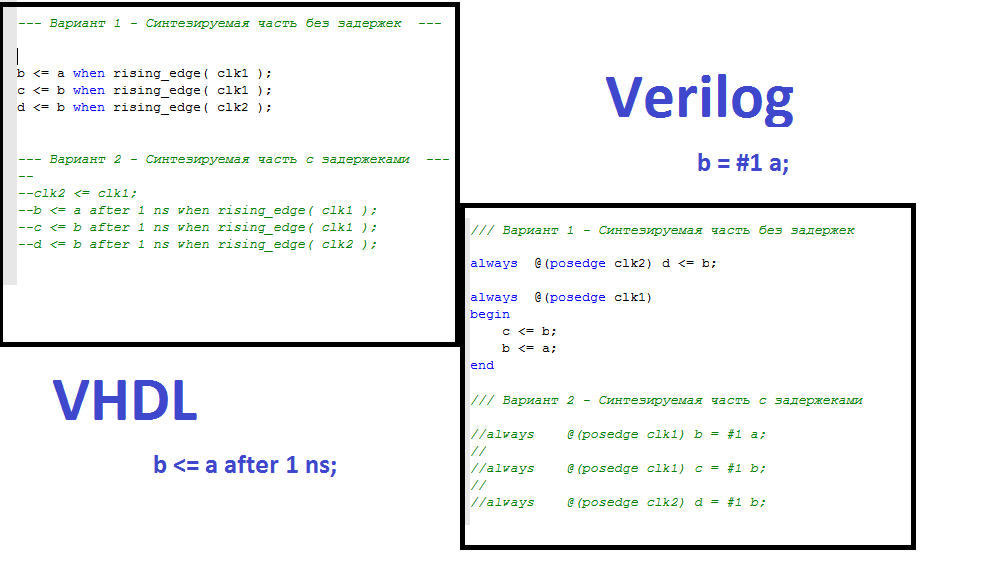

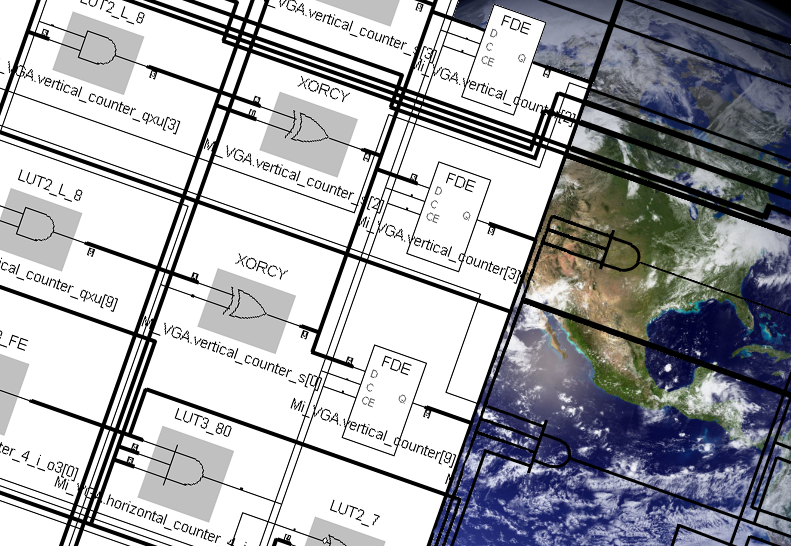

Одновременно в конце 1980-х на Западе появилась технология логического синтеза из языков описания аппаратуры Verilog и VHDL. Эта технология стала мейнстримом в 1990-х и в конечном итоге в 21 веке привела к айфонам и нейроускорителям. Логический синтез ввели во всяких MIT и Стенфордах вместе с лабами на ПЛИС-ах еще в 1990-е, но в России и Украине того времени пораженческие настроения и неверие в отечественную электронику привели к тому, что исправлять ситуацию предстоит нам сейчас.

Для того, чтобы построить в России экосистему разработки электроники, с сотнями компаний, а не дюжиной, как сейчас, нужно делать то, что делали в США в 1990-х и делают сейчас в Китае: выучить кучу молодых инженеров принципам логического проектирования цифровых схем на уровне регистровых передач. Даже если не все из них будут проектировать микропроцессоры и сетевые чипы, а половина пойдет в чистое программирование, эти знания не пропадут зря: время повышения быстродействия компьютеров за счет уменьшения транзисторов подходит к концу, и везде наступают гибридные софтверно-хардверные решения, со специализированными аппаратными вычислительными блоками — об этом недавно даже произнес речь Джон Хеннесси, председатель совета директоров компании Alphabet / Google.

Я это все говорю к тому, что она днях в Новосибирске пройдет одно из мероприятий по вытаскиванию России из неразвитого состояния в данной области.

Читать полностью »