A forwarding entity always forwards packets in per-flow order to

zero, one or more of the forwarding entity’s own transmit interfaces

and never forwards a packet to the packet’s own receive interface.

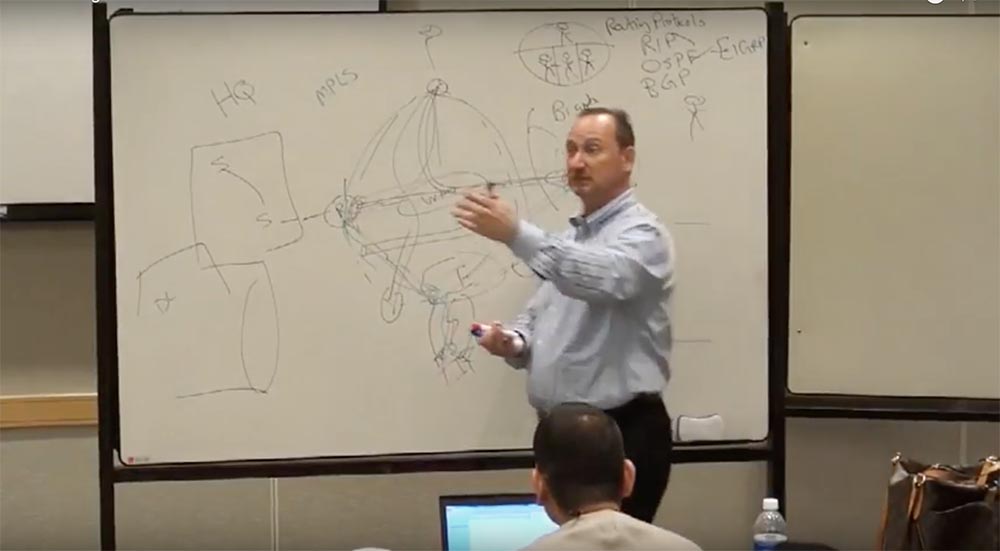

Brian Petersen. Hardware Designed Network

Одно из удивительнейших достижений современности — это то, как, сидя в Норильске, человек может чатиться со своим другом в Таиланде, параллельно покупать билет на вечерний самолёт к нему, расплачиваясь банковской картой, в то время, как где-то в Штатах на виртуалочке его бот совершает сделки на бирже со скоростью, с которой его сын переключает вкладки, когда отец входит в комнату.

А через 10 минут он закажет такси через приложение на телефоне, и ему не придётся даже брать с собой в дорогу наличку.

В аэропорту он купит кофе, расплатившись часами, сделает видеозвонок дочери в Берлин, а потом запустит кинцо онлайн, чтобы скоротать час до посадки.

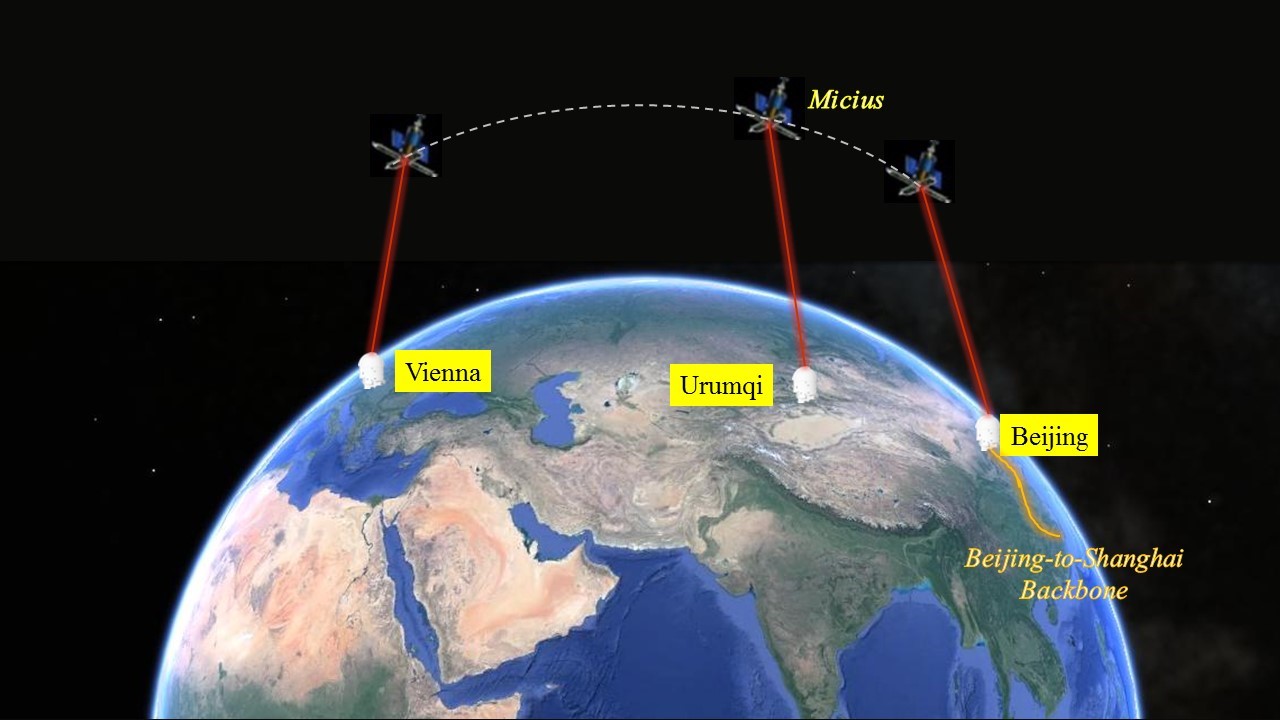

За это время тысячи MPLS-меток будут навешаны и сняты, миллионы обращений к различным таблицам произойдут, базовые станции сотовых сетей передадут гигабайты данных, миллиарды пакетов больших и малых в виде электронов и фотонов со скоростью света понесутся в ЦОДы по всему миру.

Это ли не электрическая магия?

В своём вояже к QoS, теме обещанной многократно, мы сделаем ещё один съезд. На этот раз обратимся к жизни пакета в оборудовании связи. Вскроем этот синий ящик и распотрошим его.

Кликабельно и увеличабельно.

Сегодня:

- Коротко о судьбе и пути пакета

- Плоскости (они же плейны): Forwarding/Data, Control, Management

- Кто как и зачем обрабатывает трафик

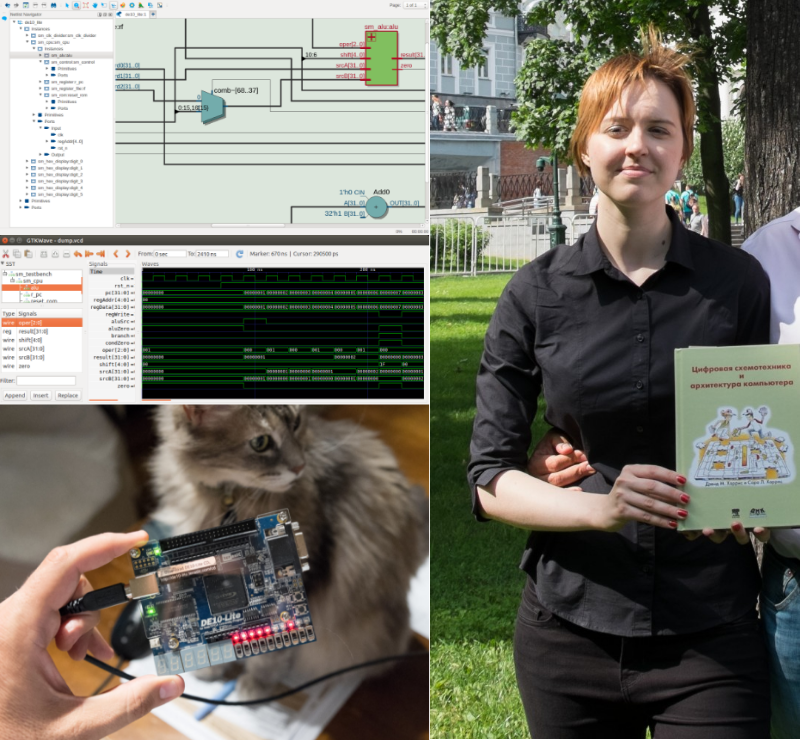

- Типы чипов: от CPU до ASIC'ов

- Аппаратная архитектура сетевого устройства

- Путешествие длиною в жизнь

Читать полностью »