Для встраиваемых систем на базе процессоров с архитектурами MIPS и ARM нередко используются специализированные генераторы дистрибутивов ОС GNU/Linux: buildroot, openwrt и прочие Yocto.

Но иногда интересно запустить на такой системе универсальную ОС Debian. Установить Debian на ЭВМ с процессором архитектуры x86/amd64 — дело несложное, а вот со встраиваемыми системами, поверьте, у нас не всё так однозначно...

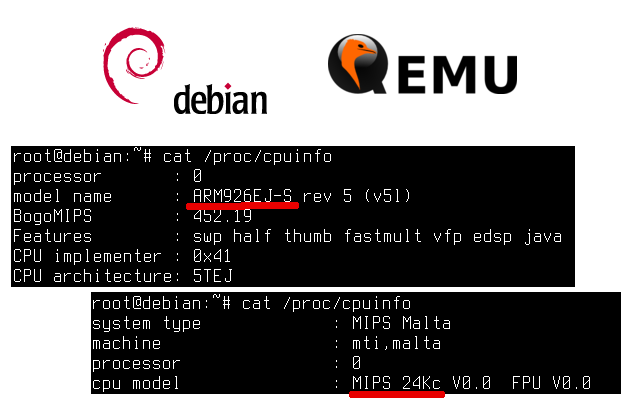

В данной публикации я расскажу как можно при помощи debootstrap установить, а затем как при помощи QEMU запустить ОС Debian для ЭВМ с процессорами MIPS и ARM.

Читать полностью »

Рубрика «mips» - 6

RISC’овый Debian под QEMU

2016-02-29 в 10:18, admin, рубрики: Debian, linux, mips, qemu, Настройка Linux, Разработка под LinuxПлаты для разработчиков и терминал на основе российского микропроцессора Байкал-Т

2016-02-26 в 9:09, admin, рубрики: Baikal Electronics, baikal-t, cnc machining, CoreMark, cpu, electronic engineering times, imagination technologies, mips, MIPS P5600, multicore, superscalar processors, Synopsys, t-platforms, tavolga, terminal, thin client, TSMC, xilinx, Анализ и проектирование систем, виртуализация, параллельное программирование, Программирование, Промышленное программированиеЗа последние три дня вышло несколько новостей про российский процессор Байкал-Т:

1. Российская компания «Т-Платформы» представила процессорный модуль SF-BT1 с Байкалом-Т, который она собирается распостранять среди разработчиков.

2. Также «Т-Платформы» выпустили на основе Байкала-Т тонкий клиент «Таволга терминал», который может работать не только как терминал, но и как автономной компьютер с Linux Debian 8.

3. Т-Платформы показывали и плату для разрабочиков, и терминал на основе Байкала-Т на выставке Embedded World в Нюренберге, в сотрудничестве с британской компанией Imagination Technologies, которая разработала микропроцессорное ядро MIPS P5600, которое использует Байкал-Т.

Я не буду пересказывать все статьи про Байкал-Т, Т-Платформы и Таволгу. Те разрабочики, кто этим интересуется, могут сами сходить по ссылкам и посмотреть параметры плат. Я добавлю некоего информационного гарнира про процессор, его экосистему и историю.

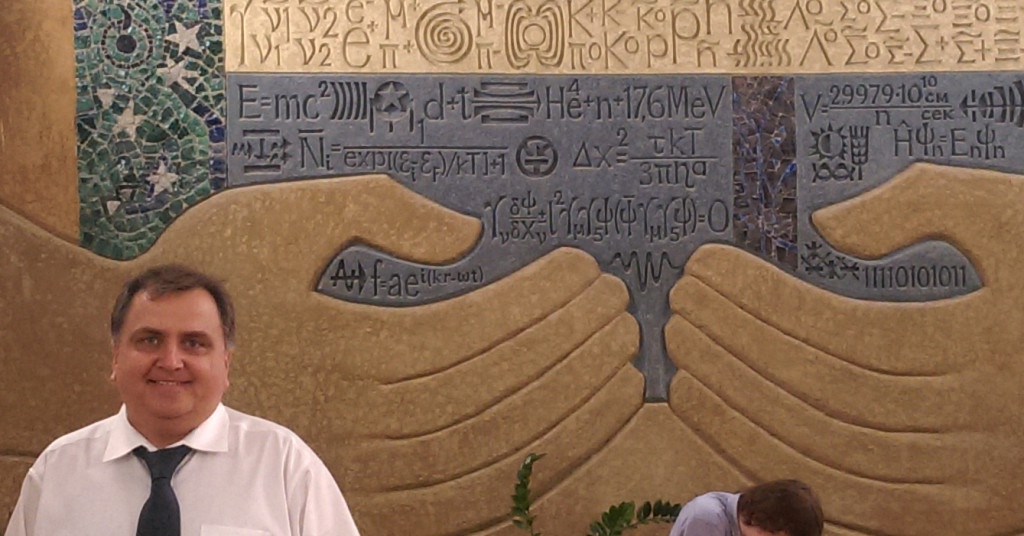

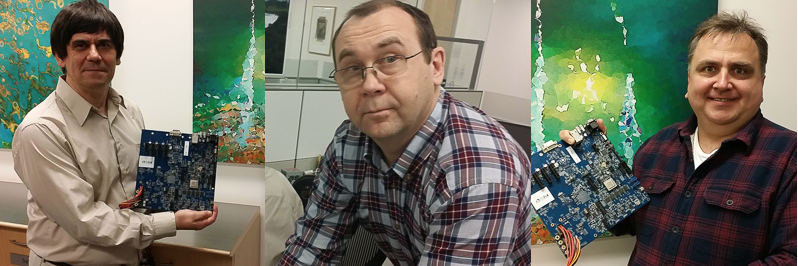

На фотографии ниже — ранние пользователи байкаловских плат. Это инженеры из России, Украины и Казахстана, которые участвуют в разработке микропроцессорного ядра MIPS P5600 и его сотфтверной экосистеме в отделении Imagination Technologies в Санта-Клара, Калифорния: Леонид Егошин (поддержка многоядерности в ядре Линукса), Сергей Вакуленко (симулятор для верификации) и Юрий Панчул (модели интерфейсов шин):

Вообще Байкал-Т — это плод международного сотрудничества, в которон вовлечены в частности:

Читать полностью »

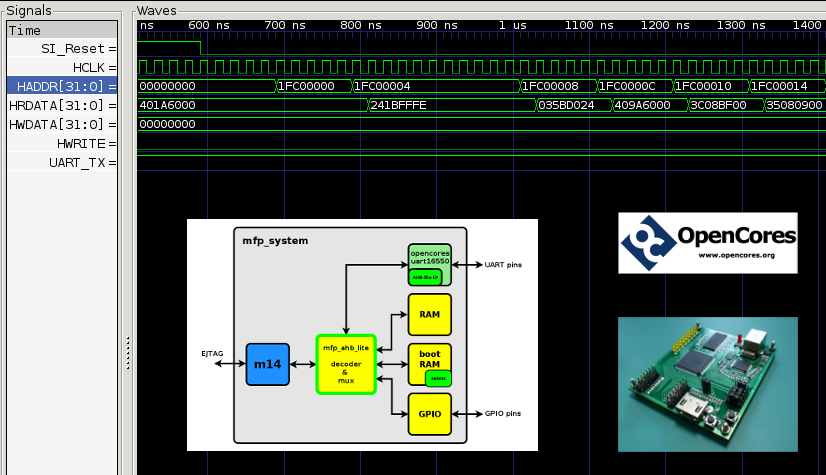

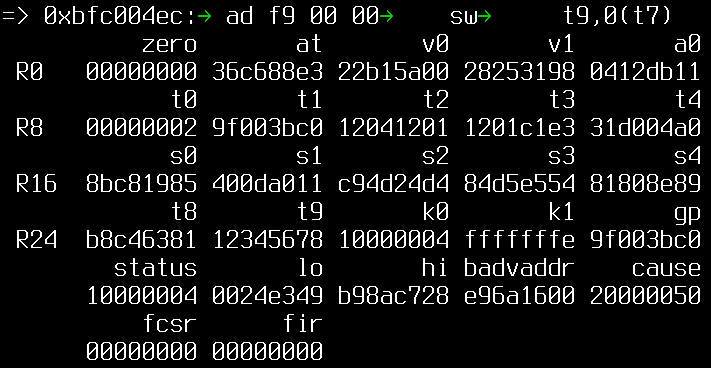

Добавляем инструкции в микропроцессор MIPS, которые работают в конвейере как его собственные

2016-02-08 в 8:37, admin, рубрики: CorExtend, fpga, mips, mips assembler, MIPS microAptiv UP, MIPSfpga, RTL, UDI, Verilog, Анализ и проектирование систем, программирование микроконтроллеровМожно ли добавить в микропроцессор инструкции (команды)? Если вы используете микросхемы ПЛИС / FPGA с реконфигурируемой логикой и микропроцессорное ядро, которые синтезирутся из описания на языках Verilog и VHDL, то можете. Причем это будет «честное», настоящее расширение системы команд, а не трюк типа программной эмуляции инструкции в обработчике исключения от зарезервированной команды, и не «микрокод», популярный в исторических процессорах 1970-х годов. Команды, добавленные в современный синтезируемый процессор с помощью модификации его исходников на Verilog или VHDL, могут работать в конвейере и обрабатываться процессором как его собственные, без временных задержек.

Главная проблема с модификацией исходников дизайна процессора на Verilog или VHDL — трудоемкость. Нужно понять, как работает логика различных блоков и избежать нежелательных побочных эффектов. К счастью, существует способ расширения процессора, который превращает семестровый студенческий проект в нечто, что студент может спроектировать за одну лабораторную работу. Этот способ — интерфейс CorExtend / UDI (User Defined Instructions) в микропроцессорном ядре MIPS microAptiv UP, которое используется в пакете для образования MIPSfpga.

В рамках университетской программы MIPSfpga компании Imagination Technologies можно скачать настоящий индустриальный код на Verilog процессора MIPS microAptiv UP.

https://community.imgtec.com/university/resources/

Одним из распространенных применений UDI является манипуляции битами в алгоритмах шифрования. Другой пример — создание специальных инструкций для ускорения алгоритмов ЦОС Accelerating DSP Filter Loops with MIPS® CorExtend® Instructions.

Однако в наборе документации к MIPSfpga интерфейс между ядром и CorExtend описан недостаточно подробно. Подробная документация предоставляется только лицензиатам ядер. В этой статье представлено мое описание данного интерфейса на основе изучения исходного кода. Его можно также скачать в формате pdf MIPS microAptiv UP Processor CorExtend UDI interface protocol guide.

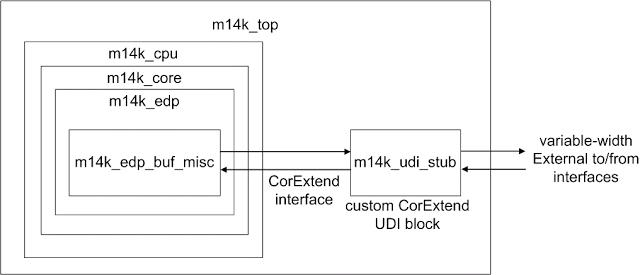

CorExtend занимает следующее место в RTL иерархии ядра m14k microAptiv.

Как начать работать с MIPSfpga

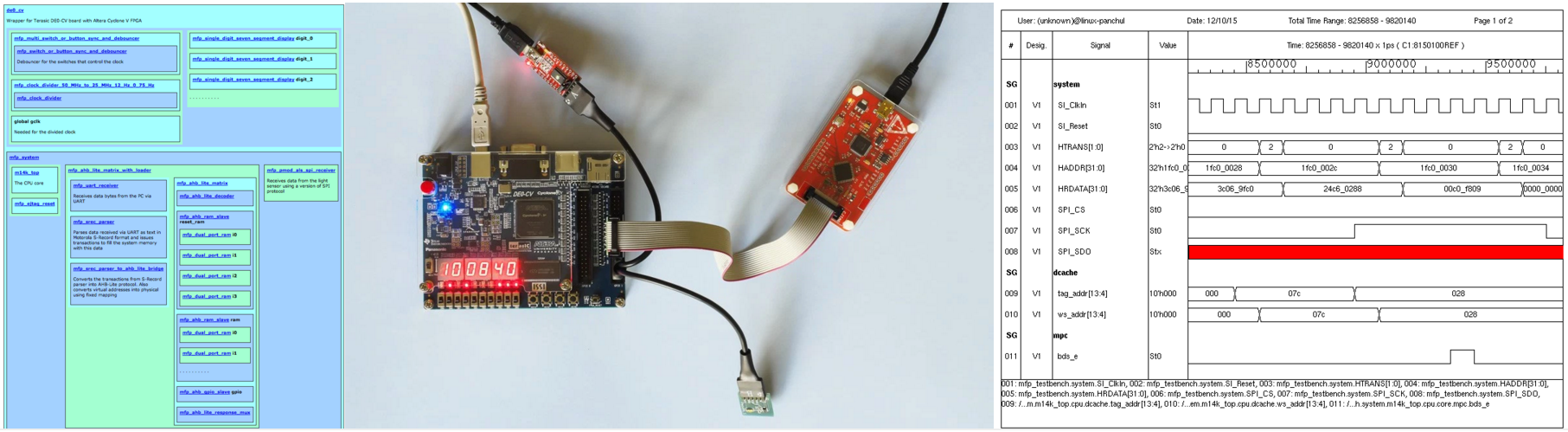

2016-01-16 в 5:59, admin, рубрики: Altera, fpga, imagination technologies, mips, MIPS microAptiv UP, MIPSfpga, SPI, uart, Verilog, vhdl, xilinx, Анализ и проектирование систем, параллельное программирование, ПЛИС, программирование микроконтроллеров, метки: плисMIPSfpga — это пакет, который содержит процессорное ядро в исходниках на Verilog, которое можно менять, добавлять новые инструкции, строить многопроцессорные системы, менять одновременно софтвер и хардвер, симулировать на симуляторе верилога, синтезировать для ПЛИС/FPGA и т.д. Его можно в целях эксперимента например запускать с частотой 1 такт в секунду и выводить наружу информацию о состоянии кэша, конвейера, и любых структур внутри процессора. При этом ядро MIPS microAptiv UP внутри MIPSfpga — это то же ядро которое например используется в платформе IoT Samsung Artik 1 и Microchip PIC32MZ, т.е. студенты получают возможность работать с тем же кодом, с которым работают инженеры в Samsung и Microchip.

MIPSfpga не предназначен для введения в предмет с абсолютного нуля. Для его плодотворного использования нужно чтобы студент или исследователь уже знал основы цифровой схемотехники, умел бы программировать на Си и на ассемблере, а также представлял бы концепции микроархитектуры — конвейера, конфликтов конвейера и т.д. Желательно, чтобы до работы с MIPSfpga студент уже бы построил собственный простой процессор с нуля и мог бы сравнивать свой простой процессор с процессором, используемым в промышленности и совместимым с развитой экосистемой разработки.

Путешествие по микроэлектронной России (академическая часть)

2015-12-19 в 17:48, admin, рубрики: fpga, imagination technologies, Microchip Technology, mips, MIPSfpga, ГУАП, Железо, итмо, ЛЭТИ, мгу, МИСиС, МИФИ, МИЭТ, МФТИ, МЭИ, Научно-популярное, Разработка для интернета вещей, робототехника, СГАУ, сколково, Сколтех, метки: Imagination Technologies, Microchip TechnologyТри недели на просторах бескрайней, с посещениями МГУ, МФТИ, МИФИ, зеленоградского МИЭТ, питерского ИТМО, самарского СГАУ, сколковского Сколкова и зеленогорского Microchip Masters Russia. В историческом для российской микроэлектроники 2015 году, когда появились спроектированные в России чипы на 28 nm, с гигагерцовыми частотами и суперскалярными процессорными ядрами на борту, когда зеленоградские команды начали интегрировать на одном чипе разработанные в России блоки видеообработки с блоками, разработанными в Калифорнии и Великобритании в совместных международных проектах, с теми же компаниями, с которыми сотрудничает Apple (Synopsys, Imagination Technologies, Cadence, ARM и другими).

Путешествие началось c парти на софтверной конференции SECR — Central & Eastern European Software Engineering Conference in Russia, на которое меня пригласил мой старый приятель Максим Цепков. Я обсудил c товарищами вопросы поддержки российских микропроцессорных проектов типа Байкала-Т со стороны российского софтверного сообщества. Конференция проходила в Digital October, популярном московском месте для организаций мероприятий такого рода:

Отчет о посещении кружка по изучению основ цифровой схемотехники в Музее Космонавтики в Москве

2015-12-14 в 8:36, admin, рубрики: arduino, JAXA, mips, Железо, космонавтика, микросхемы малой степени интеграции, музей космонавтики, НПЦ Элвис, образование, Электроника для начинающих Когда я был маленьким мальчиком, моей любимой книгой была «Земля и Небо». Она до сих пор стоит у меня на полке:

Потом я в 1 классе поехал в Москву, пошел на ВДНХ в павильон «Космос», и с большим интересом познакомился там с луноходом. И вот недавно, 38 лет спустя, я повторил знакомство:

Читать полностью »

Фотографии, материалы и перипетии семинара MIPSfpga в МИФИ

2015-11-25 в 8:23, admin, рубрики: Altera, BusBlaster, fpga, imagination technologies, mips, MIPS microAptiv UP, MIPSfpga, openocd, Semiconductor IP, Terasic, uart, xilinx, МИФИ, НИИСИ, ПЛИС, программирование микроконтроллеров, Производство и разработка электроники, Процессоры, Электроника для начинающихВ конце октября в МИФИ состоялся семинар по MIPSfpga — один из серии семинаров, организованных российскими вузами совместно с Imagination Technologies, Microchip Technology в партнерстве с Гамма Санкт-Петербург, представителями Xilinx в России компанией Макро Групп, с участием докладчиков из MathWorks и НИИСИ. Ниже — смесь из фотографий, ссылок на материалы, заметок о подготовке семинара и о мифишной культуре.

Ниже фотография МИФИ снаружи. Слово «ядерный» напоминает, что в МИФИ стоит ядерный реактор, поэтому туда трудно попасть, особенно с американским паспортом — пропуск мне готовили недели две, а приказ о семинаре подписывал ректор. На входе стоит автоматчик с Калашниковым (!)

Читать полностью »

MIPSfpga: вне канона

2015-11-12 в 13:26, admin, рубрики: AHB-Lite, Altera, Cyclone, fpga, MAX10, mips, MIPSfpga, nmon, opencores, openocd, Quartus, Terasic, uart, Wishbone, Железо, платы Марсоход, Производство и разработка электроники, Процессоры, Электроника для начинающих

В течении последних трёх недель в МИЭТ, МГУ, МИФИ, МФТИ и других российских ВУЗах прошли семинары по процессору на ПЛИС MIPSfpga. В рамках семинаров прошли лабораторные работы на которых демонстрировалось как применять MIPSfpga на практике.

В публикации я расскажу о своих экспериментах с MIPSfpga, которые выходят за рамки лабораторных работ, рассмотрю возможности интеграции процессорного ядра MIPSfpga с IP-блоками opencores.org. Также поведаю о портировании MIPSfpga на некоторые платы на базе ПЛИС Altera (приведены значения Fmax и показатели использования ресурсов ПЛИС).

Читать полностью »

Провели семинар по процессору на ПЛИС MIPSfpga в МИЭТ

2015-10-27 в 4:53, admin, рубрики: fpga, imagination technologies, mips, MIPSfpga, xilinx, Железо, зеленоград, МИЭТ, ПЛИС, Производство и разработка электроники, Процессоры, Электроника для начинающих, метки: MIPSfpga, XilinxПровели семинар по процессору на ПЛИС MIPSfpga в Национальном исследовательском университете «Московский институт электронной техники». Получилось хорошо, уровень слушателей довольно высокий. Помимо меня, докладчика от Imagination Technologies, был докладчик из Макро Групп и MathWorks. Александр Филиппов из Макро Групп, официального представителя Xilinx в России, рассказал о Artix-7, Kintex-7 и UltraScale FPGA. Михаил Песельник, докладчик от MathWorks, рассказал о модели single-cycle реализации подмножества архитектуры MIPS в среде Simulink. Забыл попросить кого-нибудь меня сфотографировать, но остальные докладчики на фото ниже. Сегодня будет такой же семинар в МГУ, завтра в МИФИ.

Презентации использовавшиеся во время доклады от Imagination: panchul.com/dropbox/2014_10_26/presentations

Основной код для лабораторных работ: github.com/MIPSfpga/mipsfpga-plus

EJTAG: аттракцион для хакеров-2

2015-08-30 в 0:35, admin, рубрики: AR9331, Black Swift, DDR, diy или сделай сам, EJTAG, gdb, mips, openocd, PLL, trace, u-boot, Железо, Процессоры, Софт

В моих предыдущих публикациях EJTAG: аттракцион для хакеров и Black Swift: использование EJTAG рассматривался самый простой сценарий применения EJTAG — загрузка в ОЗУ и запуск на исполнение программы пользователя. Однако, возможности EJTAG этим не ограничиваются. В публикации рассказывается как организовать несложную отладку кода при помощи EJTAG, используя свободно-распространяемые программные средства openocd и GDB.

Читать полностью »